# HIGH-EFFICIENCY SYNCHRONOUS BUCK PWM CONTROLLER

#### **FEATURES**

- On-Chip Predictive Gate Drive<sup>™</sup> for High-Efficiency Synchronous Buck Operation

- Dual ±3-A TrueDrive<sup>™</sup> Outputs

- On-Board Programmable Oscillator with 1-MHz Frequency Operation

- TR Input for Sequencing Operation

- Overcurrent Protection using a Parallel Average Current Mode Control Loop

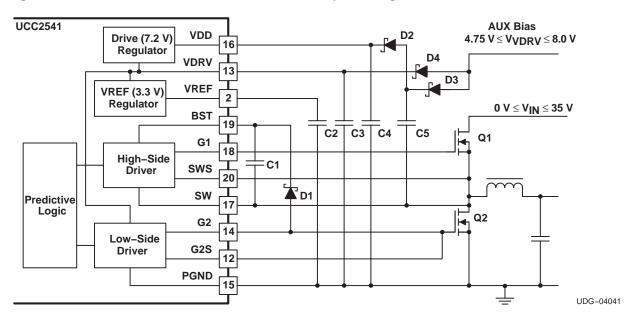

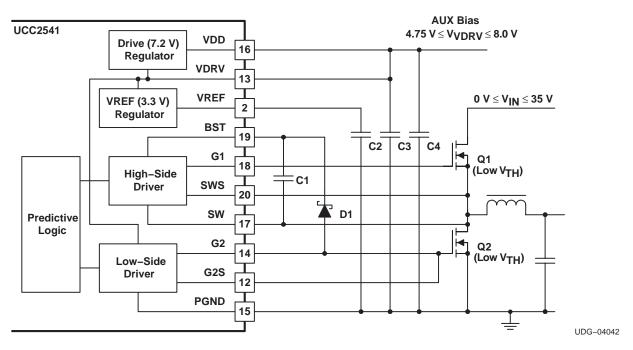

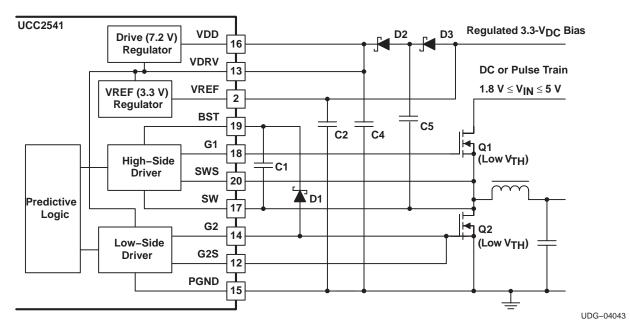

- 3 Modes to Support 2.7-V to 35-V Input Bias

- Reverse Current Protection for Output Stage

- User Programmable Shutdown Using SS Pin

- ±1.0% Initial Tolerance Bandgap Reference

- High Bandwidth Error Amplifiers

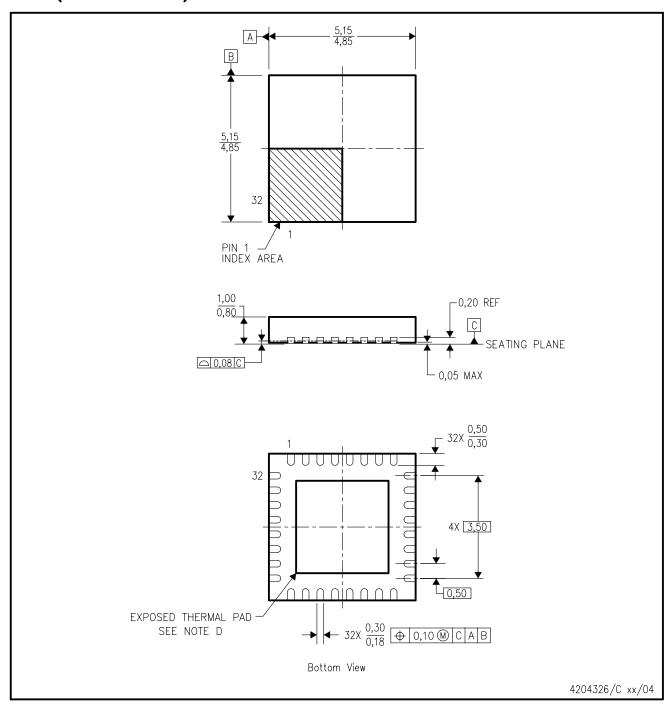

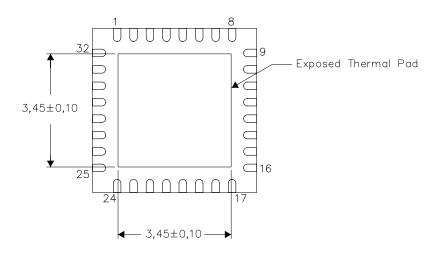

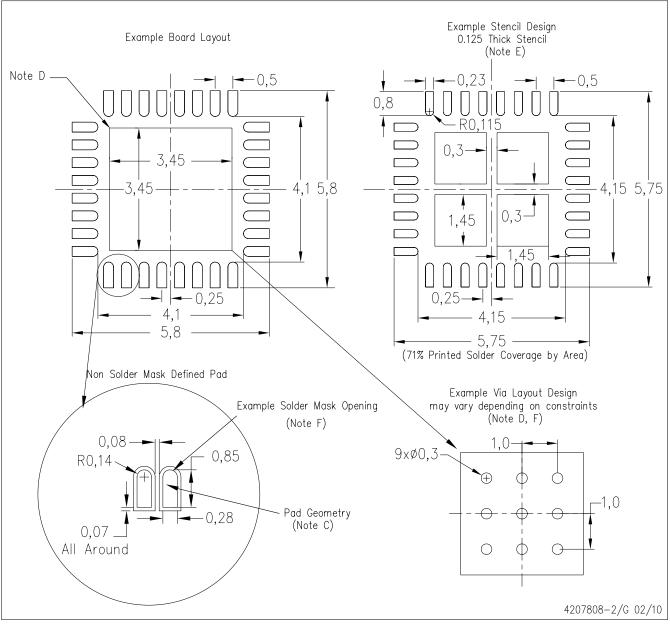

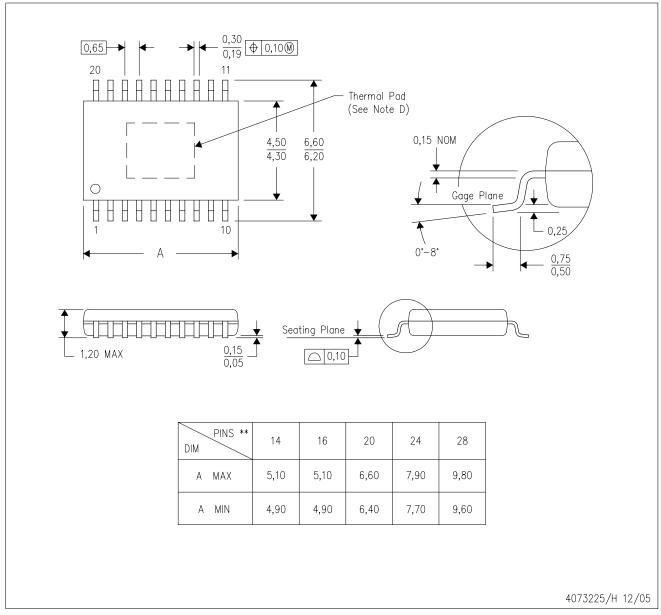

- Thermally Enhanced HTSSOP 20-Pin PowerPAD™ Package and QFN-32 Pin

- Synchronization Input

- Supports Pre-Bias Applications

#### **APPLICATIONS**

- High Efficiency Non-Isolated Converters Requiring Advanced Features such as Pre-Bias Support and Tracking Capability

- Point-of-Load Modules for Servers, Telecom, and Data communication Equipments

- Good for Input Voltages of 3.3 V, 5.0 V, 12.0 V, or Intermediate Bus Voltages

#### **DESCRIPTION**

The UCC2541 is a synchronous buck PWM controller for high current and low output voltage applications.

For higher efficiency, it incorporates the Predictive Gate Drive™ technology that virtually eliminates body diode conduction losses in synchronous rectifiers.

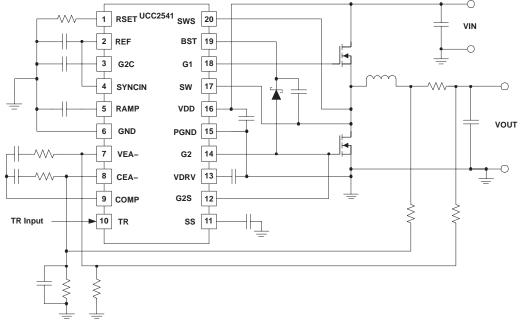

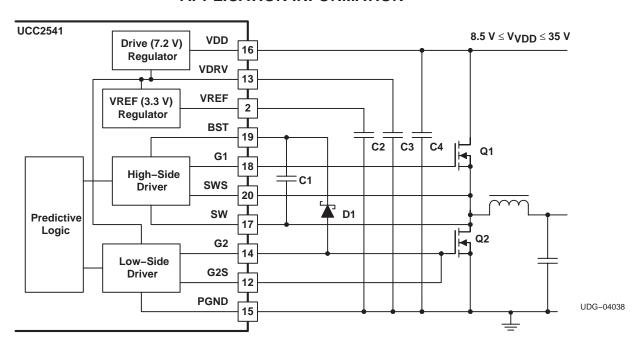

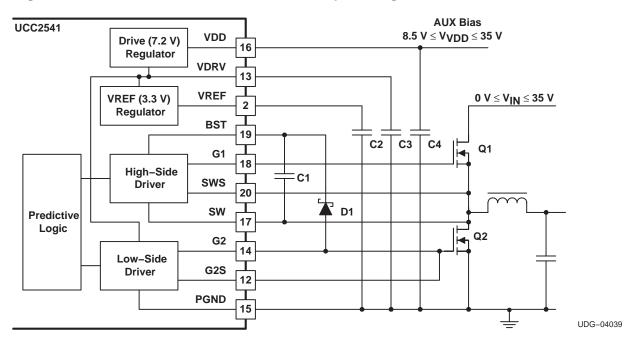

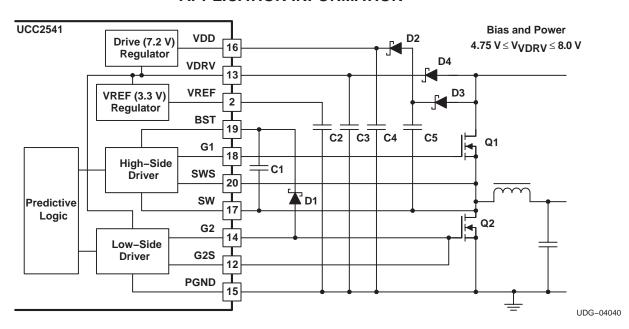

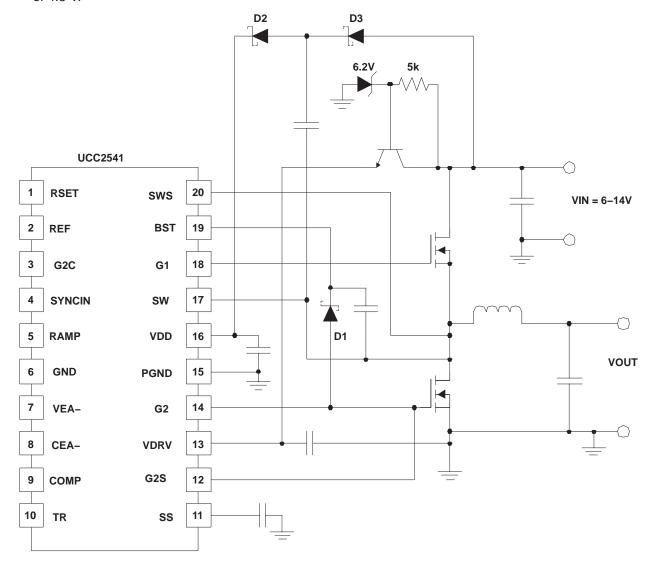

# SIMPLIFIED APPLICATION DIAGRAM

Predictive Gate Drive™, TrueDrive™ and PowerPAD™ are trademarks of Texas Instruments Incorporated.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **DESCRIPTION (CONT.)**

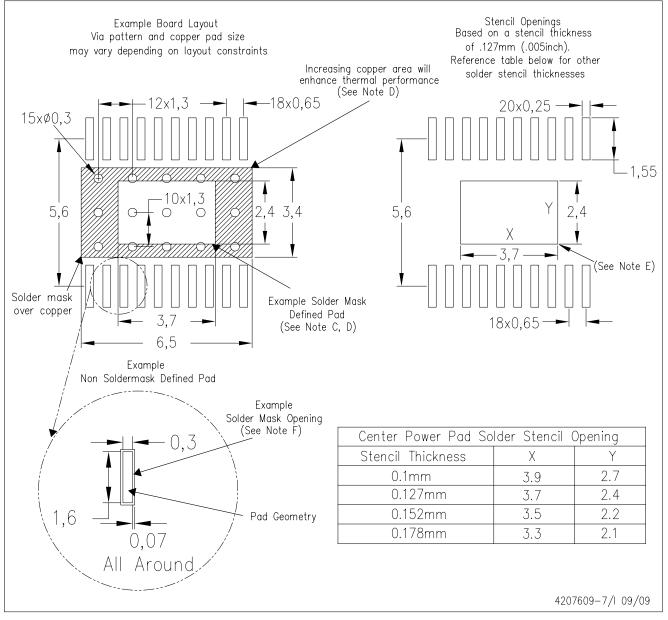

The UCC2541 is available in the extended temperature range of  $-40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$  and is offered in thermally enhanced PowerPAD  $^{\text{TM}}$  20-pin HTSSOP (PWP) or 32-pin quad flatpack (RHB) package. This space saving package with standard 20-pin TSSOP footprint has a drastically lower thermal resistance of  $1.4^{\circ}\text{C/W}$   $\theta_{\text{JC}}$  to accommodate the dual high-current drivers on board.

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)(1)(2)

|                                               |                                     | UCC2541        | UNIT |  |

|-----------------------------------------------|-------------------------------------|----------------|------|--|

| Supply voltage range, VDD                     |                                     | 36             | V    |  |

| Supply current, I <sub>VDD</sub>              | VDD                                 | 50             | mA   |  |

|                                               | CEA-, COMP, G2C, RAMP, SS, TR, VEA- | -0.3 to 3.6    |      |  |

|                                               | VDRV                                | -0.3 to 9      |      |  |

| Analan Sanut waltanaa                         | G1, BST                             | SW-0.3 to SW+9 | .,   |  |

| Analog input voltages                         | SW, SWS                             | -1 to 36       | V    |  |

|                                               | G2, G2S                             | –1 to 9        |      |  |

|                                               | SYNCIN                              | -0.3 to 8.0    |      |  |

| Sink current (peak), IOUT_SINK                | G1, G2                              | 3.5            |      |  |

| Source current (peak), IOUT_SOURCE            | G1, G2                              | -3.5           | Α    |  |

| Operating junction temperature range, TJ      | -55 to 150                          |                |      |  |

| Storage temperature, T <sub>Stg</sub>         | -65 to 150                          | °C             |      |  |

| Lead temperature 1,6 mm (1/16 inch) from case | 300                                 |                |      |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                 |        | MIN     | TYP | MAX  | UNIT |

|-------------------------------------------------|--------|---------|-----|------|------|

| Supply voltage, VDD                             | Mode 1 | 8.5     |     | 35   |      |

| Supply voltage, VDRV                            | Mode 2 | 4.75    |     | 9.00 | V    |

| Supply voltage, REF                             | Mode 3 | 3.0     | 3.3 | 3.6  |      |

| Supply voltage bypass, CVDD                     |        | 1.0     | 2.2 |      |      |

| Reference bypass capacitor, CREF                |        | 0.1     | 1.0 | 2.2  | _    |

| VDRV bypass capacitor, C <sub>VDRV</sub>        |        | 0.2     |     |      | μF   |

| BST-SW bypass capacitor, CBST-SW                |        | 0.1     |     |      |      |

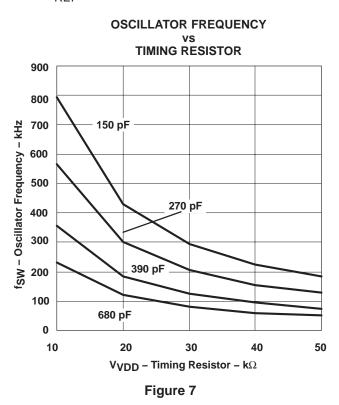

| Timer current resistor range, R <sub>RSET</sub> |        | 10      |     | 50   | kΩ   |

| PWM ramp capacitor range, CRAMP                 |        | 100     |     | 680  | _    |

| Turn-off capacitor range, C <sub>G2C</sub>      |        | 120     |     | 1000 | pF   |

| COMP pin load range, R <sub>LOAD</sub>          |        | <br>6.5 |     |      | kΩ   |

| Junction operating temperature, TJ              |        | <br>-40 |     | 105  | °C   |

<sup>(2)</sup> All voltages are with respect to GND. Currents are positive into, and negative out of the specified terminal.

#### ORDERING INFORMATION

| т. т.                           | HTSSOP-20 (PWP) <sup>(1)</sup> | QFN-32 (RHB) <sup>(1)</sup> |

|---------------------------------|--------------------------------|-----------------------------|

| T <sub>A</sub> = T <sub>J</sub> | Bulk                           | Bulk                        |

| -40°C to +105°C                 | UCC2541PWP                     | UCC2541RHB                  |

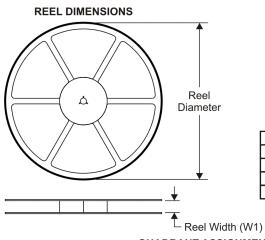

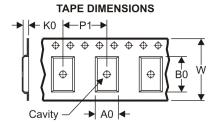

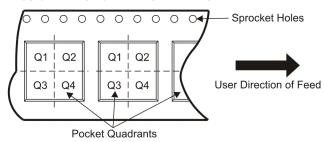

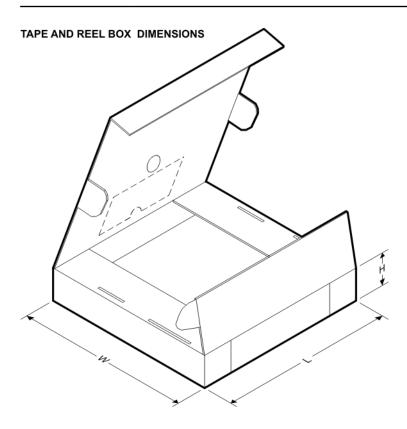

<sup>(1)</sup> The PWP and RHB packages are also available at 73 devices per tube and taped and reeled at 3,000 devices per reel. Add an R suffix to the device type (i.e., UCC2541PWPR). See the application section of the data sheet for PowerPAD drawing and layout information.

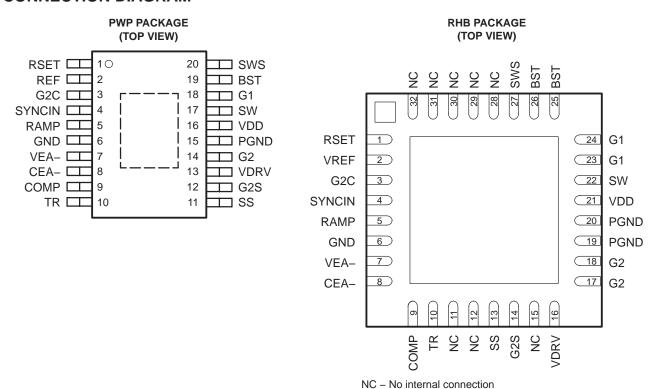

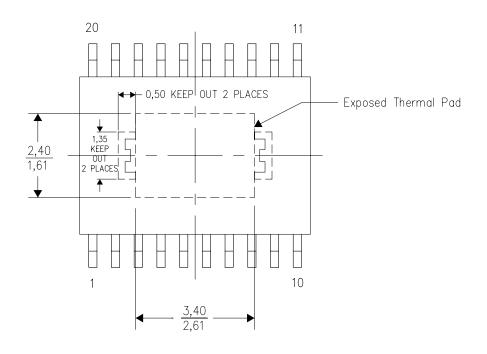

## **CONNECTION DIAGRAM**

NOTE: The PowerPAD™ is not directly connected to any lead of the package, but is thermally connected to the substrate of the device. The exposed dimension is 1.3 mm x 1.7 mm for the PWP package and 3.25 mm x 3.25 mm for the RHB package. However, the tolerances can be +1.05 mm / -0.05 mm (+41 mils / -2 mils) due to position and mold flow variation.

## THERMAL INFORMATION

| PACKAGE<br>FAMILY       | PACKAGE<br>DESIGNATOR | θ <b>JA (°C/W)</b><br>(with PowerPAD) | θ <b>JC (°C/W)</b><br>(without PowerPAD) | θ <b>JC (°C/W)</b><br>(with PowerPAD) | MAXIMUM DIE<br>TEMPERATURE |

|-------------------------|-----------------------|---------------------------------------|------------------------------------------|---------------------------------------|----------------------------|

| PowerPAD™<br>HTSSOP-20  | PWP                   | 22.3 to 32.6<br>(500 to 0 LFM)        | 19.9                                     | 1.4                                   | 125°C                      |

| Quad Flatpack<br>QFN-32 | RHB                   | 22.3 to 32.6<br>(500 to 0 LFM)        | 19.9                                     | 1.4                                   | 125°C                      |

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \text{ V}, 1 - \mu \text{F capacitor from VDD to GND, } 1 - \mu \text{F capacitor from BST to SW, } 1 - \mu \text{F capacitor from REF to GND, } 0.1 - \mu \text{F and } 2.2 - \mu \text{F capacitors from VDRV to PGND, } C_{RAMP} = 517 \text{ pF, } R_{SET} = 10 \text{ k}\Omega, T_{A} = T_{J} = -40^{\circ}\text{C to } 105^{\circ}\text{C}, \text{ (unless otherwise noted)}.$

|                    | PARAMETER                               | TEST CONDITIONS                                                                | MIN  | TYP  | MAX  | UNIT |

|--------------------|-----------------------------------------|--------------------------------------------------------------------------------|------|------|------|------|

| OVERALL            | -                                       |                                                                                |      |      |      |      |

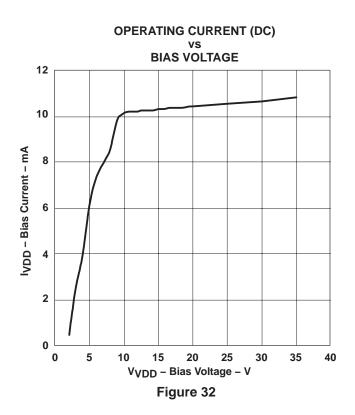

| h                  | Operating current                       | DC, after G2 timeout                                                           | 5    | 8    | 10   | A    |

| IVDD               | Operating current                       | $C_{LOAD} = 2.2 \text{ nF}$                                                    | 9    | 18   | 30   | mA   |

| UNDERV             | OLTAGE LOCKOUT                          |                                                                                |      |      |      |      |

| V <sub>VDD</sub>   | Start threshold voltage                 | MODE 1                                                                         | 8.0  | 8.5  | 9.0  |      |

| $V_{VDD}$          | Stop threshold voltage                  | MODE 1                                                                         | 7.5  | 8.0  | 8.5  |      |

| V <sub>VDD</sub>   | Hysteresis                              | MODE 1                                                                         | 0.3  | 0.5  | 0.8  |      |

| V <sub>VDR</sub> V | Start threshold voltage                 | MODE 2                                                                         | 4.30 | 4.65 | 4.85 |      |

| V <sub>VDR</sub> V | Stop threshold voltage                  | MODE 2                                                                         | 4.0  | 4.3  | 4.6  | V    |

| V <sub>VDR</sub> V | Hysteresis                              | MODE 2                                                                         | 0.15 | 0.35 | 0.55 |      |

| VREF               | Start threshold voltage                 | MODE 3 V <sub>VDD</sub> = V <sub>VDRV</sub>                                    | 2.5  | 2.8  | 3.2  |      |

| V <sub>REF</sub>   | Stop threshold voltage                  | MODE 3                                                                         | 2.2  | 2.5  | 2.8  |      |

| V <sub>REF</sub>   | Hysteresis                              | MODE 3                                                                         | 0.15 | 0.35 | 0.55 |      |

|                    | REFERENCE (REF)                         | •                                                                              |      |      |      |      |

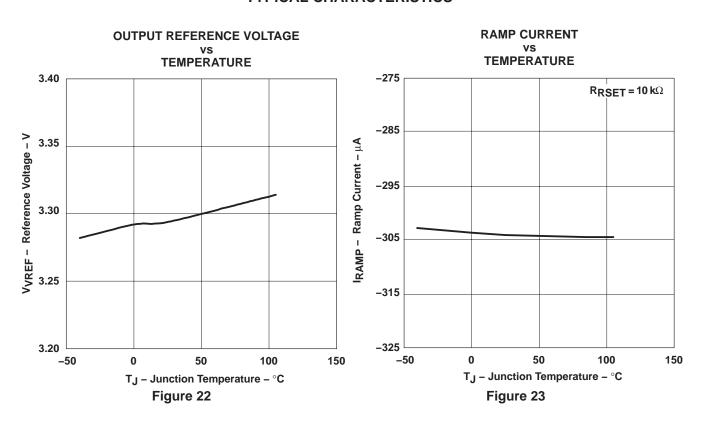

|                    |                                         | T <sub>A</sub> = 25°C                                                          | 3.28 | 3.30 | 3.35 |      |

| VREF               | Reference output voltage                | Total variation                                                                | 3.2  | 3.3  | 3.4  | V    |

| I <sub>SC</sub>    | Short circuit current                   | V <sub>REF</sub> = 0 V, T <sub>A</sub> = 25°C                                  | 10   | 13   | 20   | mΑ   |

|                    | Line regulation                         | 5.25 V ≤ V <sub>DRV</sub> ≤ 7.2 V                                              | 0    | 1.5  | 15   |      |

|                    | Load regulation                         | 0 mA ≤ I <sub>REF</sub> ≤ 5 mA                                                 | 0    | 30   | 70   | mV   |

| Oscillator         | PWM (RAMP)                              |                                                                                |      |      |      |      |

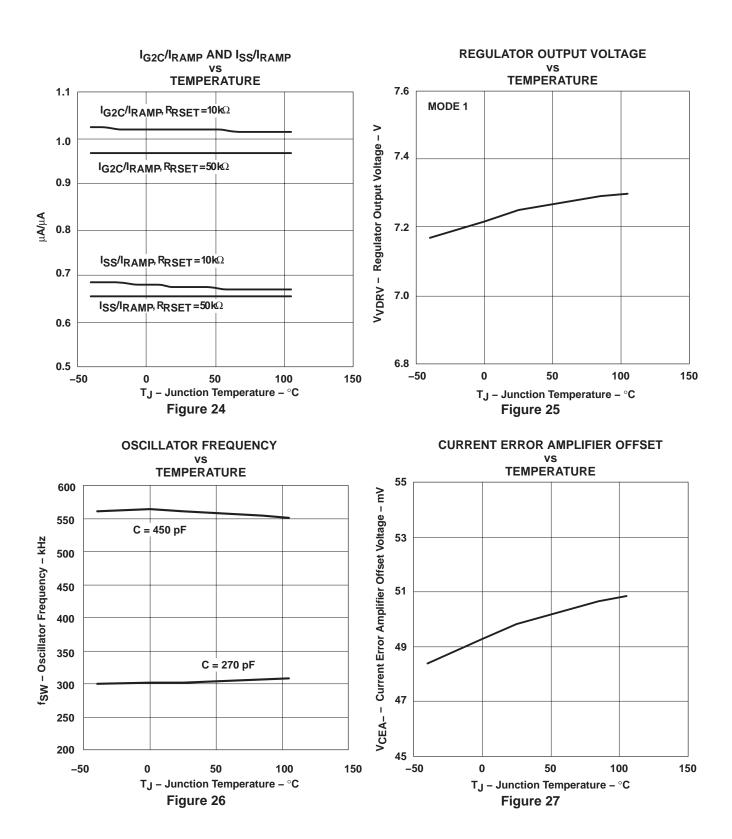

| fsw                | Oscillator frequency                    |                                                                                | 270  | 300  | 330  | kHz  |

| D <sub>MIN</sub>   | Minimum duty cycle                      |                                                                                |      |      | 0%   |      |

| VRAMP              | Offset voltage                          |                                                                                | 0.10 | 0.25 | 0.50 |      |

|                    | Oscillator peak voltage                 |                                                                                | 1.7  | 2.0  | 2.3  | V    |

| <sup>t</sup> DEAD  | G1 deadtime at maximum duty cycle ratio |                                                                                | 150  | 175  | 200  | ns   |

| IRAMP              | Ramp charge current                     | R <sub>RSET</sub> = 10 kΩ                                                      | -325 | -300 | -275 | μА   |

|                    | T ERROR AMPLIFIER                       | NOET                                                                           | •    |      |      | •    |

| VCEA+              | Offset voltage                          | Total variation                                                                | 45   | 50   | 55   | mV   |

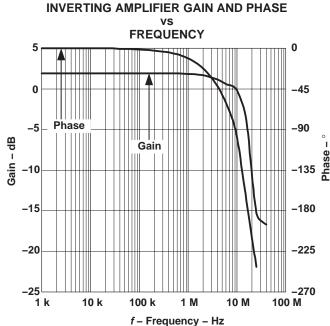

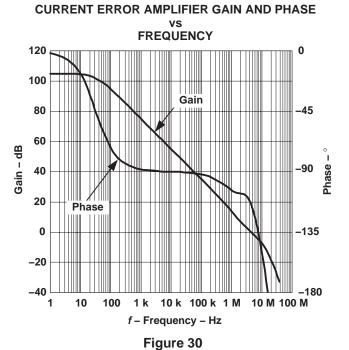

| GBW                | Gain bandwidth <sup>(3)</sup>           |                                                                                | 3    | 4    |      | MHz  |

|                    |                                         | I <sub>COMP</sub> = 0 A, V <sub>CEA</sub> = 3.3 V, V <sub>VEA</sub> = 2.0 V    |      |      | 0.1  |      |

| VOL                | Low-level output voltage                | I <sub>COMP</sub> = 100 μA, V <sub>CEA</sub> = 1.5 V<br>V <sub>VEA</sub> = 1 V | 0    | 0.60 | 0.90 | V    |

| VOH                | High-level output voltage               | I <sub>COMP</sub> = 0 A, V <sub>CEA</sub> = 0 V, V <sub>VEA</sub> = 1 V        | 2.2  | 2.5  | 3.0  | V    |

| Avol               | Open loop                               |                                                                                | 60   | 100  | 160  | dB   |

| I <sub>BIAS</sub>  | Bias current                            |                                                                                | -200 | -80  | -10  | nA   |

| ISINK              | Sink current                            | VCOMP = 1.0 V, VCEA_ = 1.5 V,<br>VVEA_ = 1 V                                   | 0.30 | 0.80 | 1.70 | mA   |

|                    | Common mode input range <sup>(3)</sup>  |                                                                                |      |      |      |      |

<sup>(3)</sup> Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \text{ V, 1-$\mu$F} \text{ capacitor from VDD to GND, 1-$\mu$F} \text{ capacitor from BST to SW, 1-$\mu$F} \text{ capacitor from REF to GND, 0.1-$\mu$F} \text{ and 2.2-$\mu$F} \text{ capacitors from VDRV to PGND, C}_{RAMP} = 517 \text{ pF, R}_{SET} = 10 \text{ k}\Omega, T_{A} = T_{J} = -40 ^{\circ}\text{C} \text{ to 105}^{\circ}\text{C}, \text{ (unless otherwise noted)}$

|                   | PARAMETER                                | TEST CONDITIONS                                                                                       | MIN   | TYP   | MAX   | UNIT |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| VOLTAGE           | ERROR AMPLIFIER                          |                                                                                                       |       |       |       |      |

| VSS_OFF           | Offset voltage from soft-start input     | VCOMP = VVEA-, VSS- = 1.5 V                                                                           | 0.40  | 0.75  | 1.00  | V    |

| VTR_OFF           | Offset voltage from tracking input       | V <sub>TR</sub> = 1.0 V                                                                               | -10   |       | 10    | mV   |

| V                 | Threehold valte as /freez \/ [A 45 COMP) | $0^{\circ}C \leq T_{A} \leq 105^{\circ}C$                                                             | 1.485 | 1.500 | 1.515 | V    |

| V <sub>VEA+</sub> | Threshold voltage (from VEA- to COMP)    | Total variation                                                                                       | 1.47  | 1.50  | 1.53  | V    |

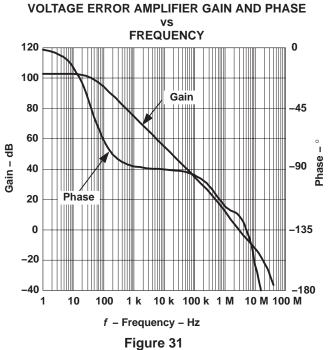

| GBW               | Gain bandwidth(3)                        |                                                                                                       | 3     | 4     |       | MHz  |

|                   | Landard advantage                        | I <sub>COMP</sub> = 0 A,<br>V <sub>VEA</sub> = 2.0 V,                                                 |       |       | 0.1   |      |

| V <sub>OL</sub>   | Low-level output voltage                 | $I_{COMP} = 100 \mu A$ , $V_{CEA} = 0 V$ , $V_{VEA} = 1 V$ , $V_{TR} = 0 V$                           | 0     | 0.60  | 0.9   | V    |

| VOH               | High-level output voltage                | ICOMP = 0 A, VCEA_ = 0 V<br>VVEA_ = 1 V                                                               | 2.2   | 2.5   | 3.0   |      |

| AVOL              | Open loop                                |                                                                                                       | 60    | 100   | 140   | dB   |

| I <sub>BIAS</sub> | Bias current                             |                                                                                                       | -500  | -250  | -50   | nA   |

| ISINK             | Sink current                             | V <sub>COMP</sub> = 1.0 V, V <sub>CEA</sub> = 0 V,<br>V <sub>VEA</sub> = 1.0 V, V <sub>TR</sub> = 0 V | 0.30  | 0.80  | 1.70  | mA   |

| CURRENT           | SET                                      |                                                                                                       |       |       |       |      |

| lout              | Output current                           | R <sub>RSET</sub> = 10 kΩ                                                                             | -158  | -150  | -142  | μΑ   |

| VRSET             | RSET voltage                             | R <sub>RSET</sub> = 10 kΩ                                                                             | 1.42  | 1.50  | 1.58  | V    |

| SYNCHRO           | NIZATION AND SHUTDOWN TIMER (SYNCIN      | , G2C)                                                                                                | •     |       |       |      |

|                   | Timer threshold                          |                                                                                                       | 2.3   | 2.5   | 2.7   | .,   |

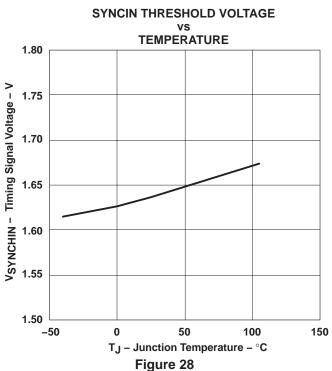

|                   | SYNCIN threshold                         |                                                                                                       | 1.50  | 1.65  | 1.80  | V    |

| ICHG(G2C)         | Shutdown timer charge current            | R <sub>RSET</sub> = 10 kΩ                                                                             | -325  | -300  | -275  | μΑ   |

| SOFT-STA          | RT (SS)                                  |                                                                                                       |       |       |       |      |

| ICH(SS)           | Charge current                           | $R_{RSET} = 10 \text{ k}\Omega$                                                                       | -230  | -200  | -170  | _    |

| IDSCH(SS)         | Discharge current                        | $R_{RSET} = 10 \text{ k}\Omega$                                                                       | 45    | 70    | 100   | μА   |

|                   | Discharge/shutdown threshold             |                                                                                                       | 0.35  | 0.45  | 0.55  | V    |

| DRIVE REC         | GULATOR (VDRV)                           |                                                                                                       |       |       |       |      |

| V <sub>VDRV</sub> | Output voltage                           |                                                                                                       | 6.87  | 7.20  | 7.53  | V    |

|                   | Line regulation                          | 9 V ≤ V <sub>VDD</sub> ≤ 35 V                                                                         | 0     | 50    | 100   | \/   |

|                   | Load regulation                          | $-5 \text{ mA} \le I_{VDRV} \le 0 \text{ mA}$                                                         | 0     | 50    | 100   | mV   |

| I <sub>SC</sub>   | Short-circuit current                    |                                                                                                       | 15    | 30    | 50    | mA   |

| <b>G2S GATE</b>   | DRIVE SENSE                              |                                                                                                       |       |       |       |      |

|                   | G2S rising threshold voltage             | V <sub>SWS</sub> = 0 V                                                                                | 1.90  | 2.25  | 3.10  | V    |

|                   | G2S falling threshold voltage            | V <sub>SWS</sub> = 0 V                                                                                | 1.00  | 1.25  | 1.30  | V    |

| I <sub>G2S</sub>  | Current                                  | V <sub>G2S</sub> = 0 V                                                                                | -0.70 | -0.50 | -0.37 | mA   |

| SWS SWIT          | CH NODE SENSE                            |                                                                                                       |       |       |       |      |

|                   | SWS rising threshold voltage             | V <sub>G2S</sub> = 0 V                                                                                | 1.90  | 2.25  | 2.90  | .,   |

|                   | SWS falling threshold voltage            | V <sub>G2S</sub> = 0 V                                                                                | 1.0   | 1.2   | 1.3   | V    |

| loves             | Current                                  | V <sub>SWS</sub> = 0 V                                                                                | -1.8  | -1.3  | -0.9  | mA   |

| Isws              | Current                                  | Outputs disabled                                                                                      | -1.0  |       | 1.0   | μΑ   |

|                   | Negative threshold voltage               |                                                                                                       | -0.5  | -0.3  | -0.1  | V    |

<sup>(3)</sup> Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 12 \text{ V}, 1\text{-}\mu\text{F capacitor from VDD to GND, } 1\text{-}\mu\text{F capacitor from BST to SW, } 1\text{-}\mu\text{F capacitor from REF to GND, } 0.1\text{-}\mu\text{F and } 2.2\text{-}\mu\text{F capacitors from VDRV to PGND, } C_{RAMP} = 517 \text{ pF, } R_{SET} = 10 \text{ k}\Omega, T_{A} = T_{J} = -40^{\circ}\text{C to } 105^{\circ}\text{C}, \text{ (unless otherwise noted)}$

|                     | PARAMETER                     |                            | TEST CONDITIONS         | S                        | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------|----------------------------|-------------------------|--------------------------|-----|-----|-----|------|

| G1 MAIN C           | DUTPUT                        | •                          |                         |                          |     |     |     |      |

| RSINK               | Sink resistance               | $V_{SW} = 0 V$             | V <sub>BST</sub> = 6 V, | V <sub>G1</sub> = 0.3 V  | 0.3 | 0.7 | 1.3 |      |

| R <sub>SRC</sub>    | Source resistance             | $V_{SW} = 0 V$             | $V_{BST} = 6 V$ ,       | $V_{G1} = 5.7 \text{ V}$ | 10  | 25  | 45  | Ω    |

| ISINK               | Sink current(3)               | $V_{SW} = 0 V$             | $V_{BST} = 6 V$ ,       | V <sub>G1</sub> = 3.0 V  |     | 3   |     |      |

| ISRCE               | Source current(3)             | $V_{SW} = 0 V$             | $V_{BST} = 6 V$ ,       | V <sub>G1</sub> = 3.0 V  |     | -3  |     | Α    |

| <sup>t</sup> RISE   | Rise time                     | C <sub>LOAD</sub> = 2.2 nF | F, from G1 to SW        |                          |     | 12  | 25  |      |

| tFALL               | Fall time                     | C <sub>LOAD</sub> = 2.2 nF | F, from G1 to SW        |                          |     | 12  | 25  | ns   |

| G2 SYNCH            | IRONOUS RECTIFIER OUTPUT      |                            |                         |                          |     |     |     |      |

| RSINK               | Sink resistance               | $V_{G2} = 0.3 V$           |                         |                          | 5   | 15  | 30  | Ω    |

| ISINK               | Sink current(3)               | $V_{G2} = 3.25 \text{ V}$  |                         |                          |     | 3   |     |      |

| ISRC                | Source current(3)             | $V_{G2} = 3.25 \text{ V}$  |                         |                          |     | -3  |     | Α    |

| <sup>t</sup> RISE   | Rise time                     | C <sub>LOAD</sub> = 2.2 nF | , from G2 to PGND       |                          |     | 12  | 25  |      |

| tFALL               | Fall time                     | C <sub>LOAD</sub> = 2.2 nF | f, from G2 to PGND      |                          |     | 12  | 25  | ns   |

| Vон                 | High-level output voltage, G2 | V <sub>SW</sub> = GND      |                         |                          | 6.2 | 6.7 | 7.5 | V    |

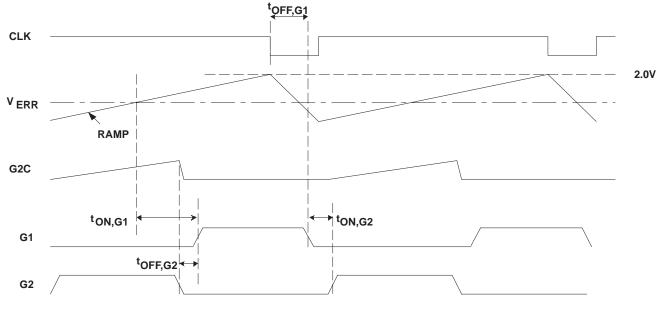

| DEADTIME            | DELAY (see Figure 1)          |                            |                         |                          |     |     |     |      |

| tON(G1)             | RAMP rising to G1 rising      |                            |                         |                          | 90  | 115 | 130 |      |

| tOFF(G1)            | SYNCIN falling to G1 falling  |                            |                         |                          | 50  | 70  | 90  |      |

| tON(G2)<br>tOFF(G2) | Delay control resolution      |                            |                         |                          | 3.5 | 5.0 | 6.5 |      |

| tON(G2)             | G2 on-time minimum            | wrt G1 falling             |                         |                          |     | -24 |     | ns   |

| tON(G2)             | G2 on-time maximum            | wrt G1 falling             |                         |                          |     | 62  |     |      |

| tOFF(G2)            | G2 off-time minimum           | wrt G1 rising              |                         |                          |     | -68 |     |      |

| tOFF(G2)            | G2 off-time maximum           | wrt G1 rising              |                         |                          |     | 10  |     |      |

<sup>(3)</sup> Ensured by design. Not production tested.

Figure 1. Predictive Gate Drive Timing Diagram

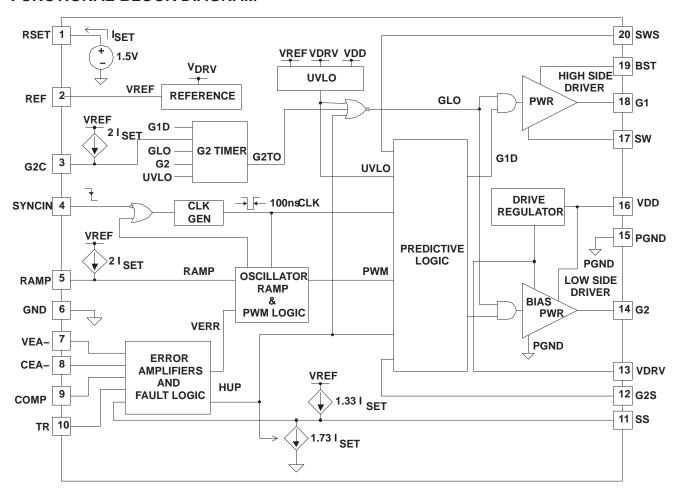

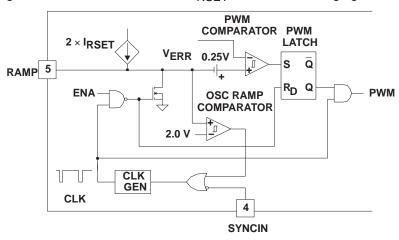

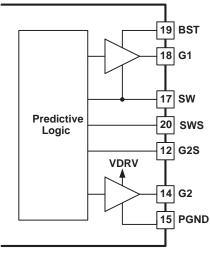

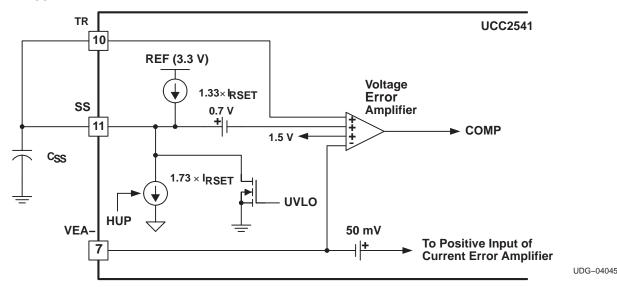

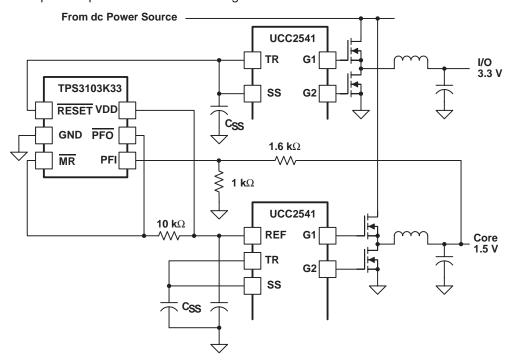

# **FUNCTIONAL BLOCK DIAGRAM**

# **PIN ASSIGNMENTS**

| time.  GND 6 - Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.  PGND 15 - Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.  RAMP 5 I Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.  REF(1) 2 I/O 3.3-V reference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.  RSET 1 I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).  SS 11 I Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.  SYNCIN 4 I Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SW 17 - G1 driver return connection.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TERMINAL           |     | 1/0 | PERCENTENT                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SST to SW with an external capacitor.  CEA- 8 I Inverting input of the current error amplifier used for output current regulation.  COMP 9 I Output of the voltage and current error amplifiers for compensation.  G1 18 O High-side gate driver output that swings between SW and BST.  G2 14 O Low-side gate driver output that swings between PGND and VDRV.  G2C 3 I Timer pin to turn off synchronous rectifier. The capacitor connected to this pin programs the maximum duration that G2 is allowed to stay HIGH.  G2S 12 I Used by the predictive deadtime controller for sensing the SR MOSFET gate voltage to set the appropriate deadtime.  GND 6 - Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.  GND 15 - Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.  RAMP 5 I Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.  3.3-V reference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.  REFT 1 I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).  Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.  SYNCIN 4 I Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDRV 13 II Output of the drive regul | NAME               | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

| COMP         9         I         Output of the voltage and current error amplifiers for compensation.           G1         18         O         High-side gate driver output that swings between SW and BST.           G2         14         O         Low-side gate driver output that swings between PGND and VDRV.           G2C         3         I         Timer pin to turn off synchronous rectifier. The capacitor connected to this pin programs the maximum duration that G2 is allowed to stay HIGH.           G2S         12         I         Used by the predictive deadtime controller for sensing the SR MOSFET gate voltage to set the appropriate deadtime.           GND         6         -         Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.           PGND         15         -         Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.           RAMP         5         I         Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.           REF(1)         2         I/O         J. Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.           REF(1)         2         I/O         J. Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.           REF(1)         2         I/O         J. J. Prin to program full meas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BST                | 19  | 1   |                                                                                                                                                                                                                                                                                                                              |

| G1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CEA-               | 8   | I   | Inverting input of the current error amplifier used for output current regulation.                                                                                                                                                                                                                                           |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | COMP               | 9   | I   | Output of the voltage and current error amplifiers for compensation.                                                                                                                                                                                                                                                         |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | G1                 | 18  | 0   | High-side gate driver output that swings between SW and BST.                                                                                                                                                                                                                                                                 |

| 12   Label Description of the stay HIGH.  G2S   12   Label Description of the stay HIGH.  G2S   12   Label Description of the stay HIGH.  G2S   13   Label Description of the stay HIGH.  G3S   14   Label Description of the stay HIGH.  G3S   Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.  G3D   Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.  FGND   15   Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.  RAMP   5   Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.  REF(1)   2   I/O   3.3-V reference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode) 3 or if it has large or pulsating loads.  RSET   1   I   Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).  SS   11   I   Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.  SYNCIN   4   I   Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SW   17   G1 driver return connection.  SWS   20   I   Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR   10   I   Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD   16   I   Power supply pin to the device and input to the internal VDRV drive regulator. Normal VDD range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.               | G2                 | 14  | 0   | Low-side gate driver output that swings between PGND and VDRV.                                                                                                                                                                                                                                                               |

| GND 6 - Ground for internal circuitry. GND and PGND should be tied together under the device. See layout guidelines for further details.  Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.  RAMP 5 I Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.  REF(1) 2 I/O µ Fo capacitance for REF loads that are 0 mA to −1 mA. Bypass this pin with at least 0.1 µ F of capacitance for REF loads that are 0 mA to −1 mA. Bypass this pin with at least 1 µ F of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.  RSET 1 I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 µ A to 150 µ A, respectively).  SS 11 I Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.  SYNCIN 4 I Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SW 17 - G1 driver return connection.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V <sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 µ F of capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G2C                | 3   | I   |                                                                                                                                                                                                                                                                                                                              |

| Figure 15 - Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.  RAMP 5 I Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.  REF(1) 2 I/O 3.3-V reference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to –1 mA. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to –1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.  RSET 1 I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).  SS 11 I Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.  SYNCIN 4 I Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SW 17 - G1 driver return connection.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V <sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | G2S                | 12  | ı   | Used by the predictive deadtime controller for sensing the SR MOSFET gate voltage to set the appropriate dead-time.                                                                                                                                                                                                          |

| <ul> <li>RAMP 5 I Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.</li> <li>REF(1) 2 I/O µ For ference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 µ F of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 µ F of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.</li> <li>RSET 1 I I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 µ A to 150 µ A, respectively).</li> <li>Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.</li> <li>SYNCIN 4 I Input pin for timing signal. Tie to logic high (V<sub>REF</sub>) when not used.</li> <li>SW 17 - G1 driver return connection.</li> <li>SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.</li> <li>Tracking input to the voltage error amplifier. Connect to REF when not used.</li> <li>VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V<sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 µ F of capacitance.</li> <li>VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND                | 6   | -   |                                                                                                                                                                                                                                                                                                                              |

| REF(1)       2       I/O       3.3-V reference pin. All analog control circuits are powered from this 3.3-V rail. Bypass this pin with at least 0.1 μF of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.         RSET       1       I       Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).         SS       11       I       Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.         SYNCIN       4       I       Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.         SW       17       -       G1 driver return connection.         SWS       20       I       Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.         TR       10       I       Tracking input to the voltage error amplifier. Connect to REF when not used.         VDD       16       I       Power supply pin to the device and input to the internal VDRV drive regulator. Normal VDD range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.         VDRV       13       I       Output of the drive regulator and power supply pin fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PGND               | 15  | _   | Ground return for the G2 driver. Connect PGND to the pc-board ground plane with several vias.                                                                                                                                                                                                                                |

| <ul> <li>REF<sup>(1)</sup> 2 I/O μF of capacitance for REF loads that are 0 mA to -1 mA. Bypass this pin with at least 1 μF of capacitance if it is used as an input (Mode 3) or if it has large or pulsating loads.</li> <li>RSET 1 I I Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).</li> <li>Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.</li> <li>SYNCIN 4 I Input pin for timing signal. Tie to logic high (V<sub>REF</sub>) when not used.</li> <li>SWS 17 - G1 driver return connection.</li> <li>SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.</li> <li>Tracking input to the voltage error amplifier. Connect to REF when not used.</li> <li>VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V<sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.</li> <li>VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RAMP               | 5   | I   | Input pin to connect timing capacitor to GND to generate the oscillator PWM ramp.                                                                                                                                                                                                                                            |

| <ul> <li>RSET 1 I tional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 kΩ to 50 kΩ (giving a programmable nominal ISET range of 30 μA to 150 μA, respectively).</li> <li>SS 11 I Soft start and shutdown pin. Connect a capacitor to GND to set the soft-start time. Add switch to GND for immediate shutdown functionality.</li> <li>SYNCIN 4 I Input pin for timing signal. Tie to logic high (V<sub>REF</sub>) when not used.</li> <li>SW 17 - G1 driver return connection.</li> <li>SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.</li> <li>TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.</li> <li>VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V<sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.</li> <li>VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REF <sup>(1)</sup> | 2   | I/O | $\mu$ F of capacitance for REF loads that are 0 mA to $-1$ mA. Bypass this pin with at least 1 $\mu$ F of capacitance if it is                                                                                                                                                                                               |

| SYNCIN 4 I Input pin for timing signal. Tie to logic high (V <sub>REF</sub> ) when not used.  SW 17 - G1 driver return connection.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V <sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.  VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RSET               | 1   | I   | Pin to program timer currents for G2C, RAMP, SS charge and SS discharge. This pin generates a current proportional to the value of the external resistor connected from RSET pin to GND. RSET range is 10 k $\Omega$ to 50 k $\Omega$ (giving a programmable nominal ISET range of 30 $\mu$ A to 150 $\mu$ A, respectively). |

| SW 17 - G1 driver return connection.  SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal VDD range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.  VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SS                 | 11  | 1   |                                                                                                                                                                                                                                                                                                                              |

| SWS 20 I Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.  TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal VDD range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.  VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SYNCIN             | 4   | I   | Input pin for timing signal. Tie to logic high (VREF) when not used.                                                                                                                                                                                                                                                         |

| TR 10 I Tracking input to the voltage error amplifier. Connect to REF when not used.  VDD 16 I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V <sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.  VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SW                 | 17  | _   | G1 driver return connection.                                                                                                                                                                                                                                                                                                 |

| <ul> <li>VDD</li> <li>16</li> <li>I Power supply pin to the device and input to the internal VDRV drive regulator. Normal V<sub>DD</sub> range is from 4.5 V to 36 V. Bypass the pin with at least 1 μF of capacitance.</li> <li>VDRV</li> <li>13</li> <li>I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SWS                | 20  | I   | Used by the predictive controller to sense SR body-diode conduction. Connect to SR MOSFET drain close to the MOSFET package.                                                                                                                                                                                                 |

| VDRV 13 I 36 V. Bypass the pin with at least 1 μF of capacitance.  VDRV 13 I Output of the drive regulator and power supply pin for the G2 driver. VDRV is also the supply voltage for the internal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TR                 | 10  | I   | Tracking input to the voltage error amplifier. Connect to REF when not used.                                                                                                                                                                                                                                                 |

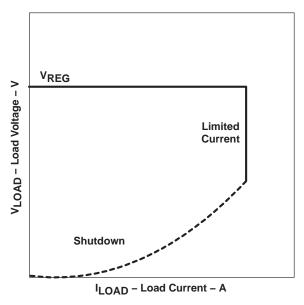

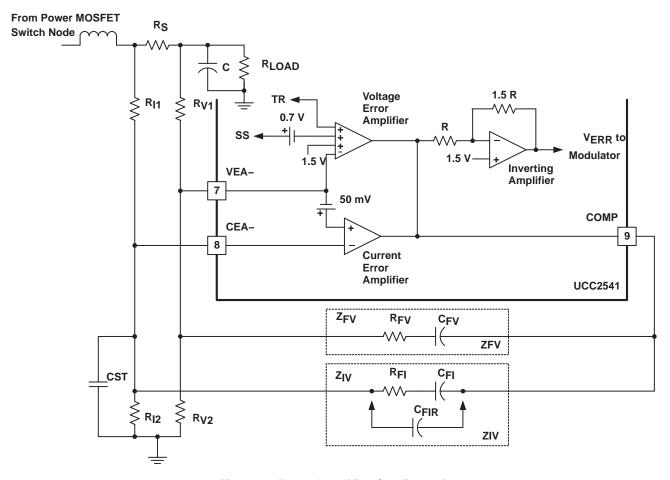

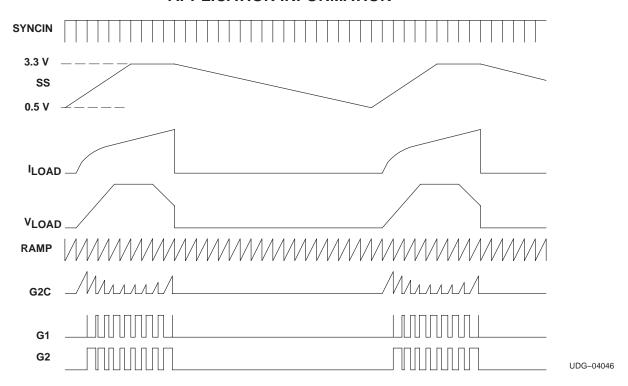

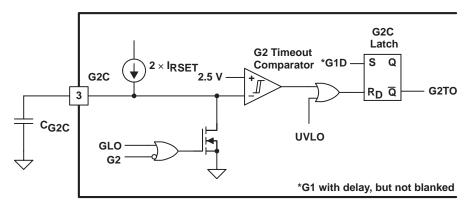

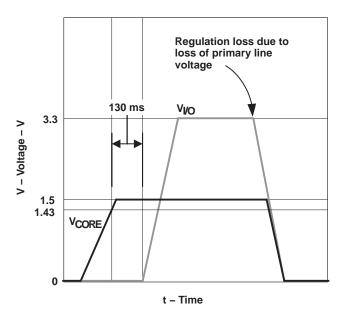

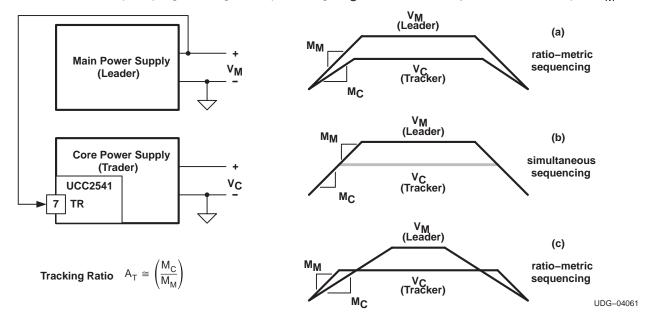

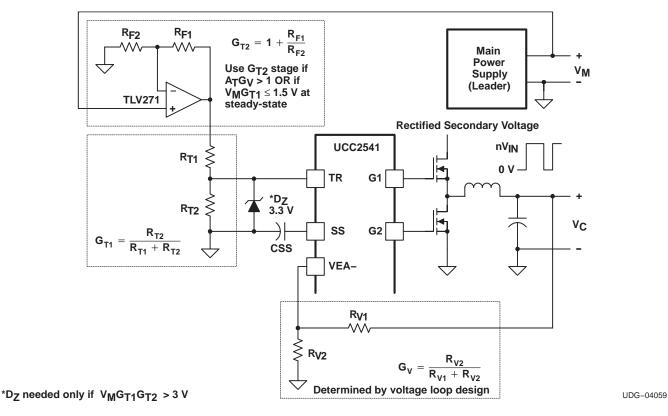

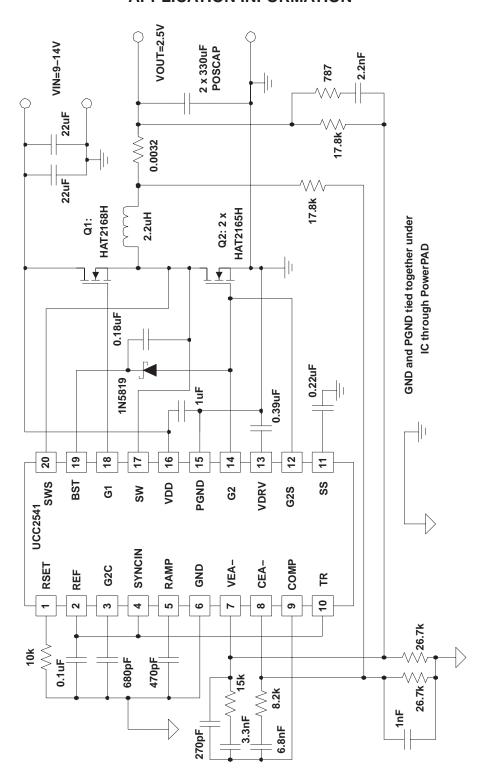

| ternal logic and control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD                | 16  | 1   | Power supply pin to the device and input to the internal VDRV drive regulator. Normal $V_{DD}$ range is from 4.5 V to 36 V. Bypass the pin with at least 1 $\mu$ F of capacitance.                                                                                                                                           |