www.ti.com

SCDS193D-AUGUST 2006-REVISED MARCH 2009

## **SPST CMOS ANALOG SWITCHES**

#### **FEATURES**

- 2-V to 12-V Single-Supply Operation

- Specified ON-State Resistance:

- 15 Ω Max With 12-V Supply

- 20 Ω Max With 5-V Supply

- 50 Ω Max With 3.3-V Supply

- Specified Low OFF-Leakage Currents:

- 1 nA at 25°C

- 10 nA at 85°C

- Specified Low ON-Leakage Currents:

- 1 nA at 25°C

- 10 nA at 85°C

- Low Charge Injection: 11.5 pC (12-V Supply)

- Fast Switching Speed:

- $t_{ON} = 80 \text{ ns}, t_{OFF} = 50 \text{ ns} (12-V \text{ Supply})$

- Break-Before-Make Operation (t<sub>ON</sub> > t<sub>OFF</sub>)

- TTL/CMOS-Logic Compatible With 5-V Supply

### **DESCRIPTION/ORDERING INFORMATION**

The TS12A4514/TS12A4515 are single pole/single throw (SPST), low-voltage, single-supply CMOS analog switches, with very low switch ON-state resistance. The TS12A4514 is normally open (NO). The TS12A4515 is normally closed (NC).

These CMOS switches can operate continuously with a single supply between 2 V and 12 V. Each switch can handle rail-to-rail analog signals. The OFF-leakage current maximum is only 1 nA at 25°C or 10 nA at 85°C.

All digital inputs have 0.8-V to 2.4-V logic thresholds, ensuring TTL/CMOS-logic compatibility when using a 5-V supply.

For pin-compatible parts for use with dual supplies, see the TS12A4516/TS12A4517.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAC             | SE <sup>(1)(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING (3) |

|----------------|--------------------|----------------------|-----------------------|----------------------|

|                | PDIP – P           | Reel of 1000         | TS12A4514P            | TS12A4514P           |

|                | SOIC - D           | Reel of 1500         | TS12A4514D            | YD514                |

|                | 201C - D           | Reel of 2500         | TS12A4514DR           | TD514                |

| 4000 +- 0500   | SOP (SOT-23) - DBV | Reel of 3000         | TS12A4514DBVR         | 9CJ_                 |

| –40°C to 85°C  | PDIP – P           | Reel of 1000         | TS12A4515P            | TS12A4515P           |

|                | SOIC - D           | Reel of 1500         | TS12A4515D            | VDE4E                |

|                | 201C - D           | Reel of 2500         | TS12A4515DR           | YD515                |

|                | SOP (SOT-23) - DBV | Reel of 3000         | TS12A4515DBVR         | 9CK_                 |

- (1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

- (2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (3) DBV: The last character designates assembly/test Site

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

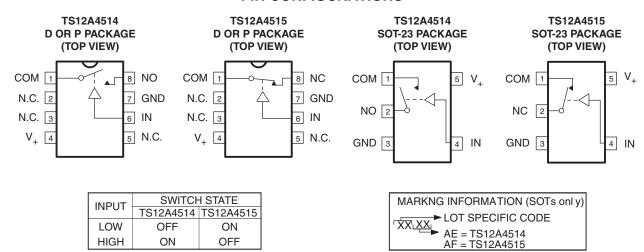

#### PIN CONFIGURATIONS

N.C. - Not internally connected

NO - Normally open

NC - Normally closed

### **Absolute Minimum and Maximum Ratings**(1)(2)

voltages referenced to GND

|                         |                                                          |                                                  | MIN                               | MAX | UNIT |

|-------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------|-----|------|

| V <sub>+</sub>          | Supply voltage range <sup>(3)</sup>                      |                                                  | -0.3                              | 13  | V    |

| $V_{NC} V_{NO} V_{COM}$ | Analog voltage range <sup>(4)</sup>                      | -0.3                                             | V <sub>+</sub> + 0.3<br>or ±20 mA | V   |      |

|                         | Continuous current into any terminal                     |                                                  | ±20                               | mA  |      |

|                         | Peak current, NO or COM (pulsed at 1 ms, 10% duty cycle) |                                                  |                                   |     | mA   |

|                         | ESD per method 3015.7                                    |                                                  |                                   |     | ٧    |

|                         |                                                          | 8-pin plastic DIP (derate 9.09 mW/°C above 70°C) |                                   | 727 |      |

|                         | Continuous power dissipation (T <sub>A</sub> = 70°C)     | 8-pin SOIC (derate 5.88 mW/°C above 70°C)        |                                   | 471 | mW   |

|                         |                                                          | 5-pin SOT-23 (derate 7.1 mW/°C above 70°C)       |                                   | 571 |      |

| T <sub>A</sub>          | Operating temperature range                              |                                                  |                                   |     | °C   |

| T <sub>stg</sub>        | tg Storage temperature range                             |                                                  |                                   |     | °C   |

|                         | Lead temperature (soldering, 10 s)                       |                                                  |                                   | 300 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum

<sup>(3)</sup> All voltages are with respect to ground, unless otherwise specified.

<sup>(4)</sup> Voltages exceeding V<sub>+</sub> or GND on any signal terminal are clamped by internal diodes. Limit forward-diode current to maximum current rating.

www.ti.com

# Electrical Characteristics for 5-V Supply<sup>(1)</sup>

$V_{+} = 4.5 \text{ V}$  to 5.5 V,  $V_{INH} = 2.4 \text{ V}$ ,  $V_{INL} = 0.8 \text{ V}$ ,  $T_{A} = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER                       | SYMBOL                            | TEST CONDITIONS                                                                       | T <sub>A</sub> | MIN TYP(2) | MAX            | UNIT |

|---------------------------------|-----------------------------------|---------------------------------------------------------------------------------------|----------------|------------|----------------|------|

| Analog Switch                   |                                   |                                                                                       | I              | ,          |                |      |

| Analog signal range             | $V_{COM}, V_{NO}, V_{NC}$         |                                                                                       |                | 0          | V <sub>+</sub> | V    |

| ON state resistance             | _                                 | $V_{+} = 4.5 \text{ V}, V_{COM} = 3.5 \text{ V},$                                     | 25°C           | 9.5        | 15             | 0    |

| ON-state resistance             | r <sub>on</sub>                   | I <sub>COM</sub> = 1 mA                                                               | Full           |            | 20             | Ω    |

| ON-state resistance             | _                                 | V <sub>COM</sub> = 1 V, 2 V, 3 V,                                                     | 25°C           | 1          | 3              | Ω    |

| flatness                        | r <sub>on(flat)</sub>             | I <sub>COM</sub> = 1 mA                                                               | Full           |            | 4              | 12   |

| NO, NC                          | I <sub>NO(OFF)</sub> ,            | V <sub>+</sub> = 5.5 V, V <sub>COM</sub> = 1 V,                                       | 25°C           |            | 1              | nA   |

| OFF leakage current (3)         | I <sub>NC(OFF)</sub>              | $V_{NO}$ or $V_{NC} = 4.5 \text{ V}$                                                  | Full           |            | 10             | ΠA   |

| СОМ                             | 1                                 | V <sub>+</sub> = 5.5 V, V <sub>COM</sub> = 1 V,                                       | 25°C           |            | 1              | ~ ^  |

| OFF leakage current (3)         | I <sub>COM(OFF)</sub>             | $V_{NO}$ or $V_{NC} = 4.5 \text{ V}$                                                  | Full           |            | 10             | nA   |

| СОМ                             |                                   | V <sub>+</sub> = 5.5 V, V <sub>COM</sub> = 4.5 V,                                     | 25°C           |            | 1              | A    |

| ON leakage current (3)          | I <sub>COM(ON)</sub>              | $V_{NO}$ or $V_{NC} = 4.5 \text{ V}$                                                  | Full           |            | 10             | nA   |

| Digital Control Input (IN)      |                                   | ·                                                                                     |                | <u>.</u>   |                |      |

| Input logic high                | V <sub>IH</sub>                   |                                                                                       | Full           | 2.4        | V <sub>+</sub> | V    |

| Input logic low                 | V <sub>IL</sub>                   |                                                                                       | Full           | 0          | 0.8            | V    |

| Input leakage current           | I <sub>IH</sub> , I <sub>IL</sub> | V <sub>IN</sub> = V <sub>+</sub> , 0 V                                                | Full           |            | 0.01           | μΑ   |

| Dynamic                         |                                   | ·                                                                                     | I              | ,          |                |      |

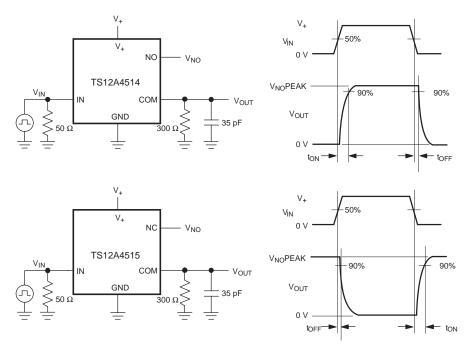

| Time on time                    | t <sub>ON</sub>                   |                                                                                       | 25°C           | 32         | 100            |      |

| Turn-on time                    |                                   | see Figure 2                                                                          | Full           |            | 125            | ns   |

| Time off time                   |                                   | Figure 0                                                                              | 25°C           | 25         | 50             |      |

| Turn-off time                   | t <sub>OFF</sub>                  | see Figure 2                                                                          | Full           |            | 60             | ns   |

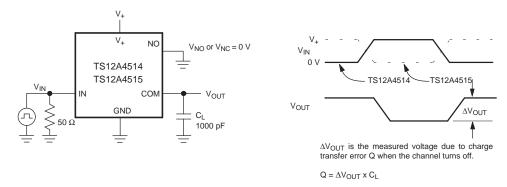

| Charge injection <sup>(4)</sup> | $Q_{C}$                           | $C_L = 1 \text{ nF}, V_{NO} = 0 \text{ V},$<br>$R_S = 0 \Omega, \text{ See Figure 1}$ | 25°C           | -3         |                | рС   |

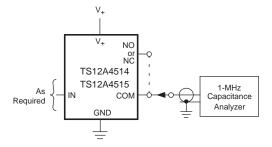

| NO, NC<br>OFF capacitance       | $C_{NO(OFF)}$ , $C_{NC(OFF)}$     | f = 1 MHz, See Figure 4                                                               | 25°C           | 7.5        |                | pF   |

| COM<br>OFF capacitance          | $C_{COM(OFF)}$                    | f = 1 MHz, See Figure 4                                                               | 25°C           | 7.5        |                | pF   |

| COM<br>ON capacitance           | C <sub>COM(ON)</sub>              | f = 1 MHz, See Figure 4                                                               | 25°C           | 19         |                | pF   |

| Digital input capacitance       | Cı                                | V <sub>IN</sub> = V <sub>+</sub> , 0 V                                                | 25°C           | 1.5        |                | pF   |

| Bandwidth                       | BW                                | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                  | 25°C           | 475        |                | MHz  |

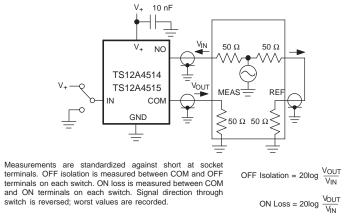

| OFF isolation                   | O <sub>ISO</sub>                  | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                  | 25°C           | -94        |                | dB   |

| Total harmonic distortion       | THD                               | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                  | 25°C           | 0.08       |                | %    |

| Supply                          |                                   |                                                                                       |                |            |                |      |

| V gunnhu gurrant                | 1                                 | \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                | 25°C           |            | 0.05           |      |

| V <sub>+</sub> supply current   | I <sub>+</sub>                    | $V_{IN} = 0 \text{ V or } V_+$                                                        | Full           |            | 0.1            | μΑ   |

The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

Typical values are at  $T_A = 25$ °C. Leakage parameters are 100% tested at maximum-rated hot operating temperature, and are ensured by correlation at 25°C.

Specified by design, not production tested

# Electrical Characteristics for 12-V Supply<sup>(1)</sup>

$V_{+}$  = 11.4 V to 12.6 V,  $V_{INH}$  = 5 V,  $V_{INL}$  = 0.8 V,  $T_{A}$  = -40°C to 85°C (unless otherwise noted)

| PARAMETER                          | SYMBOL                                       | TEST CONDITIONS                                                                            | $T_A$ | MIN TYP <sup>(2)</sup> | MAX            | UNIT |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|-------|------------------------|----------------|------|

| Analog Switch                      |                                              |                                                                                            |       |                        |                |      |

| Analog signal range                | $V_{COM}, V_{NO}, V_{NC}$                    |                                                                                            |       | 0                      | V <sub>+</sub> | V    |

| ON state mediates as               |                                              | $V_{+} = 11.4 \text{ V}, V_{COM} = 10 \text{ V},$                                          | 25°C  | 6.5                    | 10             | 0    |

| ON-state resistance                | r <sub>on</sub>                              | I <sub>COM</sub> = 1 mA                                                                    | Full  |                        | 15             | Ω    |

| ON-state resistance                |                                              | V <sub>+</sub> = 11.4 V,                                                                   | 25°C  | 1.5                    | 3              |      |

| flatness                           | r <sub>on(flat)</sub>                        | $V_{COM} = 2 \text{ V}, 5 \text{ V}, 10 \text{ V},$<br>$I_{COM} = 1 \text{ mA}$            | Full  |                        | 4              | Ω    |

| NO, NC                             | I <sub>NO(OFF)</sub> ,                       | $V_{+} = 12.6 \text{ V}, V_{COM} = 1 \text{ V},$                                           | 25°C  |                        | 1              | nA   |

| OFF leakage current (3)            | I <sub>NC(OFF)</sub>                         | $V_{NO}$ or $V_{NC} = 10 \text{ V}$                                                        | Full  |                        | 10             | ПА   |

| СОМ                                |                                              | V <sub>+</sub> = 12.6 V, V <sub>COM</sub> = 1 V,                                           | 25°C  |                        | 1              | ^    |

| OFF leakage current <sup>(3)</sup> | I <sub>COM(OFF)</sub>                        | $V_{NO}$ or $V_{NC} = 10 \text{ V}$                                                        | Full  |                        | 10             | nA   |

| СОМ                                |                                              | $V_{+} = 12.6 \text{ V}, V_{COM} = 10 \text{ V},$                                          | 25°C  |                        | 1              | A    |

| ON leakage current <sup>(3)</sup>  | I <sub>COM(ON)</sub>                         | $V_{+} = 12.6 \text{ V}, V_{COM} = 10 \text{ V}, V_{NO} \text{ or } V_{NC} = 10 \text{ V}$ | Full  |                        | 10             | nA   |

| Digital Control Input (IN)         |                                              |                                                                                            |       |                        |                |      |

| Input logic high                   | V <sub>IH</sub>                              |                                                                                            | Full  | 5                      | V <sub>+</sub> | V    |

| Input logic low                    | V <sub>IL</sub>                              |                                                                                            | Full  | 0                      | 0.8            | V    |

| Input leakage current              | I <sub>IH</sub> , I <sub>IL</sub>            | $V_{IN} = V_+, 0 V$                                                                        | Full  |                        | 0.01           | μΑ   |

| Dynamic                            |                                              |                                                                                            |       |                        |                | •    |

|                                    | t <sub>ON</sub>                              | See Figure 2                                                                               | 25°C  | 22                     | 75             |      |

| Turn-on time                       |                                              |                                                                                            | Full  |                        | 80             | ns   |

|                                    |                                              |                                                                                            | 25°C  | 20                     | 45             |      |

| Turn-off time                      | t <sub>OFF</sub>                             | See Figure 2                                                                               | Full  |                        | 50             | ns   |

| Charge injection <sup>(4)</sup>    | $Q_{C}$                                      | $C_L = 1 \text{ nF}, V_{NO} = 0 \text{ V},$<br>$R_S = 0 \Omega$ , See Figure 1             | 25°C  | -11.5                  |                | рС   |

| NO, NC<br>OFF capacitance          | C <sub>NO(OFF)</sub><br>C <sub>NC(OFF)</sub> | f = 1 MHz, See Figure 4                                                                    | 25°C  | 7.5                    |                | pF   |

| COM<br>OFF capacitance             | C <sub>COM(OFF)</sub>                        | f = 1 MHz, See Figure 4                                                                    | 25°C  | 7.5                    |                | pF   |

| COM<br>ON capacitance              | C <sub>COM(ON)</sub>                         | f = 1 MHz, See Figure 4                                                                    | 25°C  | 21.5                   |                | pF   |

| Digital input capacitance          | C <sub>I</sub>                               | V <sub>IN</sub> = V <sub>+</sub> , 0 V                                                     | 25°C  | 1.5                    |                | pF   |

| Bandwidth                          | BW                                           | $R_L = 50 \ \Omega, \ C_L = 15 \ pF, \ V_{NO} = 1 \ V_{RMS}, \ f = 100 \ kHz$              | 25°C  | 520                    |                | MHz  |

| OFF isolation                      | O <sub>ISO</sub>                             | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                       | 25°C  | -95                    |                | dB   |

| Total harmonic distortion          | THD                                          | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                       | 25°C  | 0.07                   |                | %    |

| Supply                             |                                              | <u> </u>                                                                                   |       |                        |                |      |

| M. aumaha auma-at                  |                                              | V 0.V == V                                                                                 | 25°C  |                        | 0.05           | A    |

| V <sub>+</sub> supply current      | I <sub>+</sub>                               | $V_{IN} = 0 \text{ V or } V_+$                                                             | Full  |                        | 0.2            | μΑ   |

The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

<sup>(2)</sup> Typical values are at T<sub>A</sub> = 25°C.

(3) Leakage parameters are 100% tested at maximum-rated hot operating temperature, and are ensured by correlation at 25°C.

Specified by design, not production tested

www.ti.com

## Electrical Characteristics for 3-V Supply<sup>(1)</sup>

$V_{+} = 3 \text{ V}$  to 3.6 V,  $T_{A} = -40^{\circ}\text{C}$  to 85°C (unless otherwise noted)

| PARAMETER                          | SYMBOL                          | TEST CONDITIONS                                                                         | T <sub>A</sub> | MIN TYP <sup>(2)</sup> | MAX            | UNIT  |

|------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------|----------------|------------------------|----------------|-------|

| Analog Switch                      |                                 | · ·                                                                                     |                | •                      |                |       |

| Analog signal range                | $V_{COM}$ , $V_{NO}$ , $V_{NC}$ |                                                                                         |                | 0                      | V <sub>+</sub> | V     |

| ON state registeres                | _                               | $V_{+} = 3 \text{ V}, V_{COM} = 1.5 \text{ V},$                                         | 25°C           | 18.5                   | 40             | 0     |

| ON-state resistance                | r <sub>on</sub>                 | $I_{NO} = 1 \text{ mA},$                                                                | Full           |                        | 50             | Ω     |

| ON-state resistance                |                                 | V <sub>+</sub> = 3 V,                                                                   | 25°C           | 1                      | 3              |       |

| flatness                           | r <sub>on(flat)</sub>           | V <sub>COM</sub> = 1 V, 1.5 V, 2 V,<br>I <sub>COM</sub> = 1 mA                          | Full           |                        | 4              | Ω     |

| NO, NC                             | I <sub>NO(OFF)</sub> ,          | $V_{+} = 3.6 \text{ V}, V_{COM} = 1 \text{ V},$                                         | 25°C           |                        | 1              | nA    |

| OFF leakage current (3)            | I <sub>NC(OFF)</sub>            | $V_{NO}$ or $V_{NC} = 3 \text{ V}$                                                      | Full           |                        | 10             | ПА    |

| COM                                | I <sub>COM(OFF)</sub>           | $V_{+} = 3.6 \text{ V}, V_{COM} = 1 \text{ V},$                                         | 25°C           |                        | 1              | nA    |

| OFF leakage current <sup>(3)</sup> | 'COM(OFF)                       | $V_{NO}$ or $V_{NC} = 3 \text{ V}$                                                      | Full           |                        | 10             | 117 \ |

| COM                                | I <sub>COM(ON)</sub>            | $V_{+} = 3.6 \text{ V}, V_{COM} = 3 \text{ V}, V_{NO} \text{ or } V_{NC} = 3 \text{ V}$ | 25°C           |                        | 1              | nA    |

| ON leakage current <sup>(3)</sup>  | ·COM(ON)                        | $V_{NO}$ or $V_{NC} = 3 \text{ V}$                                                      | Full           |                        | 10             | .,,   |

| Digital Control Input (IN)         |                                 |                                                                                         |                |                        | 1              |       |

| Input logic high                   | $V_{IH}$                        |                                                                                         | Full           | 2.4                    | $V_{+}$        | V     |

| Input logic low                    | $V_{IL}$                        |                                                                                         | Full           | 0                      | 8.0            | V     |

| Input leakage current              | $I_{IH},I_{IL}$                 | $V_{IN} = V_+, 0 V$                                                                     | Full           |                        | 0.01           | μΑ    |

| Dynamic                            |                                 |                                                                                         |                |                        |                |       |

| Turn-on time <sup>(4)</sup>        | t <sub>ON</sub>                 | See Figure 2                                                                            | 25°C           | 63                     | 120            | ns    |

| Turr-or time                       |                                 | See Figure 2                                                                            | Full           |                        | 175            | 113   |

| Turn-off time <sup>(4)</sup>       | t                               | See Figure 2                                                                            | 25°C           | 33                     | 80             | ns    |

|                                    | t <sub>OFF</sub>                | Occ Figure 2                                                                            | Full           |                        | 120            | 113   |

| Charge injection <sup>(4)</sup>    | $Q_{C}$                         | C <sub>L</sub> = 1 nF, See Figure 1                                                     | 25°C           | -1.5                   |                | рC    |

| NO, NC<br>OFF capacitance          | $C_{NO(OFF)},\ C_{NC(OFF)}$     | f = 1 MHz, See Figure 4                                                                 | 25°C           | 7.5                    |                | pF    |

| COM<br>OFF capacitance             | C <sub>COM(OFF)</sub>           | f = 1 MHz, See Figure 4                                                                 | 25°C           | 7.5                    |                | pF    |

| COM<br>ON capacitance              | C <sub>COM(ON)</sub>            | f = 1 MHz, See Figure 4                                                                 | 25°C           | 17                     |                | pF    |

| Digital input capacitance          | C <sub>I</sub>                  | V <sub>IN</sub> = V <sub>+</sub> , 0 V                                                  | 25°C           | 1.5                    |                | pF    |

| Bandwidth                          | BW                              | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                    | 25°C           | 460                    |                | MHz   |

| OFF isolation                      | O <sub>ISO</sub>                | $R_L = 50 \Omega, C_L = 15 pF,$<br>$V_{NO} = 1 V_{RMS}, f = 100 kHz$                    | 25°C           | -94                    |                | dB    |

| Total harmonic distortion          | THD                             | $R_L = 50 \ \Omega, \ C_L = 15 \ pF, \ V_{NO} = 1 \ V_{RMS}, \ f = 100 \ kHz$           | 25°C           | 0.15                   |                | %     |

| Supply                             |                                 | <u> </u>                                                                                |                |                        | '              |       |

| V cumply ourrest                   | 1                               | \/ - 0 \/ or \/                                                                         | 25°C           |                        | 0.03           | ^     |

| V <sub>+</sub> supply current      | I <sub>+</sub>                  | $V_{IN} = 0 \text{ V or } V_+$                                                          | Full           |                        | 0.05           | μΑ    |

The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

Typical values are at  $T_A = 25$ °C. Leakage parameters are 100% tested at maximum-rated hot operating temperature, and are ensured by correlation at 25°C.

Specified by design, not production tested

# PIN DESCRIPTION(1)

|         | PIN       | I NO.   |           |                |                                            |  |  |

|---------|-----------|---------|-----------|----------------|--------------------------------------------|--|--|

| TS12    | TS12A4514 |         | TS12A4515 |                | DESCRIPTION                                |  |  |

| D, P    | SOT-23    | D, P    | SOT-23    |                |                                            |  |  |

| 1       | 1         | 1       | 1         | COM            | Common                                     |  |  |

| 2, 3, 5 | _         | 2, 3, 5 | -         | N.C.           | No connect (not internally connected)      |  |  |

| 4       | 5         | 4       | 5         | V <sub>+</sub> | Power supply                               |  |  |

| 6       | 4         | 6       | 4         | IN             | Digital control to connect COM to NO or NC |  |  |

| 7       | 3         | 7       | 3         | GND            | Digital ground                             |  |  |

| 8       | 2         | _       | _         | NO             | Normally open                              |  |  |

| _       | _         | 8       | 2         | NC             | Normally closed                            |  |  |

<sup>(1)</sup> NO, NC, and COM pins are identical and interchangeable. Any may be considered as an input or an output; signals pass in both directions.

#### APPLICATION INFORMATION

### **Power-Supply Considerations**

The TS12A4514/TS12A4515 construction is typical of most CMOS analog switches, except that they have only two supply pins:  $V_+$  and GND.  $V_+$  and GND drive the internal CMOS switches and set their analog voltage limits. Reverse ESD-protection diodes are internally connected between each analog-signal pin and both  $V_+$  and GND. One of these diodes conducts if any analog signal exceeds  $V_+$  or GND.

Virtually all the analog leakage current comes from the ESD diodes to  $V_+$  or GND. Although the ESD diodes on a given signal pin are identical and, therefore, fairly well balanced, they are reverse biased differently. Each is biased by either  $V_+$  or GND and the analog signal. This means their leakages will vary as the signal varies. The difference in the two diode leakages to the  $V_+$  and GND pins constitutes the analog-signal-path leakage current. All analog leakage current flows between each pin and one of the supply terminals, not to the other switch terminal. This is why both sides of a given switch can show leakage currents of the same or opposite polarity.

There is no connection between the analog-signal paths and  $V_{+}$  or GND.

$V_+$  and GND also power the internal logic and logic-level translators. The logic-level translators convert the logic levels to switched  $V_+$  and GND signals to drive the analog signal gates.

### **Logic-Level Thresholds**

The logic-level thresholds are CMOS/TTL compatible when  $V_+$  is 5 V. As  $V_+$  is raised, the level threshold increases slightly. When  $V_+$  reaches 12 V, the level threshold is about 3 V – above the TTL-specified high-level minimum of 2.8 V, but still compatible with CMOS outputs.

#### **CAUTION:**

If the user is using the TS12A4514 or TS12A4515 with a V+ supply of 3 V, then the control input (IN) voltage should not exceed V+, otherwise the output levels can exceed 3 V and violate the absolute maximum rating, potentially damaging the device.

### **High-Frequency Performance**

In  $50-\Omega$  systems, signal response is reasonably flat up to 250 MHz (see *Typical Operating Characteristics*). Above 20 MHz, the on response has several minor peaks that are highly layout dependent. The problem is not in turning the switch on; it is turning it off. The OFF-state switch acts like a capacitor and passes higher frequencies with less attenuation. At 10 MHz, OFF isolation is about -45 dB in  $50-\Omega$  systems, decreasing (approximately 20 dB per decade) as frequency increases. Higher circuit impedances also make OFF isolation decrease. OFF isolation is about 3 dB above that of a bare IC socket, and is due entirely to capacitive coupling.

#### **Test Circuits/Timing Diagrams**

Figure 1. Charge Injection

Figure 2. Switching Times

Figure 3. OFF Isolation and ON Loss

Figure 4. NO, NC, and COM Capacitance

### PACKAGE OPTION ADDENDUM

www.ti.com 16-Apr-2009

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3)  |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|--------------------|

| TS12A4514D       | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4514DBVR    | ACTIVE                | SOT-23          | DBV                | 5    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4514DG4     | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4514DR      | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4514DRG4    | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4514P       | ACTIVE                | PDIP            | Р                  | 8    | 50             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type |

| TS12A4514PE4     | ACTIVE                | PDIP            | Р                  | 8    | 50             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type |

| TS12A4515D       | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4515DBVR    | ACTIVE                | SOT-23          | DBV                | 5    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4515DG4     | ACTIVE                | SOIC            | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4515DR      | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4515DRG4    | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM |

| TS12A4515P       | ACTIVE                | PDIP            | Р                  | 8    | 50             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type |

| TS12A4515PE4     | ACTIVE                | PDIP            | Р                  | 8    | 50             | Pb-Free<br>(RoHS)         | CU NIPDAU        | N / A for Pkg Type |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is

## **PACKAGE OPTION ADDENDUM**

www.ti.com 16-Apr-2009

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

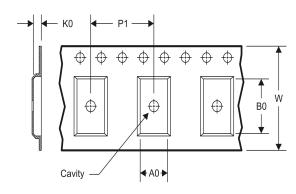

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### TAPE AND REEL INFORMATION

\*All dimensions are nominal

| All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TS12A4514DBVR              | SOT-23          | DBV                | 5 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TS12A4514DR                | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TS12A4515DBVR              | SOT-23          | DBV                | 5 | 3000 | 179.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TS12A4515DR                | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 14-Jul-2012

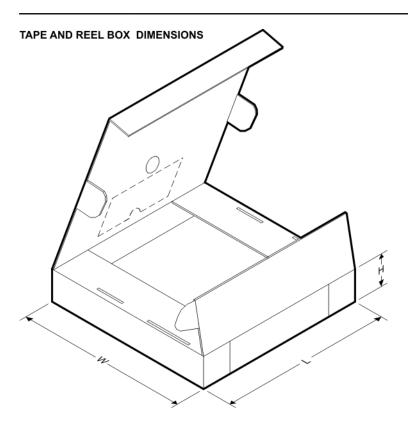

\*All dimensions are nominal

| 7 til diffictionolog are floriffial |              |                    |   |      |             |            |             |

|-------------------------------------|--------------|--------------------|---|------|-------------|------------|-------------|

| Device                              | Package Type | pe Package Drawing |   | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TS12A4514DBVR                       | SOT-23       | DBV                | 5 | 3000 | 203.0       | 203.0      | 35.0        |

| TS12A4514DR                         | SOIC         | D                  | 8 | 2500 | 367.0       | 367.0      | 35.0        |

| TS12A4515DBVR                       | SOT-23       | DBV                | 5 | 3000 | 203.0       | 203.0      | 35.0        |

| TS12A4515DR                         | SOIC         | D                  | 8 | 2500 | 367.0       | 367.0      | 35.0        |

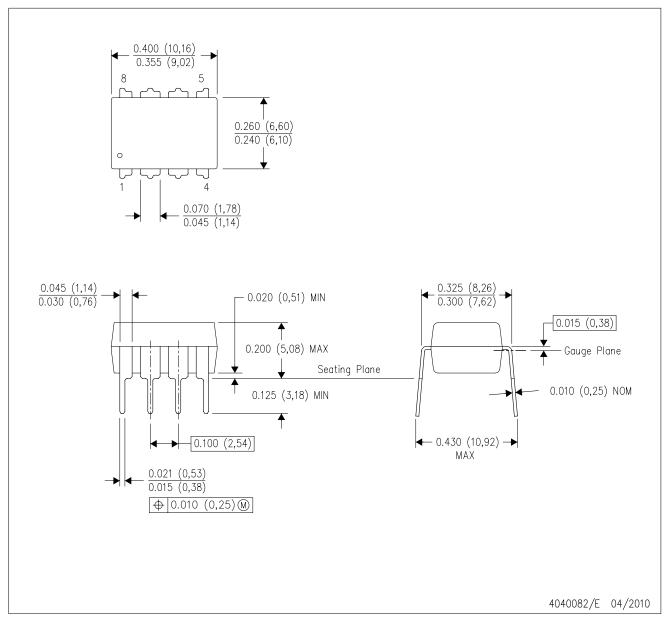

# P (R-PDIP-T8)

## PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

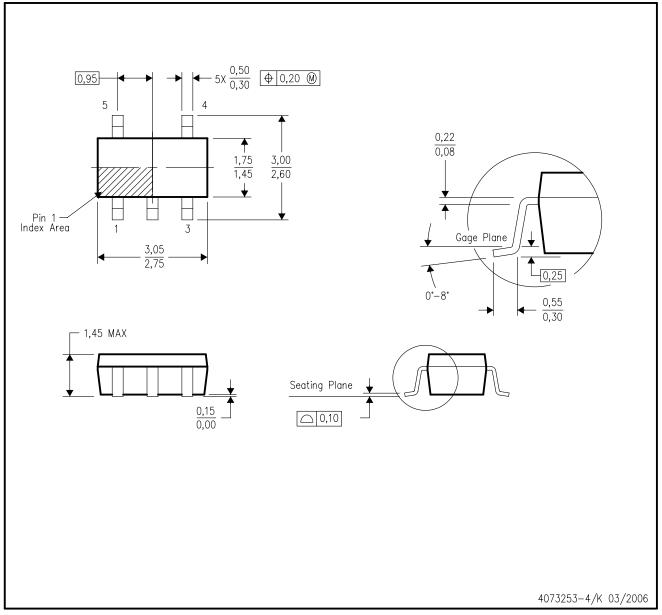

# DBV (R-PDSO-G5)

# PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-178 Variation AA.

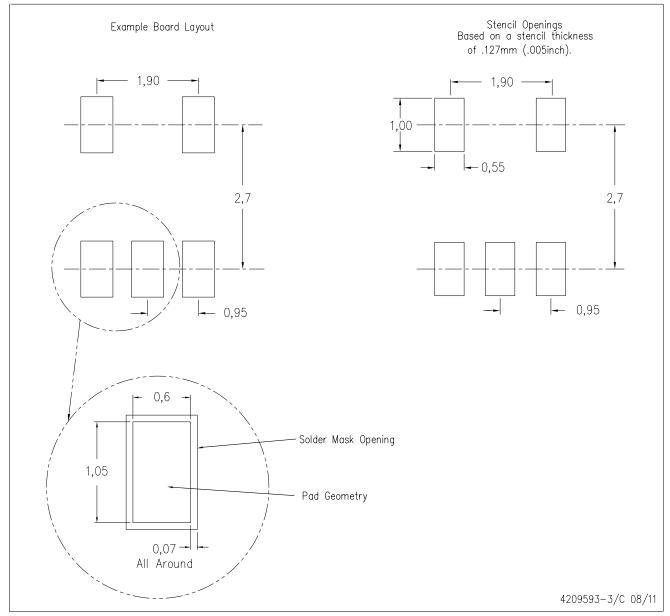

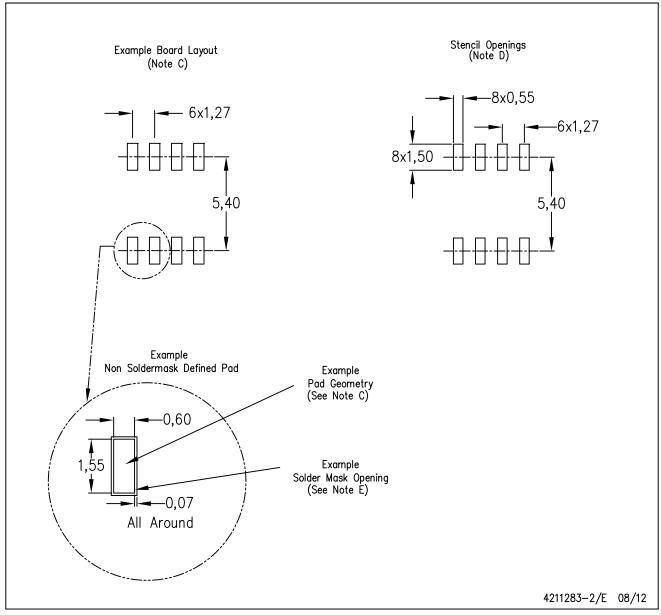

# DBV (R-PDSO-G5)

# PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

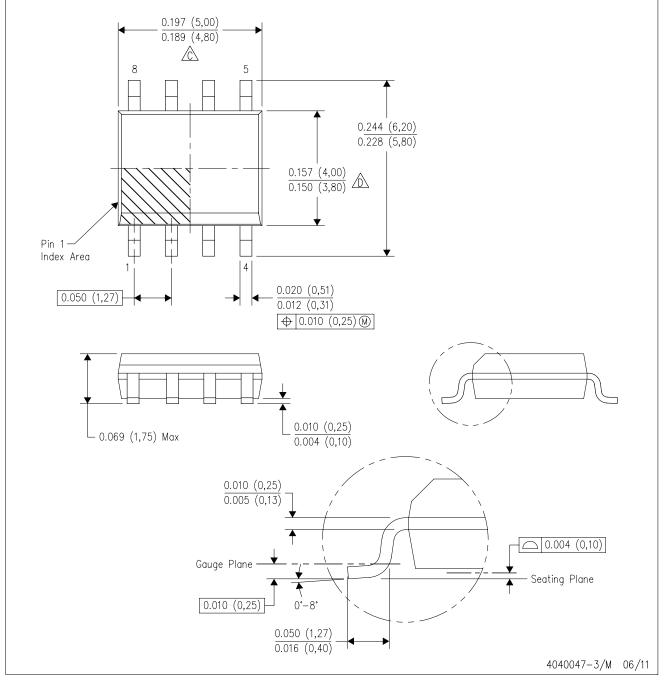

# D (R-PDSO-G8)

### PLASTIC SMALL OUTLINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

# D (R-PDSO-G8)

# PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

#### Products Applications

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers DI P® Products Consumer Electronics www.dlp.com www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy

Clocks and Timers www.ti.com/clocks Industrial www.ti.com/medical Interface interface.ti.com Medical www.ti.com/security

Power Mgmt <u>power.ti.com</u> Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>