# INTEGER-N PLL WITH INTEGRATED VCO

## **FEATURES**

- Fully Integrated VCO

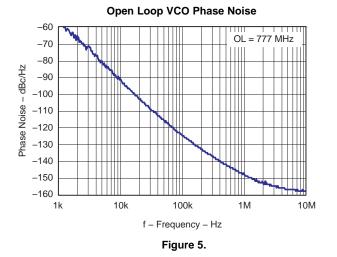

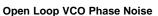

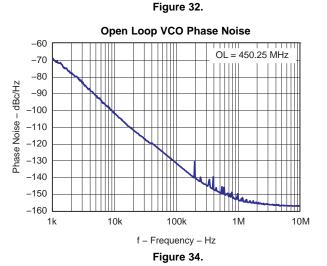

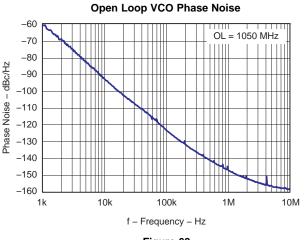

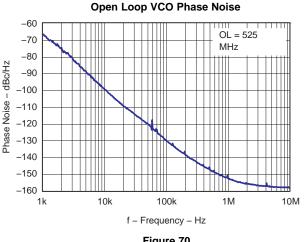

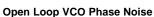

- Low Phase Noise: –137dBc/Hz (at 600kHz, f<sub>vco</sub> of 1.9GHz )

- Low Noise Floor: –158dBc/Hz at 10MHz Offset

- Integer-N PLL

- Input Reference Frequency range: 10MHz to 104MHz

- VCO Frequency Divided by 2-4 Output

- Output Buffer Enable Pin

- Programmable Charge Pump Current

- Hardware and Software Power Down

- 3-Wire Serial Interface

- Single Supply: 4.5V to 5.25V Operation

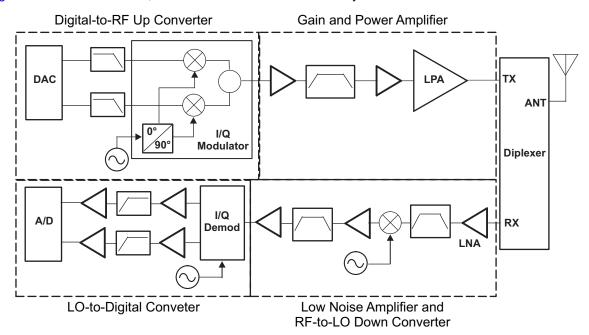

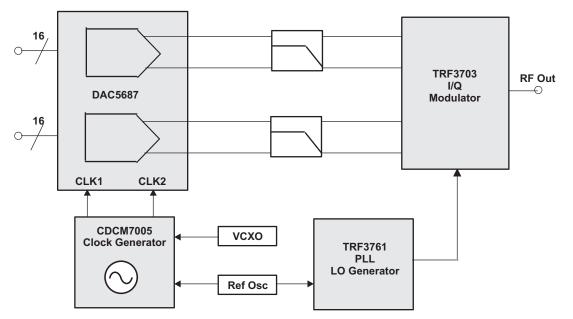

## **APPLICATIONS**

- Wireless Infrastructure

- WCDMA, CDMA, GSM

- Wideband Transceivers

- Wireless Local Loop

- RFID Transceivers

- Clock generation

- IF LO generation

SLWS181H-OCTOBER 2005-REVISED FEBRUARY 2008

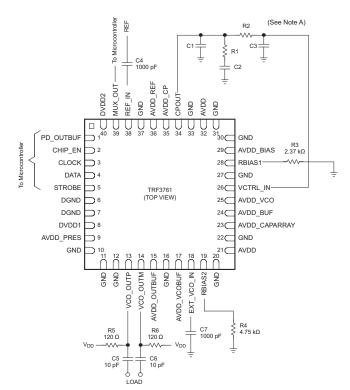

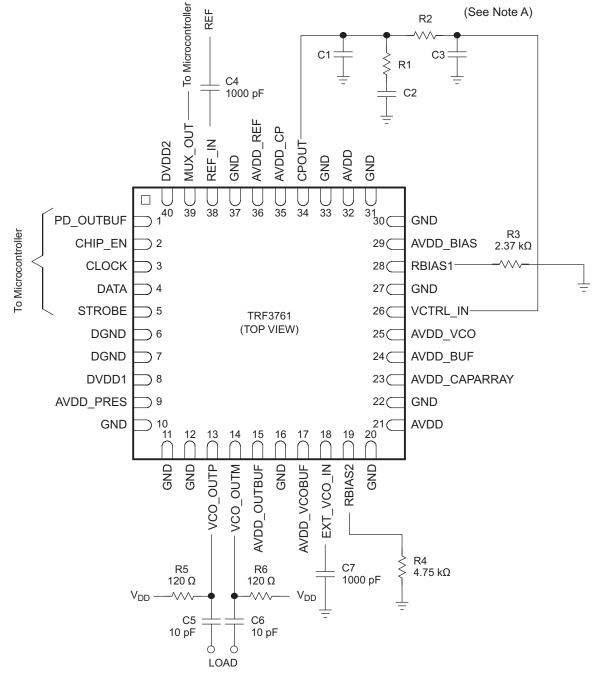

A. See the Application Information section for Loop Filter Design procedures.

#### **AVAILABLE DEVICE OPTIONS**

|             | Div    | Div by 1 |        | by 2   | Div by 4 |        |

|-------------|--------|----------|--------|--------|----------|--------|

| PART NUMBER | Fstart | Fstop    | Fstart | Fstop  | Fstart   | Fstop  |

| TRF3761-A   | 1493   | 1608     | 746.5  | 804    | 373.25   | 402    |

| TRF3761-B   | 1595   | 1711     | 797.5  | 855.5  | 398.75   | 427.75 |

| TRF3761-C   | 1660   | 1790     | 830    | 895    | 415      | 447.5  |

| TRF3761-D   | 1740   | 1866     | 870    | 933    | 435      | 466.5  |

| TRF3761-E   | 1805   | 1936     | 902.5  | 968    | 451.25   | 484    |

| TRF3761-F   | 1850   | 1984     | 925    | 992    | 462.5    | 496    |

| TRF3761-G   | 1920   | 2059     | 960    | 1029.5 | 480      | 514.75 |

| TRF3761-H   | 2028   | 2175     | 1014   | 1087.5 | 507      | 543.75 |

| TRF3761-J   | 2140   | 2295     | 1070   | 1147.5 | 535      | 573.75 |

## DESCRIPTION

TRF3761 is a family of high performance, highly integrated frequency synthesizers, optimized for high performance applications. The TRF3761 includes a low-noise, voltage-controlled oscillator (VCO) and an integer-N PLL.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **DESCRIPTION CONTINUED**

TRF3761 integrates divide-by 1, 2, or 4 options for a more flexible output frequency range. It is controlled through a 3-wire serial-programming-interface (SPI) interface. For power sensitive applications the TRF3761 can be powered down by the SPI interface or externally via chip\_en pin 2.

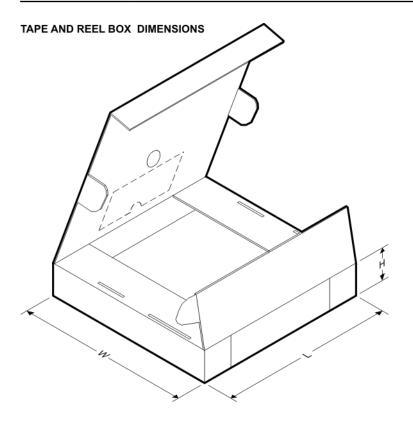

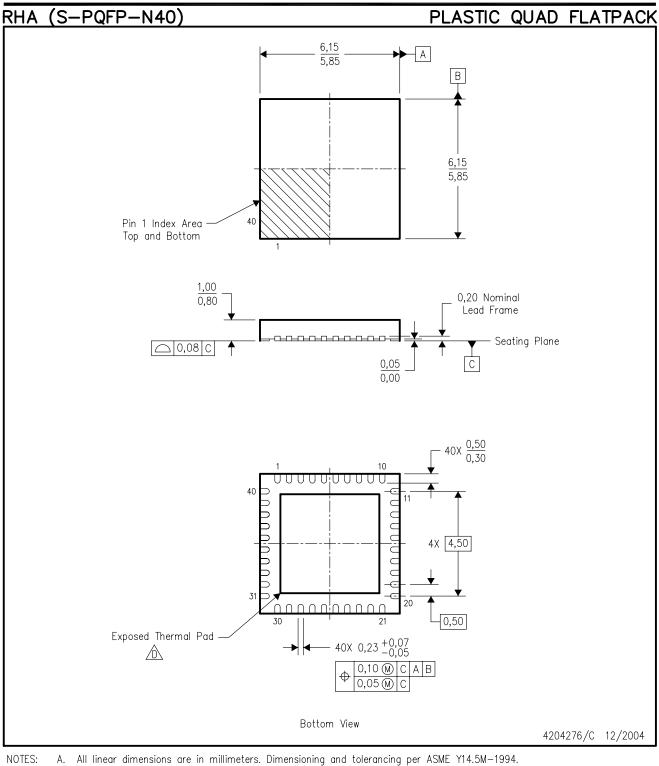

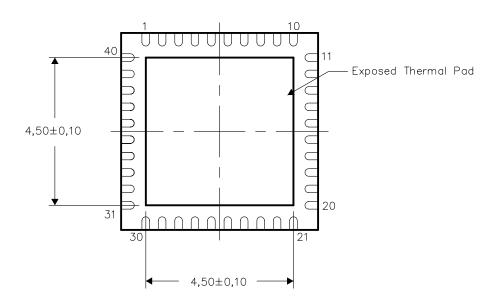

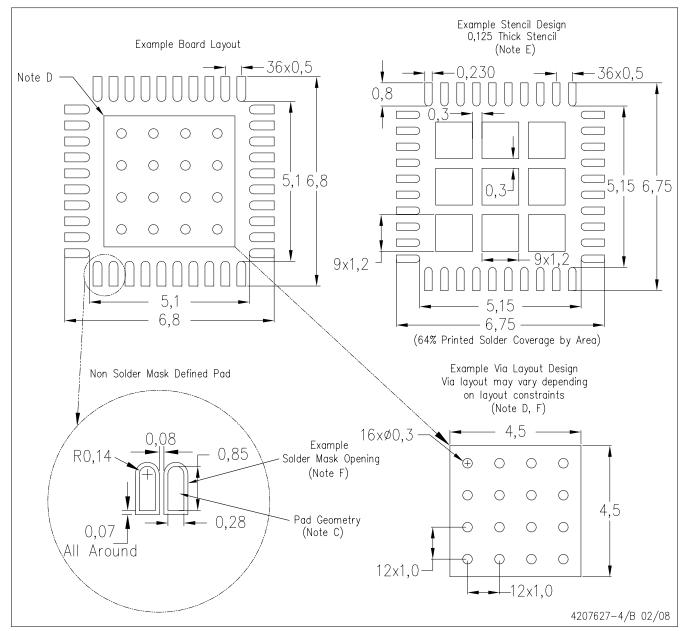

| PRODUCT   | PACKAGE<br>LEAD | PACKAGE<br>DESIGNATOR <sup>(2)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKINGS | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|-----------|-----------------|--------------------------------------|-----------------------------------|---------------------|--------------------|------------------------------|

| TRF3761-A | QFN-40          | RHA                                  | -40°C to 85°C                     | TRF3761-A           | TRF3761-AIRHAR     | Tape and Reel, 2500          |

| IRF3/01-A | QFN-40          | КПА                                  | -40 C 10 65 C                     | IKF3/01-A           | TRF3761-AIRHAT     | Tape and Reel, 250           |

| TRF3761-B | QFN-40          | RHA                                  | –40°C to 85°C                     | TRF3761-B           | TRF3761-BIRHAR     | Tape and Reel, 2500          |

| IKF3/01-D | QFN-40          | КПА                                  | -40°C 10 85°C                     | IKF3/01-D           | TRF3761-BIRHAT     | Tape and Reel, 250           |

| TRF3761-C | QFN-40          | RHA                                  | –40°C to 85°C                     | TRF3761-C           | TRF3761-CIRHAR     | Tape and Reel, 2500          |

| IKF3/01-C | QFN-40          | КПА                                  | -40°C 10 85°C                     | IKF3/01-C           | TRF3761-CIRHAT     | Tape and Reel, 250           |

| TRF3761-D | QFN-40          | RHA                                  | -40°C to 85°C                     | TRF3761-D           | TRF3761-DIRHAR     | Tape and Reel, 2500          |

| IKF3/01-D | QFN-40          | КПА                                  | -40°C 10 85°C                     | IKF3/01-D           | TRF3761-DIRHAT     | Tape and Reel, 250           |

| TRF3761-E | QFN-40          | RHA                                  | -40°C to 85°C                     | TRF3761-E           | TRF3761-EIRHAR     | Tape and Reel, 2500          |

| IRF3/01-E | QFN-40          | КПА                                  | -40°C 10 85°C                     | IKF3/01-E           | TRF3761-EIRHAT     | Tape and Reel, 250           |

| TRF3761-F | QFN-40          | RHA                                  | -40°C to 85°C                     | TRF3761-F           | TRF3761-FIRHAR     | Tape and Reel, 2500          |

| IKF3/01-F | QFN-40          | КПА                                  | -40°C 10 85°C                     | IKF3/01-F           | TRF3761-FIRHAT     | Tape and Reel, 250           |

|           |                 | DUA                                  | 4000 to 0500                      | TDE0704 0           | TRF3761-GIRHAR     | Tape and Reel, 2500          |

| TRF3761-G | QFN-40          | RHA                                  | –40°C to 85°C                     | TRF3761-G           | TRF3761-GIRHAT     | Tape and Reel, 250           |

|           |                 | DUA                                  | 4000 to 0500                      |                     | TRF3761-HIRHAR     | Tape and Reel, 2500          |

| TRF3761-H | QFN-40          | RHA                                  | –40°C to 85°C                     | TRF3761-H           | TRF3761-HIRHAT     | Tape and Reel, 250           |

|           |                 | RHA                                  | 40°C to 95°C                      |                     | TRF3761-JIRHAR     | Tape and Reel, 2500          |

| TRF3761-J | QFN-40          | КПА                                  | –40°C to 85°C                     | TRF3761-J           | TRF3761-JIRHAT     | Tape and Reel, 250           |

## PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

(2) Thermal pad size:  $177 \times 177$  mils.

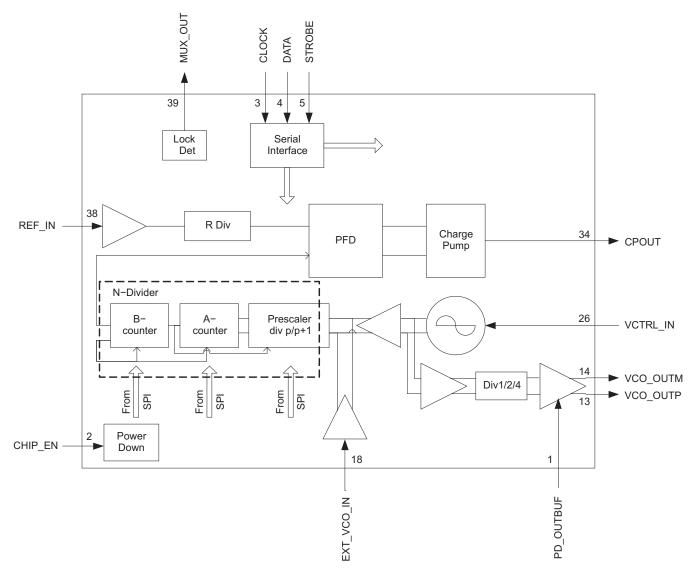

**Functional Block Diagram**

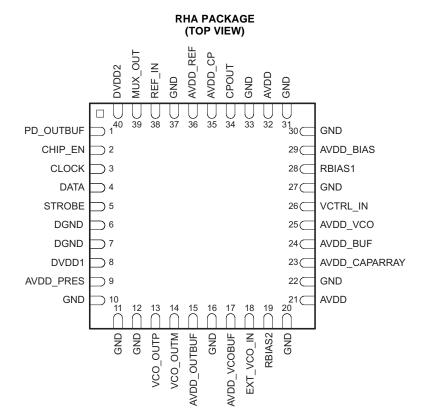

#### **TERMINAL FUNCTIONS**

| TERMIN      | NAL <sup>(1)</sup> | 1/0 | DECODIDION                                                                                                                                        |

|-------------|--------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                |     | DESCRIPTION                                                                                                                                       |

| PD_OUTBUF   | 1                  | I   | Once configured in register 1, this pin will control the output buffer. Logic level 0 turns on the buffer and logic level 1 turns off the buffer. |

| CHIP_EN     | 2                  | I   | This pin requires 4.5 to $5.25v$ applied for normal operation. Grounding this pin will disable the chip.                                          |

| CLOCK       | 3                  | I   | Serial-programming-interface clock                                                                                                                |

| DATA        | 4                  | I/O | Serial-programming-interface data, used for programming the frequency and other features.                                                         |

| STROBE      | 5                  | I   | Serial-programming-interface strobe required to write the data to the chip                                                                        |

| DGND        | 6, 7               |     | Digital ground                                                                                                                                    |

| DVDD1       | 8                  |     | Digital power supply, requires 4.5 to 5.25 V, Suggested decoupling, 0.1uF and 10pF capacitors in parallel.                                        |

| AVDD_PRES   | 9                  |     | Power supply for prescaler circuit, requires 4.5 to 5.25 V, Suggested decoupling, 0.1uF and 10pF capacitors in parallel.                          |

| VCO_OUTP    | 13                 | 0   | VCO output, can be used single ended matched to 50 ohms or in conjuction with VCO_OUTM (pin 14) with a balun.                                     |

| VCO_OUTM    | 14                 | 0   | VCO output, can be used single ended matched to 50 ohms or in conjunction with VCO_OUTP (pin 13) with a balun.                                    |

| AVDD_OUTBUF | 15                 |     | Power supply for output buffers, requires 4.5 to 5.25 V, Suggested decoupling, 0.1µF and 10pF capacitors in parallel.                             |

| AVDD_VCOBUF | 17                 |     | Power supply for VCO buffers, requires 4.5 to 5.25 V, Suggested decoupling, 0.1µF and 10pF capacitors in parallel.                                |

| EXT_VCO_IN  | 18                 | I   | External VCO input to prescaler, If using an external VCO instead of the internal VCO.                                                            |

(1) Power Supply=V<sub>CC</sub>=(DVDD1, AVDD1, AVDD\_PRES, AVDD\_VCOBUF, AVDD, AVDD\_CAPARRAY, AVDD\_BUF, AVDD\_VCO, AVDD\_BIAS, AVDD\_CP, AVDD\_REF, DVDD2)

#### **TERMINAL FUNCTIONS (continued)**

| TERMINAL <sup>(1)</sup> |                                               | I/O | DESCRIPTION                                                                                                                       |

|-------------------------|-----------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME                    | NO.                                           | 1/0 | DESCRIPTION                                                                                                                       |

| RBIAS2                  | 19                                            | I/O | External bias resistor for setting the internal reference current requires a 4.75K ohm resister to ground.                        |

| AVDD                    | 21                                            |     | Analog power supply, requires 4.5 to 5.25 V, Suggested decoupling, 0.1uF and $10\mu F$ capacitors in parallel.                    |

| AVDD_CAPARRAY           | 23                                            |     | Power supply for VCO core and buffer, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu F$ and 10pF capacitors in parallel.   |

| AVDD_BUF                | 24                                            |     | Power supply for VCO core and buffer, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu F$ and 10pF capacitors in parallel.   |

| AVDD_VCO                | 25                                            |     | Power supply for VCO core and buffer, requires 4.5 to 5.25 V, Suggested decoupling, 0.1uF and 10pF capacitors in parallel.        |

| VCTRL_IN                | 26                                            | I   | VCO control voltage, the output of the loop filter is applied to this pin.                                                        |

| RBIAS1                  | 28                                            | I/O | External bias resistor for setting charge pump reference current, requires 2.37K ohm resistor to ground.                          |

| AVDD_BIAS               | 29                                            |     | Power supply for band gap current bias, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu$ F and 10pF capacitors in parallel. |

| GND                     | 10, 11, 12, 16, 20, 22,<br>27, 30, 31, 33, 37 |     | Analog ground                                                                                                                     |

| AVDD                    | 32                                            |     | Power supply for FUSE cell, requires 4.5 to 5.25V. Suggested decoupling, 0.1 $\mu$ F, 1nF and 1pF capacitors in parallel.         |

| CPOUT                   | 34                                            | 0   | Charge pump output, connected to the input of loop filter.                                                                        |

| AVDD_CP                 | 35                                            |     | Analog power supply for charge pump, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu$ F and 10pF capacitors in parallel     |

| AVDD_REF                | 36                                            |     | Power supply for REF_IN circuitry, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu F$ and 10pF capacitors in parallel.      |

| REF_IN                  | 38                                            | Ι   | Reference signal input, reference oscillator input of 10MHz to 104MHz.                                                            |

| MUX_OUT                 | 39                                            | 0   | Generally used for digital lock detect, can be used to verify locked condition by microcontroller, high = locked, low = unlocked. |

| DVDD2                   | 40                                            |     | Power supply for the digital regulator, requires 4.5 to 5.25 V, Suggested decoupling, $0.1\mu$ F and 10pF capacitors in parallel. |

## THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|               | PARAMETER <sup>(1)</sup>              | TEST CONDITIONS                | MIN | TYP  | MAX | UNIT |

|---------------|---------------------------------------|--------------------------------|-----|------|-----|------|

|               |                                       | Soldered slug, no airflow      |     | 26   |     | °C/W |

| $\theta_{JA}$ | Thermal derating, junction-to-ambient | Soldered slug, 200-LFM airflow |     | 20.1 |     | °C/W |

|               |                                       | Soldered slug, 400-LFM airflow |     | 17.4 |     | °C/W |

(1) Determined using JEDEC standard JESD-51 with High K board

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                              | VALUE                        | UNIT |

|------------------|----------------------------------------------|------------------------------|------|

|                  | Supply voltage range <sup>(2)</sup>          | -0.3 to 5.5                  | V    |

|                  | Digital I/O voltage range                    | –0.3 to V <sub>CC</sub> +0.3 | V    |

| $T_{J}$          | Operating virtual junction temperature range | -40 to 150                   | °C   |

| T <sub>stg</sub> | Storage temperature range                    | -65 to 150                   | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

# **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted)

|                 |                                              | MIN | NOM | MAX  | UNIT         |

|-----------------|----------------------------------------------|-----|-----|------|--------------|

| V <sub>CC</sub> | Power supply voltage                         | 4.5 | 5   | 5.25 | V            |

|                 | Power supply voltage ripple                  |     |     | 940  | $\mu V_{pp}$ |

| T <sub>A</sub>  | Operating free air temperature range         | -40 |     | 85   | °C           |

| TJ              | Operating virtual junction temperature range | -40 |     | 150  | °C           |

# **ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 4.5V to 5.25V,  $T_A$  = -40 to 85 °C (unless otherwise noted)

|                  | PARAMETER                                  |                       | TEST CONDITIONS    | MIN                | TYP | MAX         | UNIT            |

|------------------|--------------------------------------------|-----------------------|--------------------|--------------------|-----|-------------|-----------------|

| DC P             | arameters                                  |                       |                    | i.                 |     |             |                 |

|                  |                                            |                       | Divide by 1 output |                    | 130 |             | mA              |

| I <sub>CC</sub>  | Total supply current                       | T <sub>A</sub> = 25°C | Divide by 2 output |                    | 140 |             | mA              |

|                  |                                            |                       | Divide by 4 output |                    | 150 |             | mA              |

| Refer            | rence Oscillator Parameters                |                       | ·                  | i                  |     |             |                 |

| f <sub>ref</sub> | Reference frequency                        |                       |                    | 10                 |     | 104         | MHz             |

|                  | Reference input sensitivity (REF_IN)       |                       |                    | 0.2                |     | 2.5         | V <sub>PP</sub> |

|                  |                                            | Parallel capa         | acitance           |                    | 5   | 6.52        | pF              |

|                  | Reference input impedance (REF_IN)         | Parallel resis        | stance             | 3913               |     |             | Ω               |

| PFD              | Charge Pump                                |                       |                    | i.                 |     |             |                 |

|                  | PFD frequency                              |                       |                    |                    |     | 30          | MHz             |

|                  | Charge pump current (I <sub>CP_OUT</sub> ) | SPI program           | mable              |                    | 5.6 |             | mA              |

| Digita           | al Interface (PD_OUTBUF, CHIP_EN, C        | LOCK, DATA            | , STROBE)          | i.                 |     |             |                 |

| VIH              | High-level input voltage                   |                       |                    | 2.5                |     | $V_{CC}$    | V               |

| V <sub>IL</sub>  | Low-level input voltage                    |                       |                    | 0                  |     | 0.8         | V               |

| V <sub>OH</sub>  | High-level output voltage                  |                       |                    | 0.8V <sub>CC</sub> |     |             | V               |

| V <sub>OL</sub>  | Low-level output voltage                   |                       |                    |                    |     | $0.2V_{CC}$ | V               |

| Outp             | ut Power                                   |                       |                    | L.                 |     |             |                 |

|                  | Single ended                               |                       |                    |                    | 0   |             | dBm             |

|                  | Differential                               |                       |                    |                    | 3   |             | dBm             |

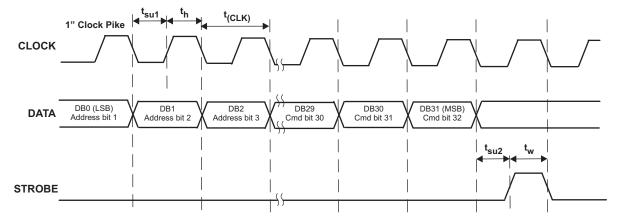

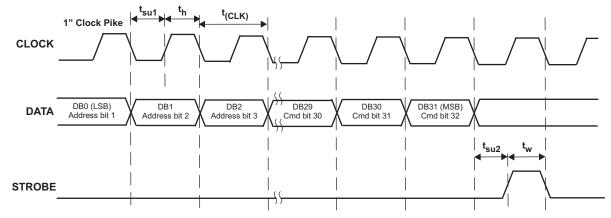

## TIMING REQUIREMENTS

Supply voltage =  $V_{CC}$  = 4.5V to 5.25V,  $T_{A}$  = –40 to 85  $^{\circ}C$

|                    | PARAMETER           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|---------------------|-----------------|-----|-----|-----|------|

| t <sub>(CLK)</sub> | Clock period        |                 | 50  |     |     | ns   |

| t <sub>su1</sub>   | Setup time, data    |                 | 10  |     |     | ns   |

| t <sub>h</sub>     | Hold time, data     |                 | 10  |     |     | ns   |

| tw                 | Pulse width, STROBE |                 | 20  |     |     | ns   |

| t <sub>su2</sub>   | Setup time, STROBE  |                 | 10  |     |     | ns   |

A. The first 4 bits, DB(3-0), of data are Address bits. The 28 remaining bits, DB(31-4), are part of the command. The command is little endian or lower bits first.

## Figure 1. Serial Programming Timing Diagram

# **TRF3761-A ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST C                                                     | ONDITIONS     | MIN TYP MA | K UNIT  |

|------------------------------------------------------------------------------|------------------------------------------------------------|---------------|------------|---------|

| OISE CHARACTERISTICS                                                         |                                                            |               |            |         |

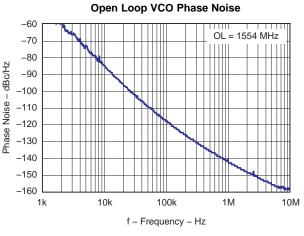

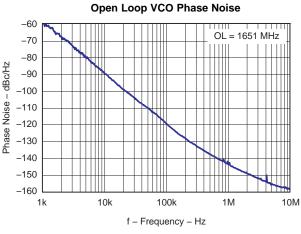

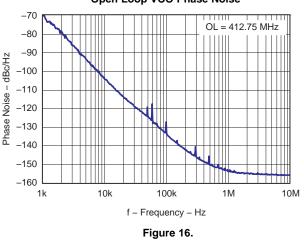

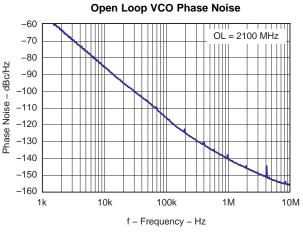

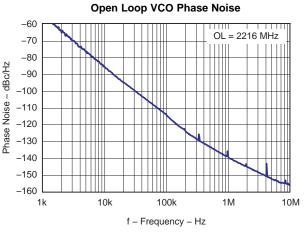

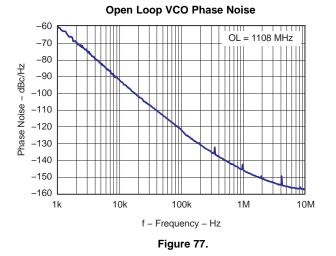

|                                                                              |                                                            | 100kHz offset | -119.34    |         |

|                                                                              |                                                            | 600kHz offset | -139       |         |

| VCO phase noise,<br>Free running VCO direct output                           | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 1651MHz    | 1MHz offset   | -142.1     | dBc/H   |

|                                                                              | 10 - 103 10112                                             | 6MHz offset   | -156.6     |         |

|                                                                              |                                                            | 10MHz offset  | -158.6     |         |

|                                                                              |                                                            | 100kHz offset | -127.8     |         |

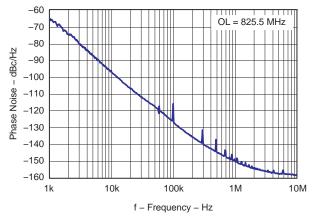

|                                                                              |                                                            | 600kHz offset | -146.5     |         |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 825.5 MHz  | 1MHz offset   | -149       | dBc/H   |

|                                                                              | 10 = 023.3 WI 12                                           | 6MHz offset   | -156.2     |         |

|                                                                              |                                                            | 10MHz offset  | -158.4     |         |

|                                                                              |                                                            | 100kHz offset | -127.3     |         |

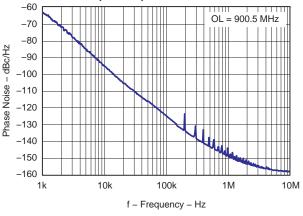

|                                                                              |                                                            | 600kHz offset | -151.4     |         |

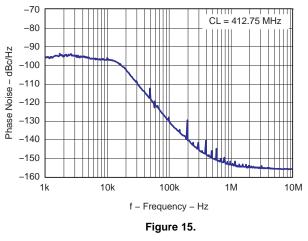

| VCO phase noise,<br>Free running VCO divide by 4 output                      | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 412.75 MHz | 1MHz offset   | -153       | dBc/H   |

| Free running VCO divide-by-4 output                                          |                                                            | 6MHz offset   | -155.5     |         |

|                                                                              |                                                            | 10MHz offset  | -155.9     |         |

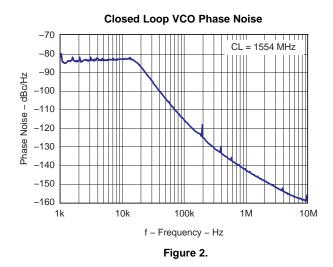

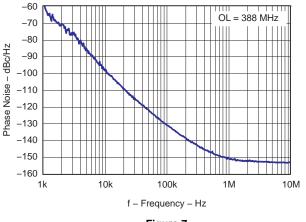

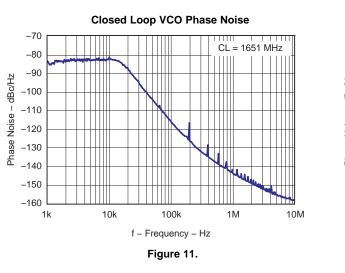

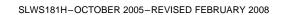

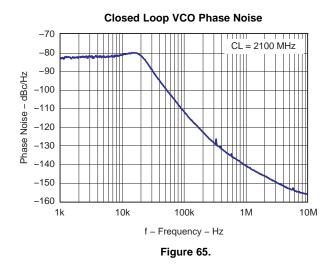

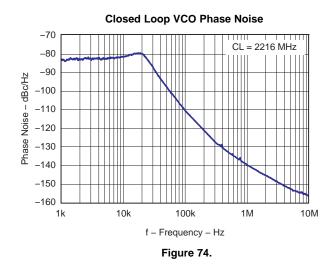

|                                                                              | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 1651MHz    | 1kHz offset   | -83.5      |         |

| VCO phase noise,                                                             |                                                            | 600kHz offset | -138       |         |

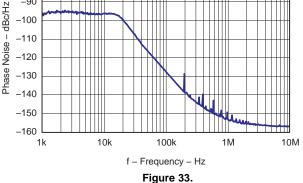

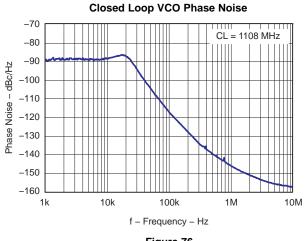

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   |                                                            | 1MHz offset   | -141.8     | dBc/H   |

|                                                                              |                                                            | 10MHz offset  | -158.2     |         |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                             |               | 0.85°      |         |

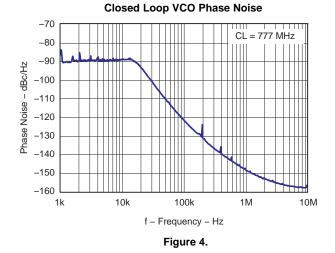

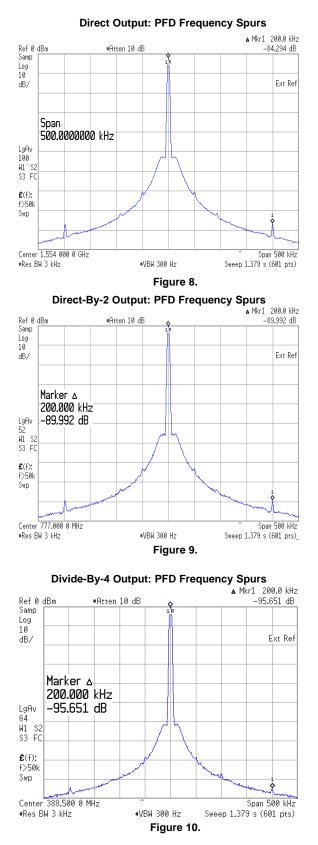

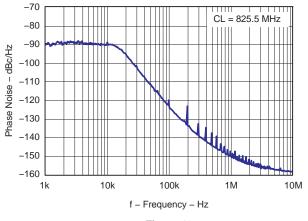

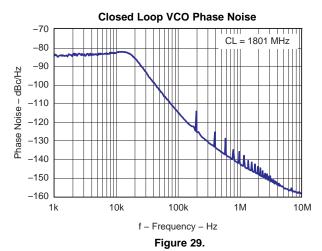

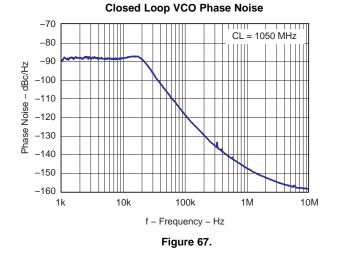

|                                                                              |                                                            | 1kHz offset   | -90.2      |         |

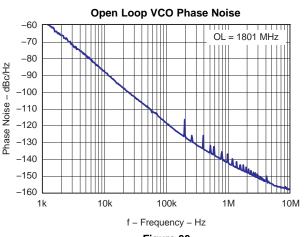

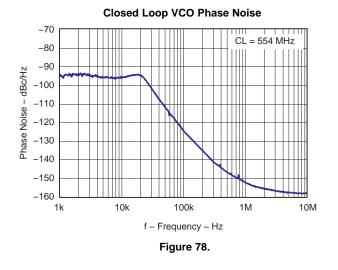

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1651MHz,                                | 600kHz offset | -146       |         |

| Closed loop phase noise divide-by-2 $output^{(4)(2)(3)}$                     | f <sub>O</sub> = 825.5 MHz                                 | 1MHz offset   | -147.39    | dBc/H   |

|                                                                              |                                                            | 10MHz offset  | -158.25    |         |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.53°      |         |

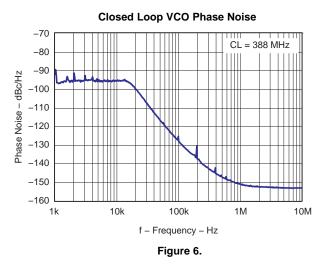

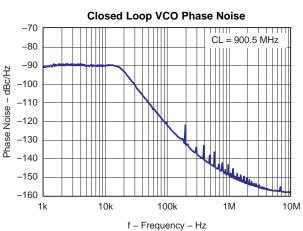

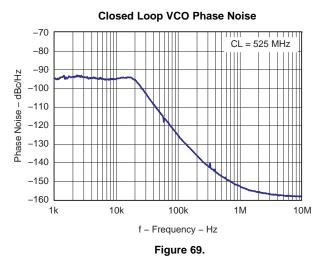

|                                                                              |                                                            | 1kHz offset   | -95.7      |         |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1651MHz,                                | 600kHz offset | -151       | ۱D - // |

| Closed loop phase noise divide-by-4 $output^{(1)(2)(3)}$                     | f <sub>O</sub> = 412.75 MHz                                | 1MHz offset   | -154       | dBc/H   |

|                                                                              |                                                            | 10MHz offset  | -156       |         |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.33°      |         |

| VCO gain, Kv                                                                 | VCO free running                                           |               | 23         | MHz/    |

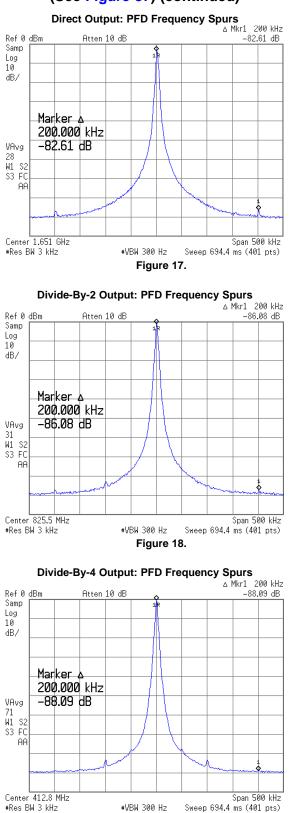

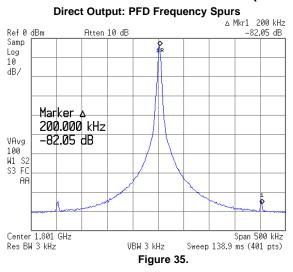

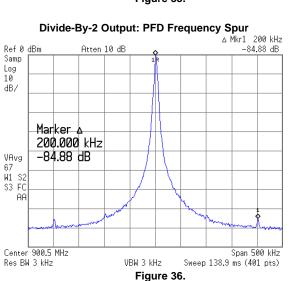

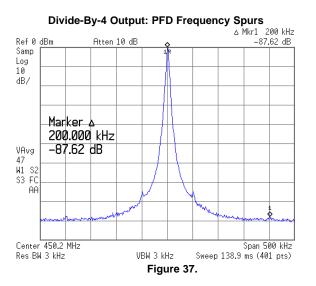

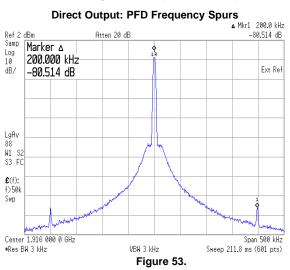

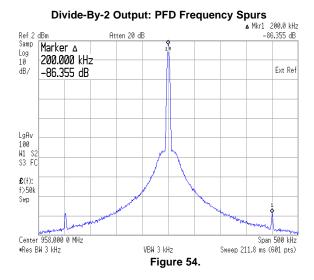

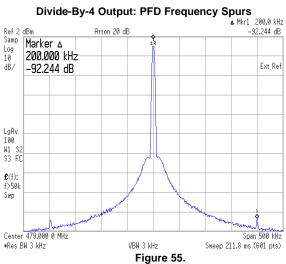

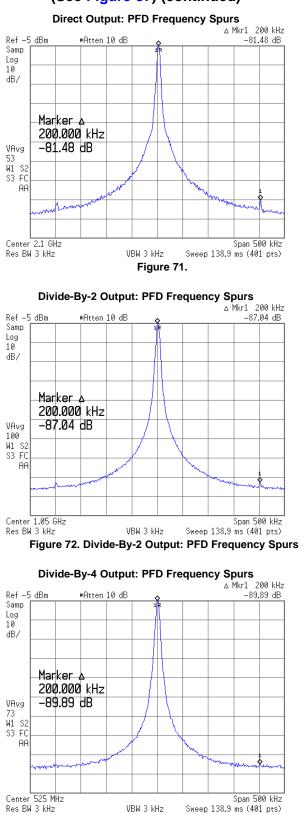

| Reference spur <sup>(2)</sup>                                                |                                                            |               | -80        | dBc     |

See Application Circuit Figure 87.

PFD = 200kHz, Loop Filter BW = 15kHz, Output frequency step = 200kHz.

Reference oscillator RMS phase error = 0.008250°, RMS jitter = 881.764 fs.

See Application Circuit Figure 87.

## **TRF3761-B ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST C                                                     | ONDITIONS     | MIN TYP MAX | UNIT        |

|------------------------------------------------------------------------------|------------------------------------------------------------|---------------|-------------|-------------|

| IOISE CHARACTERISTICS                                                        |                                                            |               |             |             |

|                                                                              |                                                            | 100kHz offset | -119.34     |             |

|                                                                              |                                                            | 600kHz offset | -139        | Ī           |

| VCO phase noise,<br>Free running VCO direct output                           | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 1651MHz    | 1MHz offset   | -142.1      | dBc/H       |

|                                                                              | 10 - 100 100 12                                            | 6MHz offset   | -156.6      | Ī           |

|                                                                              |                                                            | 10MHz offset  | -158.6      | Ī           |

|                                                                              |                                                            | 100kHz offset | -127.8      |             |

|                                                                              |                                                            | 600kHz offset | -146.5      | +           |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 825.5 MHz  | 1MHz offset   | -149        | dBc/H       |

|                                                                              | 10 - 023.3 10112                                           | 6MHz offset   | -156.2      | +           |

|                                                                              |                                                            | 10MHz offset  | -158.4      | -           |

|                                                                              |                                                            | 100kHz offset | -127.3      |             |

|                                                                              |                                                            | 600kHz offset | -151.4      | 1           |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 412.75 MHz | 1MHz offset   | -153        | dBc/Hz      |

|                                                                              |                                                            | 6MHz offset   | -155.5      |             |

|                                                                              |                                                            | 10MHz offset  | -155.9      | 1           |

|                                                                              | f <sub>VCO</sub> = 1651MHz,<br>f <sub>O</sub> = 1651MHz    | 1kHz offset   | -83.5       |             |

| VCO phase noise.                                                             |                                                            | 600kHz offset | -138        |             |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   |                                                            | 1MHz offset   | -141.8      | dBc/H       |

|                                                                              |                                                            | 10MHz offset  | -158.2      | Ť           |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                             |               | 0.85°       |             |

|                                                                              |                                                            | 1kHz offset   | -90.2       |             |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1651MHz,                                | 600kHz offset | -146        | . ID . // I |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 825.5 MHz                                 | 1MHz offset   | -147.39     | dBc/H       |

|                                                                              |                                                            | 10MHz offset  | -158.25     | İ           |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.53°       |             |

|                                                                              |                                                            | 1kHz offset   | -95.7       |             |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1651MHz,                                | 600kHz offset | -151        | -/D - // /  |

| Closed loop phase noise divide-by-4 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 412.75 MHz                                | 1MHz offset   | -154        | dBc/H       |

|                                                                              |                                                            | 10MHz offset  | -156        | Ī           |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.33°       |             |

| VCO gain, Kv                                                                 | VCO free running                                           |               | 23          | MHz/        |

| Reference spur <sup>(2)</sup>                                                |                                                            |               | -80         | dBc         |

See Application Circuit Figure 87.

PFD = 200kHz, Loop Filter BW = 15kHz, Output frequency step = 200kHz.

Reference oscillator RMS phase error = 0.008250°, RMS jitter = 881.764 fs.

# **TRF3761-C ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST C                                                     | ONDITIONS     | MIN TYP MAX | UNIT   |

|------------------------------------------------------------------------------|------------------------------------------------------------|---------------|-------------|--------|

| DISE CHARACTERISTICS                                                         |                                                            |               |             |        |

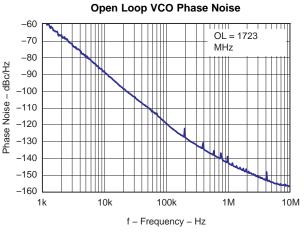

|                                                                              |                                                            | 100kHz offset | -119.5      |        |

|                                                                              |                                                            | 600kHz offset | -138.8      |        |

| VCO phase noise,<br>Free running VCO direct output                           | $f_{VCO} = 1723MHz,$<br>$f_{O} = 1700MHz$                  | 1MHz offset   | -143.9      | dBc/H  |

|                                                                              |                                                            | 6MHz offset   | -155.3      |        |

|                                                                              |                                                            | 10MHz offset  | -157.5      |        |

|                                                                              |                                                            | 100kHz offset | -126        |        |

|                                                                              |                                                            | 600kHz offset | -145.2      |        |

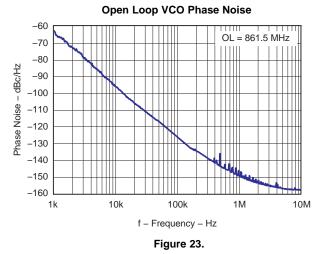

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1723MHz,<br>f <sub>O</sub> = 861.5 MHz  | 1MHz offset   | -149.5      | dBc/H  |

|                                                                              | 10 - 00 1.0 10112                                          | 6MHz offset   | -157.2      |        |

|                                                                              |                                                            | 10MHz offset  | -158        |        |

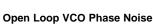

|                                                                              |                                                            | 100kHz offset | -133        |        |

|                                                                              |                                                            | 600kHz offset | -151        | -      |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      | f <sub>VCO</sub> = 1723MHz,<br>f <sub>O</sub> = 430.75 MHz | 1MHz offset   | -153.8      | dBc/H  |

|                                                                              | 1 <sub>0</sub> = 430.73 MHZ                                | 6MHz offset   | -156        |        |

|                                                                              |                                                            | 10MHz offset  | -156.5      | -      |

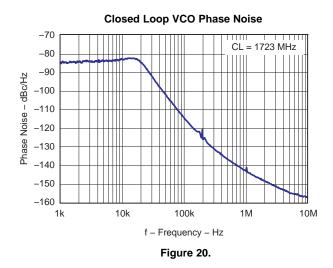

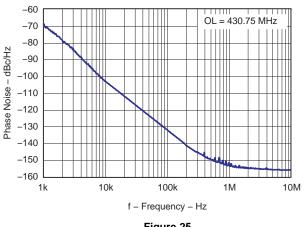

|                                                                              | f <sub>VCO</sub> = 1723MHz,<br>f <sub>O</sub> = 1723MHz,   | 1kHz offset   | -85         |        |

| VCO phase noise,                                                             |                                                            | 600kHz offset | -138.34     | dBc/ł  |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   |                                                            | 1MHz offset   | -142.68     |        |

|                                                                              |                                                            | 10MHz offset  | -157.3      |        |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                             |               | 0.87°       |        |

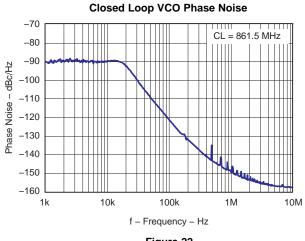

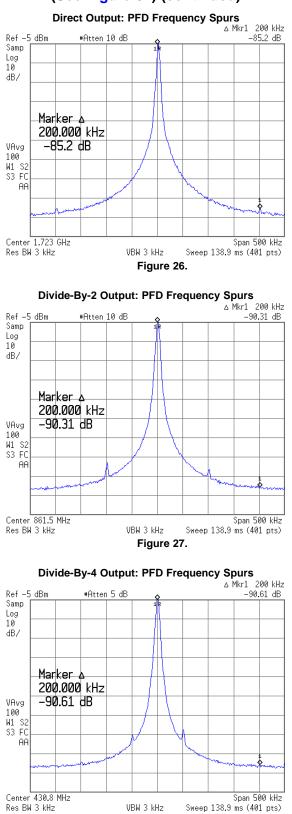

|                                                                              |                                                            | 1kHz offset   | -90.1       |        |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1723MHz,                                | 600kHz offset | -145        | dD o/l |

| Closed loop phase noise divide-by-2 $output^{(1)(2)(3)}$                     | f <sub>O</sub> = 861.5 MHz                                 | 1MHz offset   | -148.6      | dBc/ŀ  |

|                                                                              |                                                            | 10MHz offset  | -158        |        |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.53°       |        |

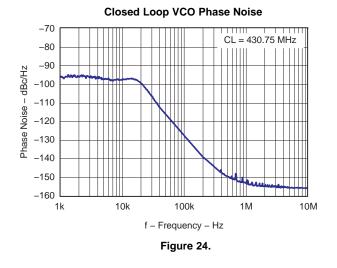

|                                                                              |                                                            | 1kHz offset   | -96.2       |        |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1723MHz,                                | 600kHz offset | -151        | dBc/l  |

| Closed loop phase noise divide-by-4 $output^{(1)(2)(3)}$                     | f <sub>O</sub> = 430.75 MHz                                | 1MHz offset   | -153        | UDC/F  |

|                                                                              |                                                            | 10MHz offset  | -156        |        |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                             |               | 0.33°       |        |

| VCO gain, Kv                                                                 | VCO free running                                           |               | 23          | MHz/   |

| Reference spur <sup>(2)</sup>                                                |                                                            |               | -80         | dBc    |

(1)

## **TRF3761-D ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    |                                                           |               |        |            |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|--------|------------|--|

| IOISE CHARACTERISTICS                                                        |                                                           |               |        |            |  |

|                                                                              |                                                           | 100kHz offset | -118   |            |  |

|                                                                              |                                                           | 600kHz offset | -138.5 |            |  |

| VCO phase noise,<br>Free running VCO direct output                           | f <sub>VCO</sub> = 1817MHz,<br>f <sub>O</sub> = 1817MHz   | 1MHz offset   | -144   | dBc/Hz     |  |

|                                                                              |                                                           | 6MHz offset   | -156   |            |  |

|                                                                              |                                                           | 10MHz offset  | -158   |            |  |

|                                                                              |                                                           | 100kHz offset | -124.8 |            |  |

|                                                                              |                                                           | 600kHz offset | -145.2 |            |  |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1817MHz,<br>f <sub>O</sub> = 908.5MHz  | 1MHz offset   | -148   | dBc/H      |  |

|                                                                              |                                                           | 6MHz offset   | -157.8 |            |  |

|                                                                              |                                                           | 10MHz offset  | -158.2 |            |  |

|                                                                              |                                                           | 100kHz offset | -132   |            |  |

|                                                                              |                                                           | 600kHz offset | -151   |            |  |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      | f <sub>VCO</sub> = 1817MHz,<br>f <sub>O</sub> = 454.25MHz | 1MHz offset   | -154   | dBc/H      |  |

|                                                                              |                                                           | 6MHz offset   | -157   |            |  |

|                                                                              |                                                           | 10MHz offset  | -157.5 |            |  |

|                                                                              |                                                           | 1kHz offset   | -85    |            |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1817MHz,                               | 600kHz offset | -139   | -1D - /1 1 |  |

| Closed loop phase noise direct $output^{(1)(2)(1)}$                          | f <sub>O</sub> = 1817MHz                                  | 1MHz offset   | -144   | dBc/H      |  |

|                                                                              |                                                           | 10MHz offset  | -159   |            |  |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                            |               | 0.85°  |            |  |

|                                                                              |                                                           | 1kHz offset   | -91    |            |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1817MHz,                               | 600kHz offset | -146   | 1          |  |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 908.5MHz                                 | 1MHz offset   | -149   | dBc/H      |  |

|                                                                              |                                                           | 10MHz offset  | -159   |            |  |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.47°  |            |  |

|                                                                              |                                                           | 1kHz offset   | -97    |            |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1817MHz,                               | 600kHz offset | -151   | dDa/U      |  |

| Closed loop phase noise divide-by-4 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 454.25MHz                                | 1MHz offset   | -154   | dBc/⊦      |  |

| •                                                                            |                                                           | 10MHz offset  | -157   |            |  |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.34°  |            |  |

| VCO gain, Kv                                                                 | VCO free running                                          |               | 23     | MHz/       |  |

| Reference spur <sup>(2)</sup>                                                |                                                           |               | -80    | dBc        |  |

# **TRF3761-E ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST C                                                    | ONDITIONS     | MIN TYP MAX | ( UNIT  |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------|---------|--|

| IOISE CHARACTERISTICS                                                        |                                                           |               |             |         |  |

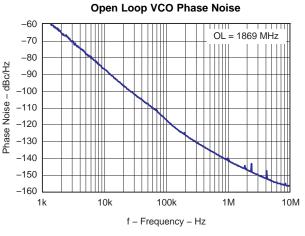

|                                                                              |                                                           | 100kHz offset | -118        |         |  |

|                                                                              |                                                           | 600kHz offset | -138        |         |  |

| VCO phase noise,<br>Free running VCO direct output                           | $f_{VCO} = 1869MHz,$<br>$f_{O} = 1869MHz$                 | 1MHz offset   | -142        | dBc/Hz  |  |

|                                                                              | 10 - 100910112                                            | 6MHz offset   | -155        |         |  |

|                                                                              |                                                           | 10MHz offset  | -157.3      |         |  |

|                                                                              |                                                           | 100kHz offset | -126        |         |  |

|                                                                              |                                                           | 600kHz offset | -144        |         |  |

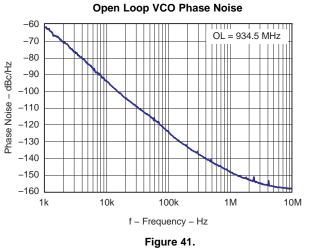

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1869MHz,<br>f <sub>O</sub> = 934.5MHz  | 1MHz offset   | -149        | dBc/H   |  |

| Thee fullning VCO divide-by-2 output                                         | 10 - 554.510112                                           | 6MHz offset   | -158        |         |  |

|                                                                              |                                                           | 10MHz offset  | -158.2      |         |  |

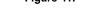

|                                                                              |                                                           | 100kHz offset | -132        |         |  |

|                                                                              | f <sub>VCO</sub> = 1869MHz,<br>f <sub>O</sub> = 467.25MHz | 600kHz offset | -150        |         |  |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      |                                                           | 1MHz offset   | -154        | dBc/H   |  |

|                                                                              |                                                           | 6MHz offset   | -157        |         |  |

|                                                                              |                                                           | 10MHz offset  | -157.3      |         |  |

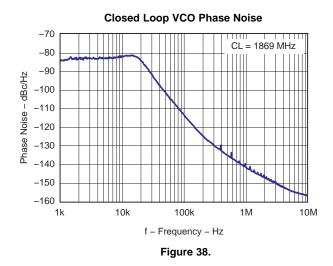

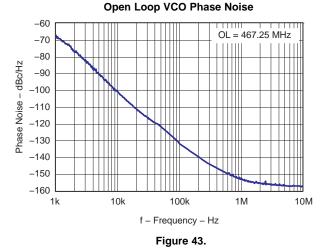

|                                                                              | f <sub>VCO</sub> = 1869MHz,                               | 1kHz offset   | -84.5       |         |  |

| VCO phase noise,                                                             |                                                           | 600kHz offset | -140        |         |  |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   | f <sub>O</sub> = 1869MHz                                  | 1MHz offset   | -143.6      | dBc/H   |  |

|                                                                              |                                                           | 10MHz offset  | -157        |         |  |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                            |               | 0.9°        |         |  |

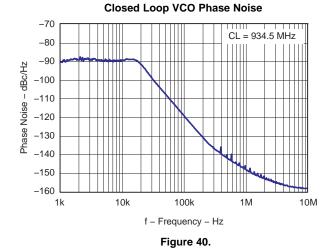

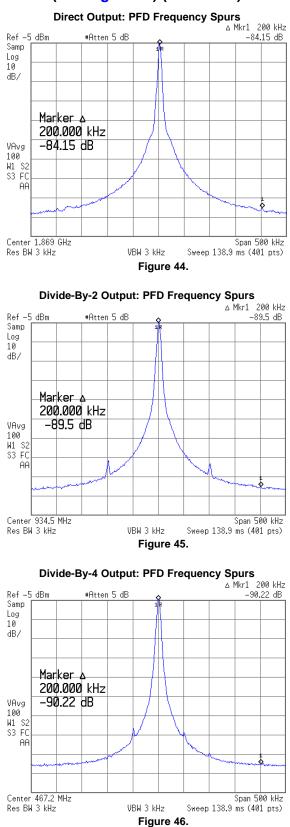

|                                                                              |                                                           | 1kHz offset   | -90.7       |         |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1869MHz,                               | 600kHz offset | -144        | dD a /l |  |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 934.5MHz                                 | 1MHz offset   | -148.5      | dBc/H   |  |

|                                                                              |                                                           | 10MHz offset  | -158        |         |  |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.53°       |         |  |

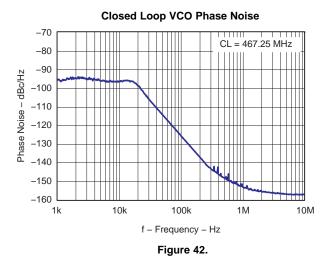

|                                                                              |                                                           | 1kHz offset   | -95         |         |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1869MHz,                               | 600kHz offset | -150        | dBc/H   |  |

| Closed loop phase noise divide-by-4 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 467.25MHz                                | 1MHz offset   | -154        | UDC/H   |  |

|                                                                              |                                                           | 10MHz offset  | -157        |         |  |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.35°       |         |  |

| VCO gain, Kv                                                                 | VCO free running                                          |               | 23          | MHz/    |  |

| Reference spur <sup>(2)</sup>                                                |                                                           |               | -80         | dBc     |  |

## **TRF3761-F ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST                                                   | CONDITIONS    | MIN TYP MAX | UNIT      |

|------------------------------------------------------------------------------|--------------------------------------------------------|---------------|-------------|-----------|

| IOISE CHARACTERISTICS                                                        |                                                        |               |             |           |

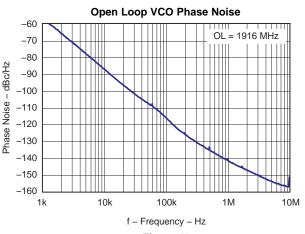

|                                                                              |                                                        | 100kHz offset | -116        |           |

|                                                                              |                                                        | 600kHz offset | -137        |           |

| VCO phase noise,<br>Free running VCO direct output                           | $f_{VCO} = 1916MHz,$<br>$f_{O} = 1916MHz$              | 1MHz offset   | -141        | dBc/Hz    |

|                                                                              | 10 - 10 100012                                         | 6MHz offset   | -155        |           |

|                                                                              |                                                        | 10MHz offset  | -157        |           |

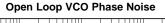

|                                                                              |                                                        | 100kHz offset | -113        |           |

|                                                                              |                                                        | 600kHz offset | -136        |           |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1916MHz,<br>f <sub>O</sub> = 958MHz | 1MHz offset   | -147.5      | dBc/H     |

|                                                                              | 10 - 50010112                                          | 6MHz offset   | -155        |           |

|                                                                              |                                                        | 10MHz offset  | -157.5      |           |

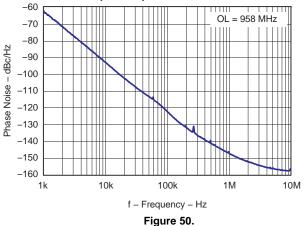

|                                                                              |                                                        | 100kHz offset | -128        |           |

|                                                                              | f <sub>VCO</sub> = 1916MHz,<br>f <sub>O</sub> = 479MHz | 600kHz offset | -148        | dBc/H     |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      |                                                        | 1MHz offset   | -150        |           |

|                                                                              |                                                        | 6MHz offset   | -155        |           |

|                                                                              |                                                        | 10MHz offset  | -156        |           |

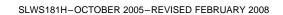

|                                                                              | $f_{VCO} = 1916MHz,$<br>$f_O = 1916MHz$                | 1kHz offset   | -82.5       |           |

| VCO phase noise,                                                             |                                                        | 600kHz offset | -136.7      | - ID - /I |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   |                                                        | 1MHz offset   | -142        | dBc/H     |

|                                                                              |                                                        | 10MHz offset  | -157        |           |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                         |               | 0.947°      |           |

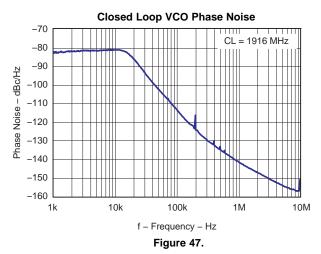

|                                                                              |                                                        | 1kHz offset   | -88.6       |           |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1916MHz,                            | 600kHz offset | -142.6      | -1D - /1  |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 958MHz                                | 1MHz offset   | -148.2      | dBc/⊢     |

|                                                                              |                                                        | 10MHz offset  | -158        |           |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                         |               | 0.477°      |           |

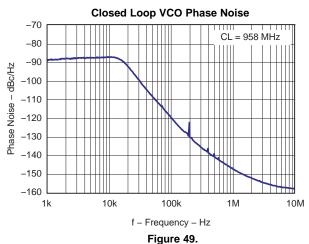

|                                                                              |                                                        | 1kHz offset   | -95         |           |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1916MHz,                            | 600kHz offset | -148        | dBc/H     |

| Closed loop phase noise divide-by-4 $output^{(1)(2)(3)}$                     | $f_0 = 479MHz$                                         | 1MHz offset   | -152        | UDU/N     |

|                                                                              |                                                        | 10MHz offset  | -156        |           |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                         |               | 0.231°      |           |

| VCO gain, Kv                                                                 | VCO free running                                       |               | 23          | MHz/      |

| Reference spur <sup>(2)</sup>                                                |                                                        |               | -80         | dBc       |

# **TRF3761-G ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST                                                      | CONDITIONS    | MIN TYP MAX | UNIT         |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------|--------------|--|

| OISE CHARACTERISTICS                                                         |                                                           |               |             |              |  |

|                                                                              |                                                           | 100kHz offset | -115        |              |  |

|                                                                              |                                                           | 600kHz offset | -136        |              |  |

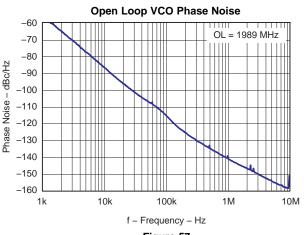

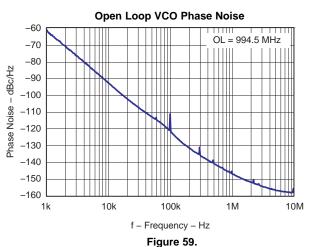

| VCO phase noise,<br>Free running VCO direct output                           | $f_{VCO} = 1989MHz,$<br>$f_{O} = 1989MHz$                 | 1MHz offset   | -141.2      | dBc/H        |  |

|                                                                              | 10 - 100010112                                            | 6MHz offset   | -155.6      |              |  |

|                                                                              |                                                           | 10MHz offset  | -159        |              |  |

|                                                                              |                                                           | 100kHz offset | -121.3      |              |  |

|                                                                              |                                                           | 600kHz offset | -142.4      |              |  |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 1989MHz,<br>f <sub>O</sub> = 994.5MHz  | 1MHz offset   | -141.5      | dBc/⊢        |  |

|                                                                              | 10 = 554.510112                                           | 6MHz offset   | -157.2      |              |  |

|                                                                              |                                                           | 10MHz offset  | -158        |              |  |

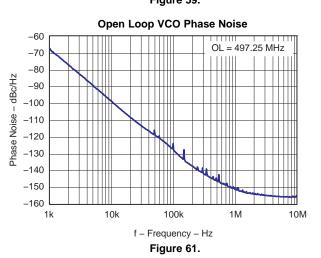

|                                                                              |                                                           | 100kHz offset | -128        |              |  |

|                                                                              | f <sub>VCO</sub> = 1989MHz,<br>f <sub>O</sub> = 497.25MHz | 600kHz offset | -148        | dBc/H        |  |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      |                                                           | 1MHz offset   | -151        |              |  |

|                                                                              |                                                           | 6MHz offset   | -156.8      |              |  |

|                                                                              |                                                           | 10MHz offset  | -157        |              |  |

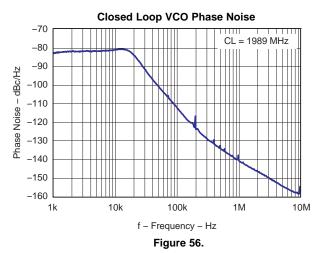

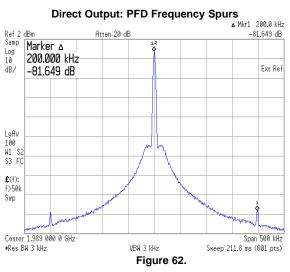

|                                                                              | f <sub>VCO</sub> = 1989MHz,                               | 1kHz offset   | -83         |              |  |

| VCO phase noise,                                                             |                                                           | 600kHz offset | -136        |              |  |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   | f <sub>O</sub> = 1989MHz                                  | 1MHz offset   | -141        | dBc/ŀ        |  |

|                                                                              |                                                           | 10MHz offset  | -159        | 1            |  |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                            |               | 1°          |              |  |

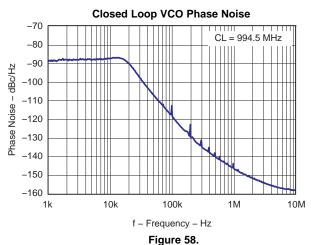

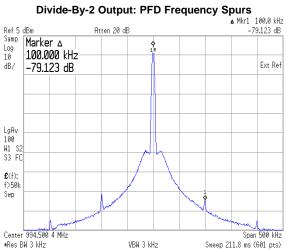

|                                                                              |                                                           | 1kHz offset   | -88.7       |              |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1989MHz,                               | 600kHz offset | -141.9      | 1            |  |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | f <sub>O</sub> = 994.5MHz                                 | 1MHz offset   | -147.5      | dBc/H        |  |

|                                                                              |                                                           | 10MHz offset  | -158        |              |  |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.509°      |              |  |

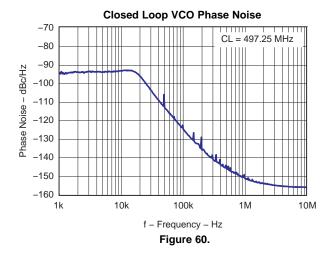

|                                                                              |                                                           | 1kHz offset   | -95         |              |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 1989MHz,                               | 600kHz offset | -147.9      | dD = "       |  |

| Closed loop phase noise divide-by-4 $output^{(1)(2)(3)}$                     | f <sub>O</sub> = 497.25MHz                                | 1MHz offset   | -151.3      | — dBc/⊢<br>— |  |

|                                                                              |                                                           | 10MHz offset  | -156        |              |  |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                            |               | 0.252°      |              |  |

| VCO gain, Kv                                                                 | VCO free running                                          |               | 23          | MHz/         |  |

| Reference spur <sup>(2)</sup>                                                |                                                           |               | -80         | dBc          |  |

## **TRF3761-H ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_{A}$  = –40 to 85  $^{\circ}C$  (unless otherwise noted)

| PARAMETER                                                                    | MIN TYP                                                 | MAX           | UNIT   |  |           |  |

|------------------------------------------------------------------------------|---------------------------------------------------------|---------------|--------|--|-----------|--|

| IOISE CHARACTERISTICS                                                        |                                                         |               | i.     |  |           |  |

|                                                                              |                                                         | 100kHz offset | -116   |  |           |  |

|                                                                              |                                                         | 600kHz offset | -136   |  |           |  |

| VCO phase noise,<br>Free running VCO direct output                           | f <sub>VCO</sub> = 2116MHz,<br>f <sub>O</sub> = 2116MHz | 1MHz offset   | -142   |  | dBc/Hz    |  |

|                                                                              | 10 - 21 1000112                                         | 6MHz offset   | -154.2 |  |           |  |

|                                                                              |                                                         | 10MHz offset  | -156   |  |           |  |

|                                                                              |                                                         | 100kHz offset | -123.3 |  |           |  |

|                                                                              |                                                         | 600kHz offset | -143   |  |           |  |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 2116MHz,<br>f <sub>O</sub> = 1058    | 1MHz offset   | -147.6 |  | dBc/H     |  |

|                                                                              | 10 - 1000                                               | 6MHz offset   | -157   |  |           |  |

|                                                                              |                                                         | 10MHz offset  | -158.3 |  |           |  |

|                                                                              |                                                         | 100kHz offset | -129.4 |  |           |  |

|                                                                              | f <sub>VCO</sub> = 2116MHz,<br>f <sub>O</sub> = 529MHz  | 600kHz offset | -149.8 |  |           |  |

| VCO phase noise,<br>Free running VCO divide-by-4 output                      |                                                         | 1MHz offset   | -152.7 |  | dBc/H     |  |

|                                                                              |                                                         | 6MHz offset   | -157.7 |  |           |  |

|                                                                              |                                                         | 10MHz offset  | -158   |  |           |  |

|                                                                              |                                                         | 1kHz offset   | -84    |  |           |  |

| VCO phase noise,                                                             | $f_{VCO} = 2116MHz,$<br>$f_O = 2116MHz$                 | 600kHz offset | -136   |  | - ID - /I |  |

| Closed loop phase noise direct output <sup>(1)(2)(3)</sup>                   |                                                         | 1MHz offset   | -141   |  | dBc/H     |  |

|                                                                              |                                                         | 10MHz offset  | -157   |  |           |  |

| RMS phase error<br>Closed loop phase noise direct output <sup>(3)</sup>      | 100Hz to 10MHz                                          |               | 0.99°  |  |           |  |

|                                                                              |                                                         | 1kHz offset   | -89    |  |           |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 2116MHz,                             | 600kHz offset | -143   |  | -ID - /I  |  |

| Closed loop phase noise divide-by-2 output <sup>(1)(2)(3)</sup>              | $f_0 = 1058MHz$                                         | 1MHz offset   | -148   |  | dBc/⊦     |  |

|                                                                              |                                                         | 10MHz offset  | -159   |  |           |  |

| RMS phase error<br>Closed loop phase noise divide-by-2 output <sup>(3)</sup> | 100Hz to 10MHz                                          |               | 0.54°  |  |           |  |

|                                                                              |                                                         | 1kHz offset   | -95    |  |           |  |

| VCO phase noise,                                                             | f <sub>VCO</sub> = 2116MHz,                             | 600kHz offset | -149.5 |  | dBa/U     |  |

| Closed loop phase noise divide-by-4 output <sup>(1)(2)(3)</sup>              | $f_0 = 529MHz$                                          | 1MHz offset   | -153   |  | dBc/H     |  |

|                                                                              |                                                         | 10MHz offset  | -158   |  |           |  |

| RMS phase error<br>Closed loop phase noise divide-by-4 output <sup>(3)</sup> | 100Hz to 10MHz                                          |               | 0.35°  |  |           |  |

| VCO gain, Kv                                                                 | VCO free running                                        |               | 23     |  | MHz/      |  |

| Reference spur <sup>(2)</sup>                                                |                                                         |               | -80    |  | dBc       |  |

# **TRF3761-J ELECTRICAL CHARACTERISTICS**

Supply voltage =  $V_{CC}$  = 5V,  $T_A$  = –40 to 85  $^\circ C$  (unless otherwise noted)

| PARAMETER                                                                    | TEST                                                   | CONDITIONS        | MIN TYP MAX | UNIT     |  |

|------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|-------------|----------|--|

| DISE CHARACTERISTICS                                                         |                                                        |                   |             |          |  |

|                                                                              |                                                        | 100kHz offset     | -116.7      |          |  |

|                                                                              |                                                        | 600kHz offset     | -135.4      |          |  |

| VCO phase noise,<br>Free running VCO direct output                           | $f_{VCO} = 2289MHz,$<br>$f_{O} = 2289MHz$              | 1MHz offset       | -141        | dBc/H    |  |

|                                                                              | 10 - 220010112                                         | 6MHz offset       | -153.8      |          |  |

|                                                                              |                                                        | 10MHz offset      | -156.4      |          |  |

|                                                                              |                                                        | 100kHz offset     | -123        |          |  |

|                                                                              |                                                        | 600kHz offset     | -142        |          |  |

| VCO phase noise,<br>Free running VCO divide-by-2 output                      | f <sub>VCO</sub> = 2289MHz,<br>f <sub>O</sub> = 1144.5 | 1MHz offset       | -147        | dBc/H    |  |

|                                                                              | 10 = 1144.0                                            | 6MHz offset       | -156.2      |          |  |

|                                                                              |                                                        | 10MHz offset      | -157.5      |          |  |

|                                                                              |                                                        | 100kHz offset     | -129        |          |  |