#### features

- Up to 200-mA Output Current

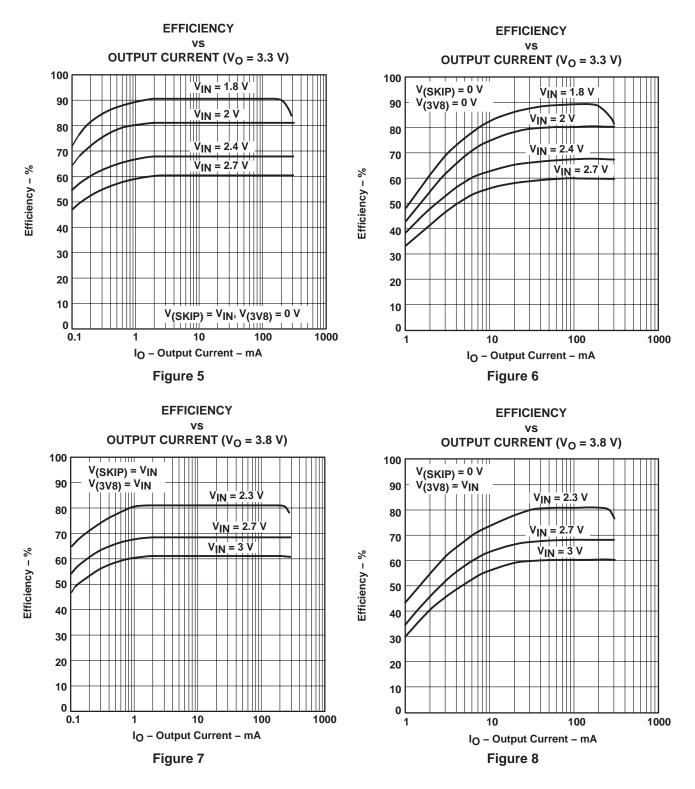

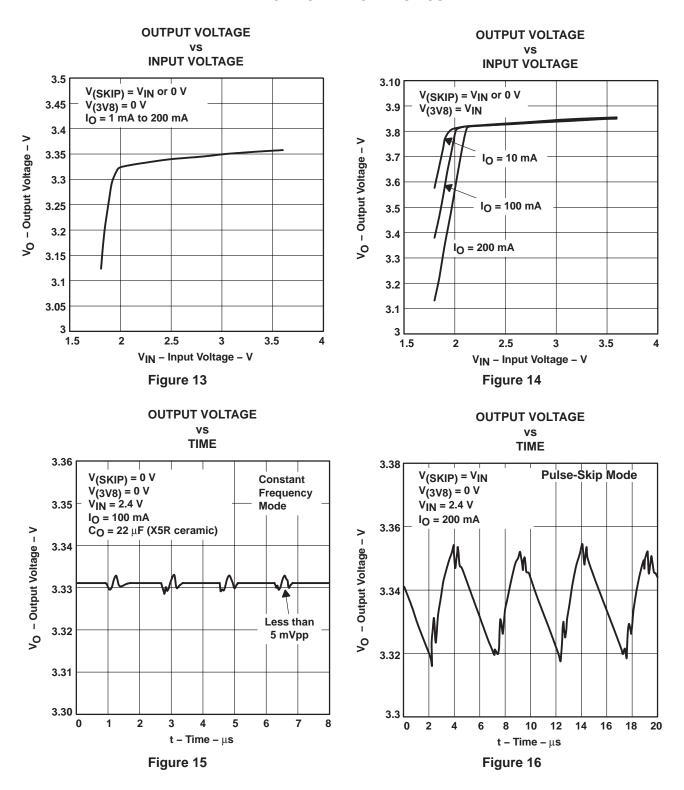

- Less Than 5-mV<sub>pp</sub> Output Voltage Ripple

- No Inductors Required/Low EMI

- Regulated 3.3-V ±4% Output

- Only Four External Components Required

- Up to 90% Efficiency

- 1.8-V to 3.6-V Input Voltage Range

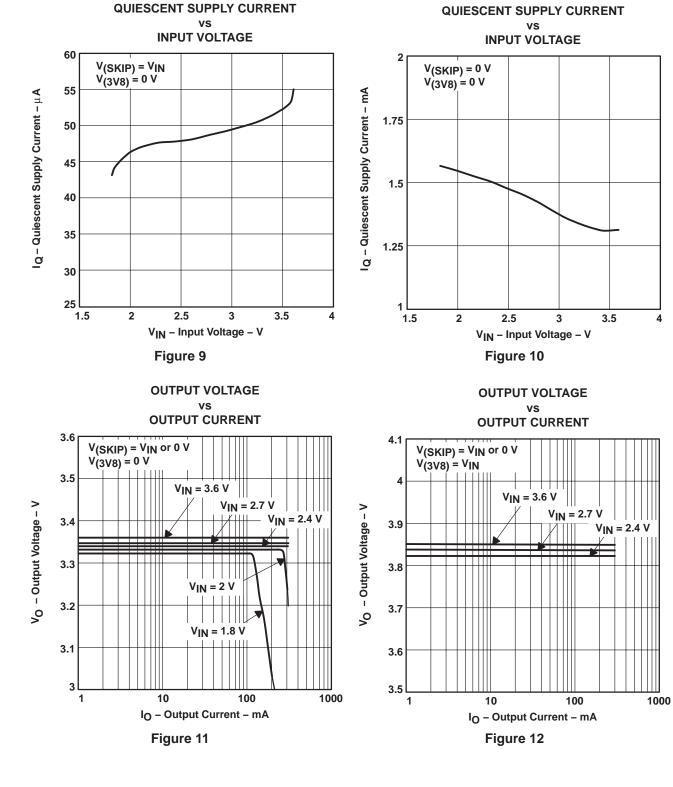

- 50-µA Quiescent Supply Current

- 0.05-μA Shutdown Current

- Load Isolated in Shutdown

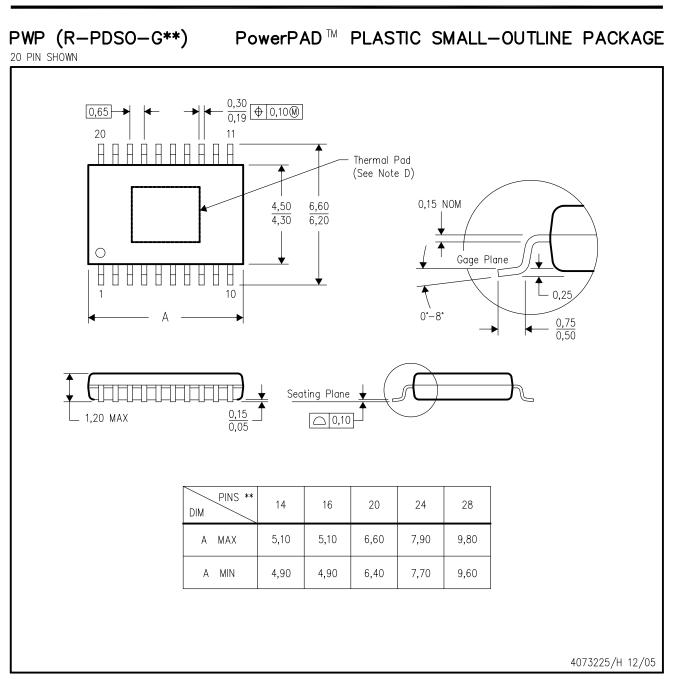

- Space-Saving Thermally-Enhanced TSSOP PowerPAD<sup>™</sup> Package

- Evaluation Module Available (TPS60100EVM-131)

#### description

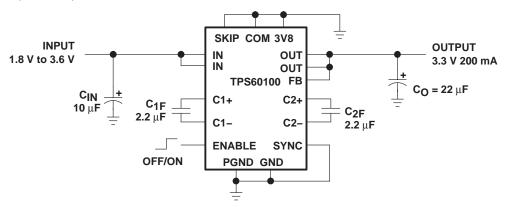

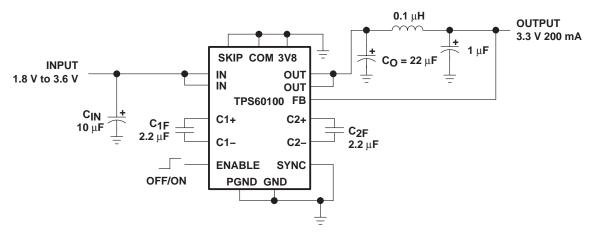

The TPS60100 step-up, regulated charge pump generates a 3.3-V  $\pm$ 4% output voltage from a 1.8-V to 3.6-V input voltage (two alkaline, NiCd, or NiMH batteries). Output current is 200 mA from a 2-V input. Only four external capacitors are needed to build a complete low-noise dc/dc converter. The push-pull operating mode of two single-ended charge pumps assures the low output voltage ripple as current is continuously transferred to the output. From a 2-V input, the TPS60100 can start into full load with loads as low as 16  $\Omega$ .

The TPS60100 features either constant frequency mode to minimize noise and output voltage ripple or the power-saving pulse-skip mode to extend battery life at light loads. The TPS60100 switching frequency is 300 kHz. The logic shutdown function reduces the supply current to 1- $\mu$ A (max) and disconnects the load from the input. Special current-control circuitry prevents excessive current from being drawn from the battery during start-up. This dc/dc converter requires no inductors and has low EMI. It is available in the small 20-pin TSSOP PowerPAD<sup>TM</sup> package (PWP).

### applications

Replaces DC/DC Converters With Inductors in

- Battery-Powered Applications

- Two Battery Cells to 3.3-V Conversion

- Portable Instruments

- Battery-Powered Microprocessor and DSP Systems

- Miniature Equipment

- Backup-Battery Boost Converters

- PDAs

- Laptops

- Handheld Instrumentation

- Medical Instruments

- Cordless Phones

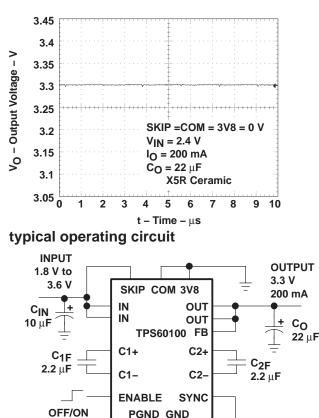

#### output voltage ripple

Figure 1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

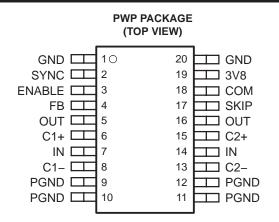

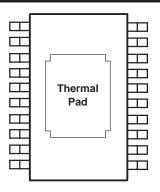

#### Figure 2. Bottom View of PWP Package, Showing the Thermal Pad

#### **AVAILABLE OPTIONS**

| PACKAGE         |  |  |  |  |  |  |  |

|-----------------|--|--|--|--|--|--|--|

| TSSOP†<br>(PWP) |  |  |  |  |  |  |  |

| TPS60100PWP     |  |  |  |  |  |  |  |

| +               |  |  |  |  |  |  |  |

<sup>†</sup> This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TPS60100PWPR).

### **Terminal Functions**

| TERMI  | NAL   |     |                                                                                                                                                                                                                                                                |

|--------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                    |

| 3V8    | 19    | I   | Mode selection.<br>When 3V8 is logic low the charge pump operates in the regulated 3.3-V mode. When 3V8 is connected to IN the regulator operates in preregulated 3.8-V mode.                                                                                  |

| C1+    | 6     |     | Positive terminal of the charge-pump capacitor C1F                                                                                                                                                                                                             |

| C1-    | 8     |     | Negative terminal of the charge-pump capacitor C1F                                                                                                                                                                                                             |

| C2+    | 15    |     | Positive terminal of the charge-pump capacitor C2F                                                                                                                                                                                                             |

| C2-    | 13    |     | Negative terminal of the charge-pump capacitor C2F                                                                                                                                                                                                             |

| СОМ    | 18    | I   | Mode selection.<br>When COM is logic low the charge pump operates in push-pull mode to minimize output ripple. When COM is connected to IN the regulator operates in single-ended mode requiring only one flying capacitor.                                    |

| ENABLE | 3     | I   | ENABLE Input. The device turns off, the output disconnects from the input, and the supply current decreases to 0.05 $\mu$ A when ENABLE is a logic low. Connect ENABLE to IN for normal operation.                                                             |

| FB     | 4     | I   | FEEDBACK input. Connect FB to OUT as close to the load as possible to achieve best regulation. Resistive divider<br>is on chip to match internal reference voltage of 1.22 V.                                                                                  |

| GND    | 1, 20 |     | GROUND. Analog ground for internal reference and control circuitry. Connect to PGND through a short trace.                                                                                                                                                     |

| IN     | 7, 14 | I   | Supply Input. Connect to an input supply in the 1.8-V to 3.6-V range. Bypass IN to GND with a (C <sub>O</sub> /2) $\mu$ F capacitor. Connect both INs through a short trace.                                                                                   |

| OUT    | 5, 16 | 0   | Regulated power output. Connect both OUTs through a short trace and bypass OUT to GND with the output filter capacitor $C_0$ . $V_0 = 3.3$ V when $3V8 = 1$ ow and $V_0 = 3.8$ V when $3V8 = $ high.                                                           |

| PGND   | 9–12  |     | PGND power ground. Charge-pump current flows through this pin. Connect all PGNDs together.                                                                                                                                                                     |

| SKIP   | 17    | I   | Mode selection. When SKIP is logic low, the charge pump operates in constant-frequency mode. Output ripple and noise are minimized in this mode. When SKIP is connect to IN, the device operates in pulse skip mode. Quiescent current is lowest in this mode. |

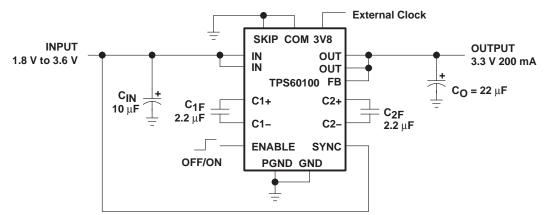

| SYNC   | 2     | I   | Selection for external clock signal. Connect to GND to use the internally generated clock signal. Connect to IN for external synchronization. In this case, the clock signal needs to be fed through 3V8 and the device operates in the regulated 3.3-V mode.  |

### absolute maximum ratings (unless otherwise noted)<sup>†‡</sup>

| Input voltage range, VI (IN, OUT, ENABLE, SKIP, COM, 3V8, FB, SYNC) | 0.3 V to 5.5 V                       |

|---------------------------------------------------------------------|--------------------------------------|

| Differential input voltage, V <sub>ID</sub> (C1+, C2+ to GND)       | –0.3 V to (V <sub>OUT</sub> + 0.3 V) |

| Differential input voltage, V <sub>ID</sub> (C1–, C2– to GND)       | –0.3 V to (V <sub>IN</sub> + 0.3 V)  |

| Continuous total power dissipation                                  | See Dissipation Rating Tables        |

| Continuous output current                                           | 300 mA                               |

| Storage temperature range, T <sub>stg</sub>                         | –55°C to 150°C                       |

| Lead temperature 1,6 mm (1/16 inch) from case for 10s               | 260°C                                |

| Maximum junction temperature, T <sub>J</sub>                        |                                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup>VENABLE, VSKIP, VCOM, V3V8 and VSYNC can exceed VIN up to the maximum rated voltage without increasing the leakage current drawn by these mode select inputs.

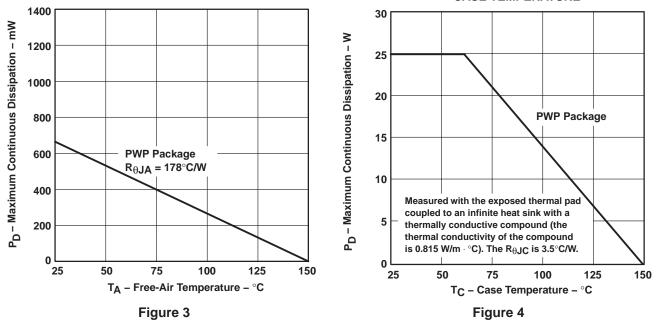

DISSIPATION RATING TABLE 1 - FREE-AIR TEMPERATURE (see Figure 3)

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| PWP     | 700 mW                | 5.6 mW/°C                   | 448 mW                | 364 mW                |

| DISSIPATION RATING TABLE 2 – CASE TEMPERATURE (see Figure 4) |                                       |             |        |        |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------|-------------|--------|--------|--|--|--|--|

| PACKAGE                                                      | T <sub>C</sub> = 85°C<br>POWER RATING |             |        |        |  |  |  |  |

| PWP                                                          | 25 W                                  | 285.7 mW/°C | 22.9 W | 18.5 W |  |  |  |  |

**DISSIPATION DERATING CURVE§**

VS FREE-AIR TEMPERATURE

§ Dissipation rating tables and figures are provided for maintenance of junction temperature at or below absolute maximum temperature of 150°C. It is recommended not to exceed a junction temperature of 125°C.

# **TPS60100 REGULATED 3.3 V 200-mA LOW-NOISE CHARGE PUMP DC/DC CONVERTER**

SLVS213B - MAY 1999 - REVISED SEPTEMBER 1999

electrical characteristics at C<sub>IN</sub> = 10  $\mu$ F, C<sub>1F</sub> = C<sub>2F</sub> = 2.2  $\mu$ F<sup>†</sup>, C<sub>O</sub> = 22  $\mu$ F, T<sub>C</sub> = -40°C to 85°C, V<sub>IN</sub> = 2V, V<sub>FB</sub> = V<sub>O</sub>, V<sub>ENABLE</sub> = V<sub>IN</sub>, V<sub>SKIP</sub> = V<sub>IN</sub> or 0 V and V<sub>COM</sub> = V<sub>3V8</sub> = V<sub>SYNC</sub> = 0 V (unless otherwise noted)

| PARAMETER |                                                        | TEST CO                                                    | NDITIONS                                  | MIN                     | TYP   | MAX                    | UNIT |

|-----------|--------------------------------------------------------|------------------------------------------------------------|-------------------------------------------|-------------------------|-------|------------------------|------|

| VIN       | Input voltage                                          |                                                            |                                           | 1.8                     |       | 3.6                    | V    |

| VIN(UV)   | Input undervoltage lockout threshold                   |                                                            |                                           |                         | 1.6   | 1.8                    | V    |

| IO(MAX)   | Maximum output current                                 |                                                            |                                           | 200                     |       |                        | mA   |

|           |                                                        | 3.17                                                       | 3.3                                       | 3.43                    |       |                        |      |

| VO        | Output voltage                                         | $2 V < V_{IN} < 3.3 V$ ,                                   | 0 < I <sub>O</sub> < 200 mA               | 3.17                    | 3.3   | 3.43                   | V    |

|           |                                                        | $3.3 \text{ V} < \text{V}_{IN} < 3.6 \text{ V},$           | 0 < I <sub>O</sub> < 200 mA               | 3.17                    | 3.3   | 3.47                   |      |

| VO(RIP)   | Output voltage ripple                                  | I <sub>O</sub> = 200 mA,                                   | VSKIP = 0 V                               |                         | 5‡    |                        | тVрр |

| lo(leak)  | Output leakage current                                 | V <sub>IN</sub> = 2.4 V,                                   | V <sub>ENABLE</sub> = 0 V                 |                         |       | 1                      | μΑ   |

|           | Quiescent current                                      | V <sub>SKIP</sub> = V <sub>IN</sub> = 2.4 V                |                                           |                         | 50    | 90                     | μΑ   |

| lQ        | (no-load input current)                                | $V_{SKIP} = 0 V,$                                          | V <sub>IN</sub> = 2.4 V                   |                         | 1.5   |                        | mA   |

| IDD(SDN)  | Shutdown supply current                                | V <sub>IN</sub> = 2.4 V,                                   | VENABLE = 0 V                             |                         | 0.05  | 1                      | μΑ   |

| fOSC(int) | Internal switching frequency                           | V <sub>IN</sub> = 2.4 V                                    |                                           | 200                     | 300   | 400                    | kHz  |

| fOSC(ext) | External clock frequency                               | $V_{SYNC} = V_{IN}$                                        | $V_{IN}$ = 1.8V to 3.6 V                  | 400                     | 600   | 800                    | kHz  |

|           | External clock duty cycle                              | $V_{SYNC} = V_{IN}$                                        | $V_{IN}$ = 1.8V to 3.6 V                  | 20%                     |       | 80%                    |      |

|           | Efficiency                                             | IO = 100 mA                                                |                                           |                         | 80%   |                        |      |

| VINL      | Input voltage low,<br>ENABLE, SKIP, COM, 3V8, SYNC     | V <sub>IN</sub> = 1.8 V                                    |                                           |                         |       | $^{0.3	imes}_{V_{IN}}$ | V    |

| VINH      | Input voltage high,<br>ENABLE, SKIP, COM, 3V8, SYNC    | V <sub>IN</sub> = 3.6 V                                    |                                           | 0.7×<br>V <sub>IN</sub> |       |                        | V    |

| l(LEAK)   | Input leakage current,<br>ENABLE, SKIP, COM, 3V8, SYNC | VENABLE = VSKIP = V<br>VSYNC = VGND or VIN                 |                                           |                         | 0.01  | 0.1                    | μA   |

|           | Output load regulation                                 | $V_{O} = 3.3 V,$<br>$T_{C} = 25^{\circ}C$                  | 1 mA < I <sub>O</sub> < 200 mA            |                         | 0.004 |                        | %/mA |

|           | Output line regulation                                 | 2 V < V <sub>IN</sub> < 3.3 V,<br>I <sub>O</sub> = 100 mA, | $V_{O} = 3.3 V,$<br>$T_{C} = 25^{\circ}C$ |                         | 0.6   |                        | %/V  |

|           | Short circuit current                                  | $V_{IN} = 2.4 V$<br>$T_C = 25^{\circ}C$                    | V <sub>O</sub> = 0 V,                     |                         | 125   |                        | mA   |

<sup>†</sup> Use only ceramic capacitors with X5R or X7R dielectric as flying capacitors.

<sup>‡</sup> Achieved with  $C_0 = 22 \,\mu\text{F}$  X5R dielectric ceramic capacitor

electrical characteristics for preregulated 3.8-V Mode ( $V_{(3V8)} = V_{IN}$ ),  $C_{IN} = 10 \ \mu$ F,  $C_{1F} = C_{2F} = 2.2 \ \mu$ F<sup>†</sup>,  $C_O = 22 \ \mu$ F,  $T_C = -40^{\circ}$ C to  $85^{\circ}$ C,  $V_{IN} = 2.4 \ V$ ,  $V_{FB} = V_O$ ,  $V_{ENABLE} = V_{IN}$ ,  $V_{SKIP} = V_{IN}$  or 0 V and  $V_{COM} = V_{SYNC} = 0 \ V$  (unless otherwise noted)

| PARAMETER |                              | TEST                            | TEST CONDITIONS                |     |      | MAX | UNIT |

|-----------|------------------------------|---------------------------------|--------------------------------|-----|------|-----|------|

| VIN       | Input voltage                |                                 |                                | 2.2 |      | 3.6 | V    |

| IO(MAX)   | Maximum output current       |                                 |                                | 200 |      |     | mA   |

| VO        | Output voltage               | 2.2 V < V <sub>IN</sub> < 3.6 V | ′, 0 < I <sub>O</sub> < 200 mA | 3.6 | 3.8  | 4   | V    |

| IO(LEAK)  | Output leakage current       | VENABLE = 0 V                   |                                |     |      | 1   | μΑ   |

|           | Quiescent current            | VSKIP = VIN                     |                                |     | 60   |     | μΑ   |

| lQ        | (no-load input current)      | VSKIP = 0 V                     |                                |     | 2    |     | mA   |

| IDD(SDN)  | Shutdown supply current      | VENABLE = 0 V                   |                                |     | 0.05 | 1   | μΑ   |

| fosc      | Internal switching frequency |                                 |                                | 200 | 300  | 400 | kHz  |

|           | Short circuit current        | V <sub>O</sub> = 0 V,           | $T_C = 25^{\circ}C$            |     | 125  |     | mA   |

$^{\dagger}$  Use only ceramic capacitors with X5R or X7R dielectric as flying capacitors.

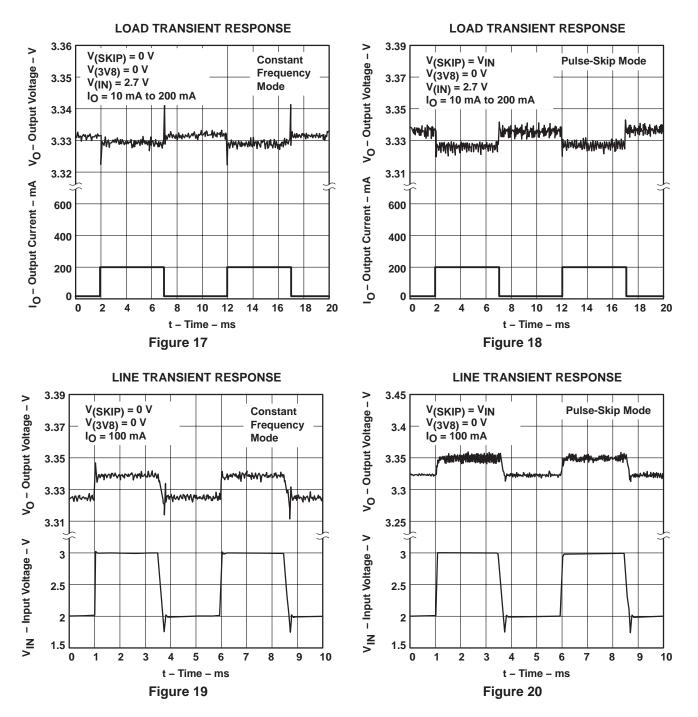

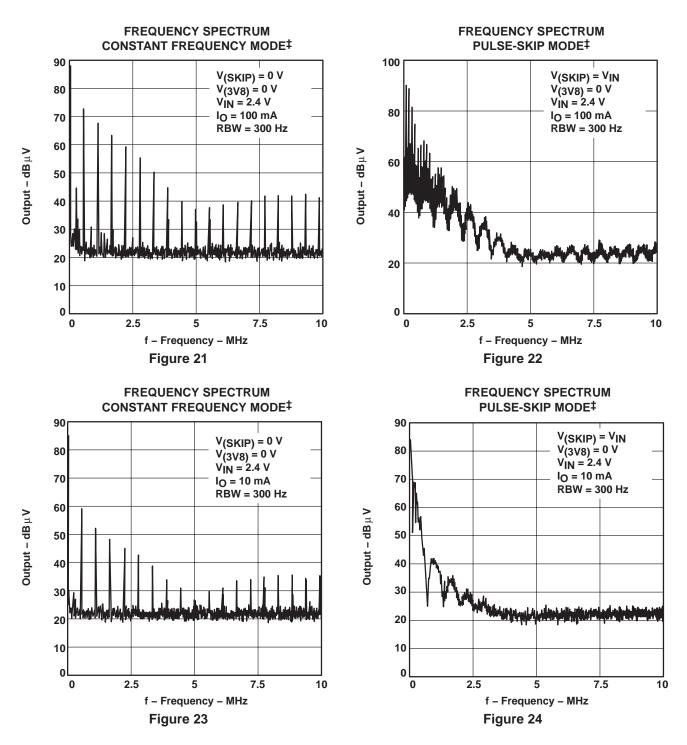

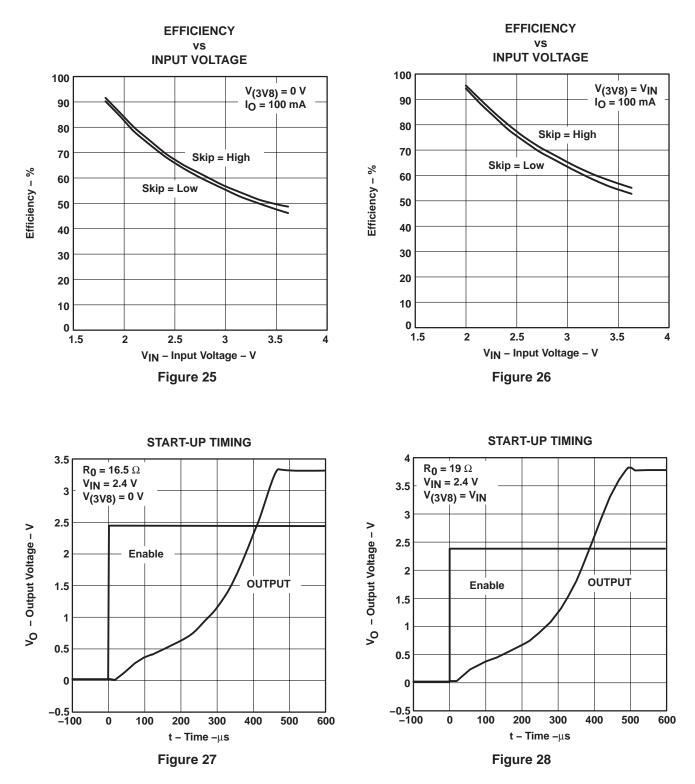

**TYPICAL CHARACTERISTICS<sup>†</sup>**

TYPICAL CHARACTERISTICS<sup>†</sup>

TYPICAL CHARACTERISTICS<sup>†</sup>

### TYPICAL CHARACTERISTICS<sup>†</sup>

TYPICAL CHARACTERISTICS<sup>†</sup>

$T_C = 25^{\circ}C$ ,  $V_{COM} = V_{SYNC} = 0$  V,  $C_{IN} = 10 \ \mu$ F,  $C_{1F} = C_{2F} = 2.2 \ \mu$ F,  $C_O = 22 \ \mu$ F, unless otherwise noted Test circuit: TPS60100EVM-131

### **TYPICAL CHARACTERISTICS<sup>†</sup>**

# **TPS60100** REGULATED 3.3 V 200-mA LOW-NOISE CHARGE PUMP DC/DC CONVERTER

SLVS213B - MAY 1999 - REVISED SEPTEMBER 1999

### detailed description

#### operating principle

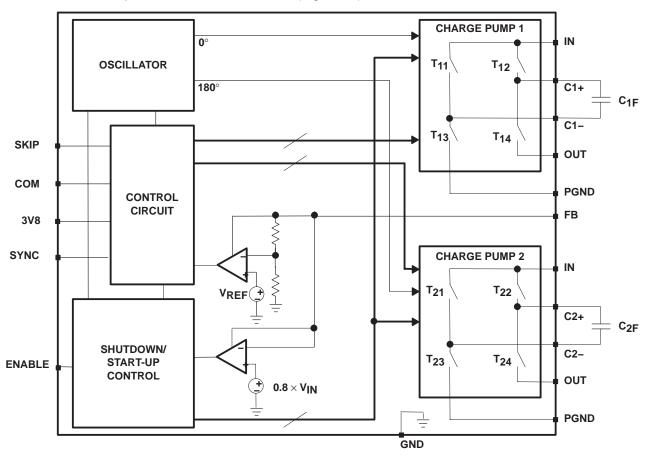

The TPS60100 charge pump provides a regulated 3.3-V output from a 1.8-V to 3.6-V input. It delivers a maximum load current of 200 mA. Designed specifically for space critical battery powered applications, the complete charge pump circuit requires only four external capacitors. The circuit can be optimized for highest efficiency at light loads or lowest output noise. The TPS60100 consists of an oscillator, a 1.22-V bandgap reference, an internal resistive feedback circuit, an error amplifier, high current MOSFET switches, a shutdown/start-up circuit, and a control circuit (Figure 29)

The oscillator runs at a 50% duty cycle. The device consists of two single-ended charge pumps which operate with  $180^{\circ}$  phase shift. Each single ended charge pump transfers charge into its transfer capacitor ( $C_{xF}$ ) in one half of the period. During the other half of the period (transfer phase), C<sub>xF</sub> is placed in series with the input to transfer its charge to C<sub>O</sub>. While one single-ended charge pump is in the charge phase, the other one is in the transfer phase. This operation guarantees an almost constant output current which ensures a low output ripple.

If the clock were to run continuously, this process would eventually generate an output voltage equal to two times the input voltage (hence the name doubler). In order to provide a regulated fixed output voltage of 3.3 V, the TPS60100 uses either pulse-skip mode or constant-frequency mode. Pulse-skip mode and constant-frequency mode are externally selected via the SKIP input pin.

### detailed description (continued)

#### start-up procedure

During start-up, i.e. when ENABLE is set from logic low to logic high, the switches T12 and T14 (charge pump 1), and the switches T22 and T24 (charge pump 2) are conducting to charge up the output capacitor until the output voltage  $V_0$  reaches  $0.8 \times V_{IN}$ . When the start-up comparator detects this limit, the IC begins to operate in the mode selected with SKIP, COM and 3V8. This start-up charging of the output capacitor guarantees a short start-up time and eliminates the need for a Schottky diode between IN and OUT.

#### pulse-skip mode

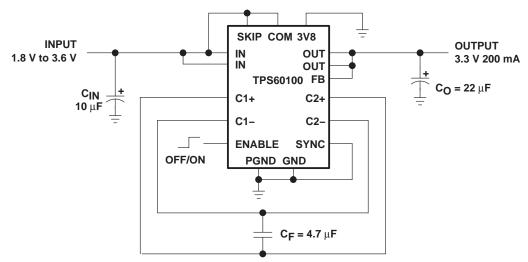

In pulse-skip mode (SKIP = high), the error amplifier disables switching of the power stages when it detects an output higher than 3.3 V. The oscillator halts. The IC then skips switching cycles until the output voltage drops below 3.3 V. Then the error amplifier reactivates the oscillator and switching of the power stages starts again. The pulse-skip regulation mode minimizes operating current because it does not switch continuously and deactivates all functions except bandgap reference and error amplifier when the output is higher than 3.3 V. When switching is disabled from the error amplifier, the load is also isolated from the input. SKIP is a logic input and should not remain floating. The typical operating circuit of the TPS60100 in pulse skip mode is shown in Figure 1.

#### constant-frequency mode

When SKIP is low, the charge pump runs continuously at the frequency  $f_{OSC}$ . The control circuit, fed from the error amplifier, controls the charge on  $C_{1F}$  and  $C_{2F}$  by driving the gates of the FETs  $T_{12}/T_{13}$  and  $T_{22}/T_{23}$ , respectively. When the output voltage falls, the gate drive increases, resulting in a larger voltage across  $C_{1F}$  and  $C_{2F}$ . This regulation scheme minimizes output ripple. Since the device switches continuously, the output noise contains well-defined frequency components, and the circuit requires smaller external capacitors for a given output ripple. However, constant-frequency mode, due to higher operating current, is less efficient at light loads than pulse-skip mode.

| FEATURE                                                    | PULSE-SKIP MODE<br>(SKIP = High) | CONSTANT-FREQUENCY MODE<br>(SKIP = Low) |

|------------------------------------------------------------|----------------------------------|-----------------------------------------|

| Best light-load efficiency                                 | Х                                |                                         |

| Smallest external component size for a given output ripple |                                  | X                                       |

| Output ripple amplitude                                    | Small amplitude                  | Very small amplitude                    |

| Output ripple frequency                                    | Variable                         | Constant                                |

| Load regulation                                            | Very good                        | Good                                    |

NOTE: Even in pulse-skip mode the output ripple amplitude is small if the push-pull operating mode is selected via COM.

#### detailed description (continued)

#### push-pull operating mode

In push-pull operating mode (COM = low), the two single-ended charge pumps operate with 180° phase shift. The oscillator signal has a 50% duty cycle. Each single-ended charge pump transfers charge into its transfer capacitor ( $C_{xF}$ ) in one-half of the period. During the other half of the period (transfer phase),  $C_{xF}$  is placed in series with the input to transfer its charge to C<sub>O</sub>. While one single-ended charge pump is in the charge phase, the other one is in the transfer phase. This operation guarantees an almost constant output current which ensures a low output ripple. COM is a logic input and should not remain floating. The typical operating circuit of the TPS60100 in push-pull mode is shown in Figure 1 and Figure 30.

#### single-ended operating mode

When COM is high, the device runs in single-ended operating mode. The two single-ended charge pumps operate in parallel without phase shift. They transfer charge into the transfer capacitor ( $C_F$ ) in one half of the period. During the other half of the period (transfer phase), C<sub>F</sub> is placed in series with the input to transfer its charge to  $C_0$ . In single-ended operating mode only one transfer capacitor ( $C_F = C_{1F} + C_{2F}$ ) is required, resulting in less board space.

#### Figure 31. Typical Operating Circuit TPS60100 in Single-Ended Operating Mode

| Table 2. Tradeoffs Betwee | en Operating Modes |

|---------------------------|--------------------|

|---------------------------|--------------------|

| FEATURE                 | PUSH-PULL MODE<br>(COM = Low) | SINGLE-ENDED MODE<br>(COM = High) |

|-------------------------|-------------------------------|-----------------------------------|

| Output ripple amplitude | Small amplitude               | Large amplitude                   |

| Smallest board space    |                               | Х                                 |

#### regulated 3.3 V operating mode

In regulated 3.3 V operating mode (3V8 = low) the device provides a regulated 3.3-V output from a1.8-V to 3.6-V input. 3V8 is a logic input and should not remain floating. The typical operating circuit of the TPS60100 in (3.3 V) regulated mode is shown in Figure 1 and Figure 30.

#### pre-regulated 3.8 V operating mode

When 3V8 is high, the device provides a preregulated 3.8-V output from a 2.2-V to 3.6-V input. This mode should be used if a tighter output voltage tolerance is a major concern. In this case the charge pump generates the input voltage for a low-dropout regulator.

### detailed description (continued)

#### shutdown

Driving ENABLE low places the device in shutdown mode. This disables all switches, the oscillator, and control logic. The device typically draws 0.05- $\mu$ A (1- $\mu$ A max) of supply current in this mode. Leakage current drawn from the output is as low as 1  $\mu$ A max. The device exits shutdown once ENABLE is set high level. The typical no-load shutdown exit time is 10  $\mu$ s. When the device is in shutdown, the load is isolated from the input and the output is high impedance.

#### external clock signal

If the device shall operate at a user defined frequency, an external clock signal can be used. Therefore, SYNC needs to be connected to IN and the external oscillator signal can drive 3V8. The maximum external frequency is limited to 800 kHz. The switching frequency of the converter is half of the external oscillator frequency. It is recommended to operate the charge pump in constant-frequency mode if an external clock signal is used so that the output noise contains only well-defined frequency components.

Figure 32. Typical Operating Circuit TPS60100 With External Synchronization

#### undervoltage lockout

The TPS60100 has an undervoltage lockout feature that deactivates the device and places it in shutdown mode when the input voltage falls below 1.6 V.

#### capacitor selection

The TPS60100 requires only four external capacitors as shown in the basic application circuit. Their values are closely linked to the output current capacity, output noise requirements, and mode of operation. Generally, the transfer capacitors ( $C_{xF}$ ) will be the smallest.

The input capacitor improves system efficiency by reducing the input impedance and stabilizes the input current.  $C_{IN}$  is recommended to be about two to four times as large as  $C_{xF}$ .

The output capacitor (C<sub>O</sub>) can be selected from 5-times to 50-times larger than  $C_{xF}$ , depending on the mode of operation and ripple tolerance<sup>†</sup>. Tables 3 and 4 show capacitor values recommended for low quiescent-current operation (pulse-skip mode) and for low output voltage ripple operation (constant-frequency mode). A recommendation is given for smallest size.

# Table 3. Recommended Capacitor Values for Low Quiescent-Current Operation<sup>†</sup> (pulse-skip mode)

| V <sub>IN</sub><br>[V] | IO [mA] | C <sub>IN</sub><br>[μF] |          | C <sub>xF</sub><br>[μF] | C <sub>O</sub><br>[μF] |          |                                |  |

|------------------------|---------|-------------------------|----------|-------------------------|------------------------|----------|--------------------------------|--|

| [v]                    |         | TANTALUM                | CERAMIC  | <b>ιμ</b> -j            | TANTALUM               | CERAMIC  | RIPPLE V <sub>PP</sub><br>[mV] |  |

| 2.4                    | 150     | 10                      |          | 2.2                     | 22                     |          | 90                             |  |

| 2.4                    | 150     |                         | 10 (X5R) | 2.2                     |                        | 22 (X5R) | 45                             |  |

| 2.4                    | 200     | 10                      |          | 2.2                     | 22                     |          | 55                             |  |

| 2.4                    | 200     |                         | 10 (X5R) | 2.2                     |                        | 22 (X5R) | 30                             |  |

<sup>†</sup> All measurements are done with additional 1-µF X7R ceramic capacitors at input and output.

# Table 4. Recommended Capacitor Values for Low Output Voltage Ripple Operation<sup>†</sup>(constant-frequency mode)

| VIN | lo   | <b>C</b> Ι<br>[μ |          | C <sub>xF</sub> | כ<br>וי  |          |                                |  |

|-----|------|------------------|----------|-----------------|----------|----------|--------------------------------|--|

| [V] | [mA] | TANTALUM         | CERAMIC  | [μ <b>F</b> ]   | TANTALUM | CERAMIC  | RIPPLE V <sub>PP</sub><br>[mV] |  |

| 2.4 | 150  | 10               |          | 2.2             | 22       |          | 13                             |  |

| 2.4 | 150  |                  | 10 (X5R) | 2.2             |          | 22 (X5R) | 4                              |  |

| 2.4 | 200  | 10               |          | 2.2             | 22       |          | 15                             |  |

| 2.4 | 200  |                  | 10 (X5R) | 2.2             |          | 22 (X5R) | 5                              |  |

<sup>†</sup>All measurements are done with additional 1-μF X7R ceramic capacitors at input and output.

<sup>†</sup> In constant-frequency mode always select  $C_O \ge 22 \ \mu F$

For the TPS60100, the smallest board space size can be achieved using Sprague's 595D-series tantalum capacitors for input and output. However, with the trend towards high capacitance ceramic capacitors in smaller size packages, these type of capacitors might become competitive in size soon.

| MANUFACTURER | PART NUMBER                                                              | CAPACITANCE                               | TYPE                                         |

|--------------|--------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|

| Taiyo Yuden  | LMK212BJ105KG-T                                                          | 1 μF                                      | Ceramic                                      |

|              | LMK212BJ225MG-T                                                          | 2.2 μF                                    | Ceramic                                      |

|              | JMK316BJ106ML-T                                                          | 10 μF                                     | Ceramic                                      |

|              | LMK432BJ226MM-T                                                          | 22 μF                                     | Ceramic                                      |

| AVX          | 0805ZC105KAT2A                                                           | 1 μF                                      | Ceramic                                      |

|              | 1206ZC225KAT2A                                                           | 2.2 μF                                    | Ceramic                                      |

|              | TPSC106025R0500                                                          | 10 μF                                     | Tantalum                                     |

|              | TPSC226016R0375                                                          | 22 μF                                     | Tantalum                                     |

| Sprague      | 595D106X0010A2T<br>595D226X06R3A2T<br>595D226X06R3B2T<br>595D226X0020C2T | 10 μF<br>22 μF<br>22 μF<br>22 μF<br>22 μF | Tantalum<br>Tantalum<br>Tantalum<br>Tantalum |

| Kemet        | T494C106M010AS                                                           | 10 μF                                     | Tantalum                                     |

|              | T494C226M010AS                                                           | 22 μF                                     | Tantalum                                     |

**Table 5. Recommended Capacitors**

Table 6 lists the manufacturers of recommended capacitors. In most applications surface-mount tantalum capacitors will be the right choice. However, ceramic capacitors will provide the lowest output voltage ripple due to their typically lower ESR.

| MANUFACTURER | CAPACITOR TYPE                               | INTERNET        |

|--------------|----------------------------------------------|-----------------|

| Taiyo Yuden  | X7R/X5R ceramic                              | www.t-yuden.com |

| AVX          | X7R/X5R ceramic<br>TPS-series tantalum       | www.avxcorp.com |

| Sprague      | 595D–series tantalum<br>593D–series tantalum | www.vishay.com  |

| Kemet        | T494-series tantalum                         | www.kemet.com   |

**Table 6. Recommended Capacitor Manufacturers**

### power dissipation

The power dissipated in the TPS60100 depends on output current and is approximated by:

$$P_{DISS} = I_{O} \times (2 V_{IN} - V_{O})$$

for  $I_{O} < < I_{O}$

P<sub>DISS</sub> must be less than that allowed by the package rating. See the ratings for 20-PowerPAD<sup>™</sup> package power-dissipation limits and deratings.

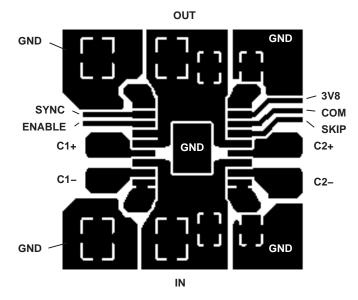

#### layout

All capacitors should be soldered in close proximity to the IC. A PCB layout proposal for a two-layer board is given in Figure 33. Care has been taken to connect both single-ended charge pumps symmetrically to the load to achive optimized output voltage ripple performance. The proposed layout also provides improved thermal performance as the exposed leadframe is soldered to the PCB. The bottom layer of the PCB is a ground plain only. All ground areas on the PCB should be connected. Connect ground areas on top layer to the bottom layer via through hole connections.

Figure 33. Recommended PCB Layout for TPS60100 (top view)

An evaluation module for the TPS60100 is available and can be ordered under literature code SLVP131 or under product code TPS60100EVM–131.

### applications proposals

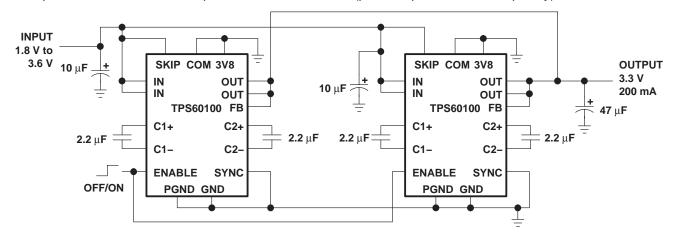

#### paralleling of two TPS60100 to deliver 400 mA

The TPS60100 can be paralleled to yield higher load currents. The circuit of Figure 34 can deliver 400 mA at an output voltage of 3.3 V. It uses two TPS60100 devices in parallel. The devices can share the output capacitors, but each one requires its own transfer capacitors and input capacitor. For best performance, the paralleled devices should operate in the same mode (pulse-skip or constant frequency).

Figure 34. Paralleling of Two TPS60100

#### TPS60100 with LC output filter for ultra low ripple

For applications where extremely low output ripple is required, a small LC filter is recommended. This is shown in Figure 35. The addition of a small inductor and filter capacitor will reduce the output ripple well below what could be achieved with capacitors alone. The corner frequency of 500 kHz was chosen above the 300 kHz switching frequency to avoid loop stability issues in case the feedback is taken from the output of the LC filter. Leaving the feedback (FB) connection point before the LC filter, the filter capacitance value can be increased to achieve even higher ripple attenuation without affecting stability margin.

Figure 35. TPS60100 With LC Filter for Ultra Low Output Ripple Applications

## TPS60100 REGULATED 3.3 V 200-mA LOW-NOISE CHARGE PUMP DC/DC CONVERTER

SLVS213B - MAY 1999 - REVISED SEPTEMBER 1999

### **APPLICATION INFORMATION**

#### related information

#### application reports

For more application information see:

- PowerPAD<sup>TM</sup> Application Report (Literature Number: SLMA002)

- TPS6010x/TPS6011x Charge Pump Application Report (Literature Number: SLVA070)

### device family products

Other devices in this family are:

| PART NUMBER | LITERATURE<br>NUMBER | DESCRIPTION                                                   |

|-------------|----------------------|---------------------------------------------------------------|

| TPS60101    | SLVS214              | Regulated 3.3-V, 100-mA Low-Noise Charge Pump DC/DC Converter |

| TPS60110    | SLVS215              | Regulated 5-V, 300-mA Low-Noise Charge Pump DC/DC Converter   |

| TPS60111    | SLVS216              | Regulated 5-V, 150-mA Low-Noise Charge Pump DC/DC Converter   |

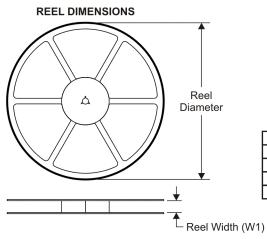

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS60100PWP      | ACTIVE                | HTSSOP          | PWP                | 20   | 70             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPG4    | ACTIVE                | HTSSOP          | PWP                | 20   | 70             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPR     | ACTIVE                | HTSSOP          | PWP                | 20   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 20   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

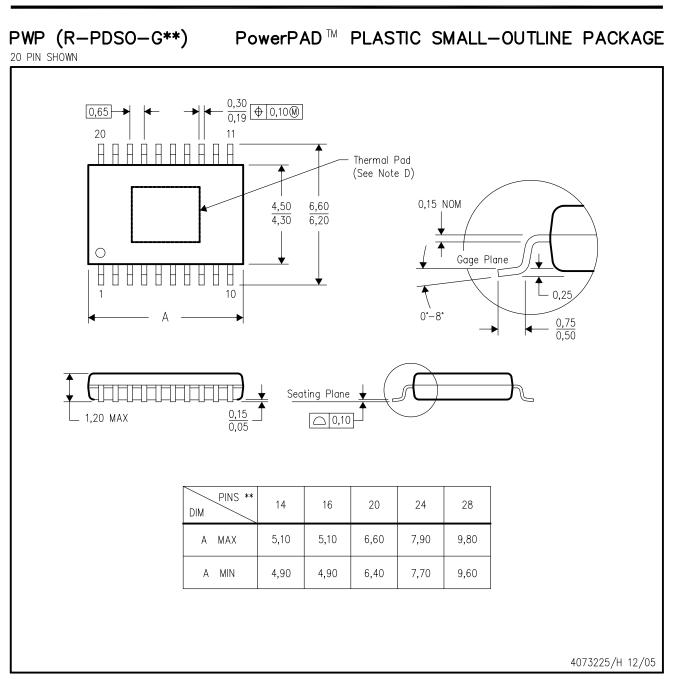

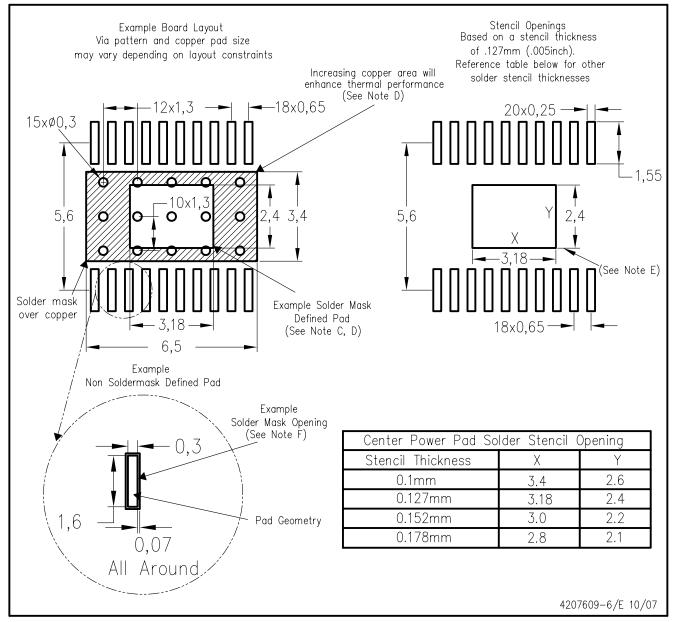

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS60100PWP      | ACTIVE                | HTSSOP          | PWP                | 20   | 70             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPG4    | ACTIVE                | HTSSOP          | PWP                | 20   | 70             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPR     | ACTIVE                | HTSSOP          | PWP                | 20   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60100PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 20   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

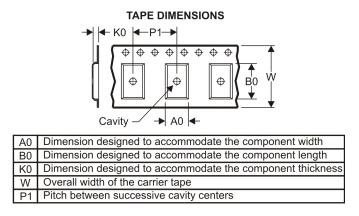

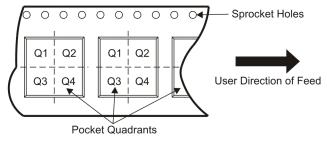

### TAPE AND REEL INFORMATION

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal | *All | dimensions | are | nominal |

|-----------------------------|------|------------|-----|---------|

|-----------------------------|------|------------|-----|---------|

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS60100PWPR | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95    | 7.1     | 1.6     | 8.0        | 16.0      | Q1               |

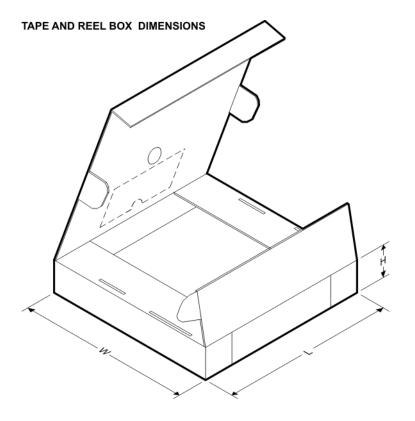

# PACKAGE MATERIALS INFORMATION

11-Mar-2008

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS60100PWPR | HTSSOP       | PWP             | 20   | 2000 | 346.0       | 346.0      | 33.0        |

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

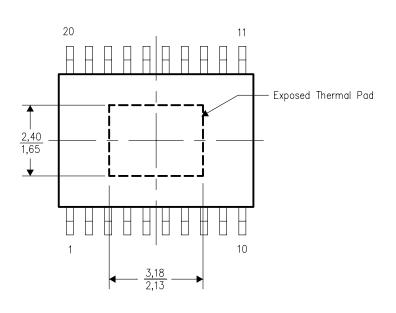

# THERMAL PAD MECHANICAL DATA

# PWP (R-PDSO-G20)

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

## LAND PATTERN

# PWP (R-PDSO-G20) PowerPAD™

NOTES:

A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated