# LM49321

LM49321 Audio Sub-System with Stereo DAC, Mono Class AB Loudspeaker

Amplifier, OCL/SE Stereo Headphone Output and RF Suppression

Literature Number: SNAS457B

### LM49321

**Boomer**® Audio Power Amplifier Series

# Audio Sub-System with Stereo DAC, Mono Class AB Loudspeaker Amplifier, OCL/SE Stereo Headphone Output and RF Suppression

### **General Description**

The LM49321 is an integrated audio sub-system designed for mono voice, stereo music cell phones connecting to base band processors with mono differential analog voice paths. Operating on a 3.3V supply, it combines a mono speaker amplifier delivering 520mW into an  $8\Omega$  load, a stereo headphone amplifier delivering 36mW per channel into a 32 $\Omega$  load, and a mono earpiece amplifier delivering 55mW into a  $32\Omega$  load. The headphone amplifier can be configured for output capacitor-less (OCL) or single-ended (SE) mode. It integrates the audio amplifiers, volume control, mixer, and power management control all into a single package. In addition, the LM49321 routes and mixes the single-ended stereo and differential mono inputs into multiple distinct output modes. The LM49321 features an I2S serial interface for full range audio and an I2C or SPI compatible interface for control. The full range music path features an SNR of 85dB with up to 192kHz playback.

Boomer audio power amplifiers are designed specifically to provide high quality output power with a minimal amount of external components.

### **Key Specifications**

| P <sub>OUT</sub> LS, 8Ω, 3.3V, 1% THD+N                        | 520mvv (typ) |

|----------------------------------------------------------------|--------------|

| $lacksquare$ P <sub>OUT</sub> HP, 32 $\Omega$ , 3.3V, 1% THD+N | 36mW (typ)   |

| ■ P <sub>OUT</sub> Mono Earpiece, 32Ω<br>1% THD+N              | 55mW (typ)   |

| ■ Shutdown current                                             | 0.6µA (typ)  |

| ■ SNR (DAC + Amplifier)                                        | 85dB (typ)   |

August 31, 2009

### **Features**

- 18-bit stereo DAC with up to 192kHz sampling rate

- Multiple distinct output modes

- Mono class AB speaker amplifier

- Stereo OCL/SE headphone amplifier

- Mono earpiece amplifier

- Differential mono analog input

- Single-ended analog inputs

- Independent loudspeaker, headphone and mono earpiece volume controls

- I<sup>2</sup>C/SPI (selectable) compatible interface

- Ultra low shutdown current

- Click and Pop Suppression circuit

# **Applications**

- Cell Phones

- PDAs

- Laptop computers

- Portable devices

Boomer® is a registered trademark of National Semiconductor Corporation.

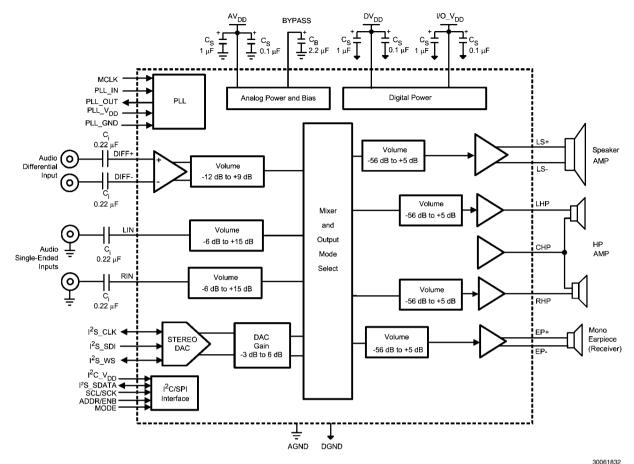

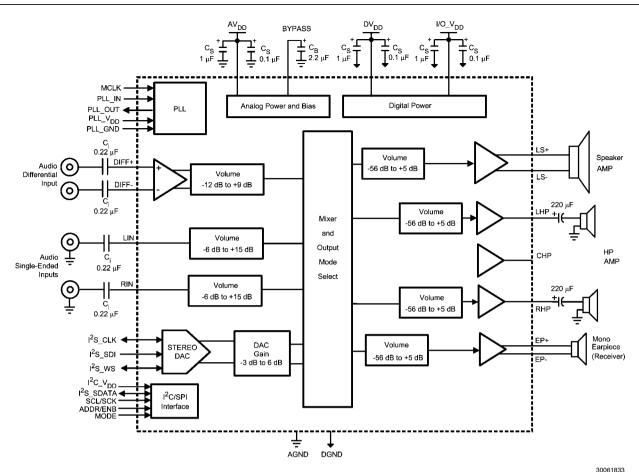

# **Block Diagram**

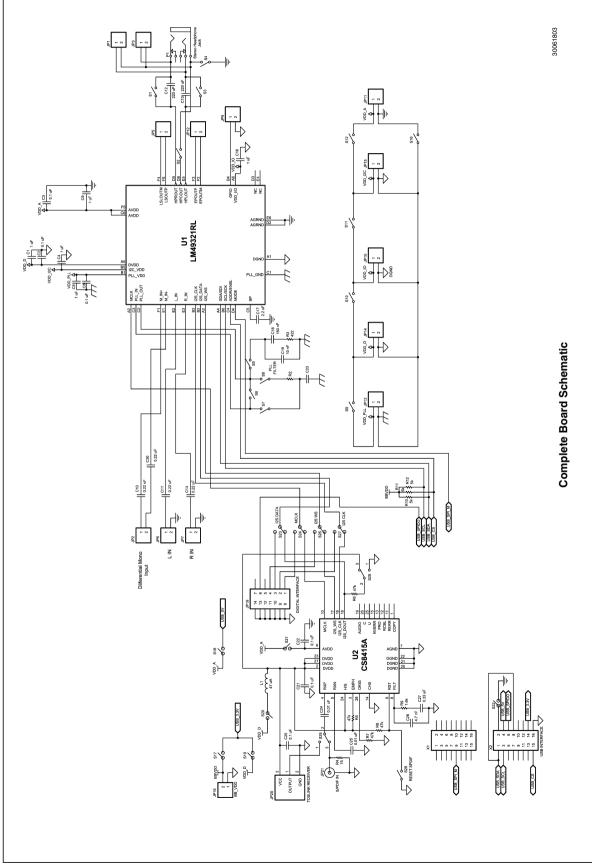

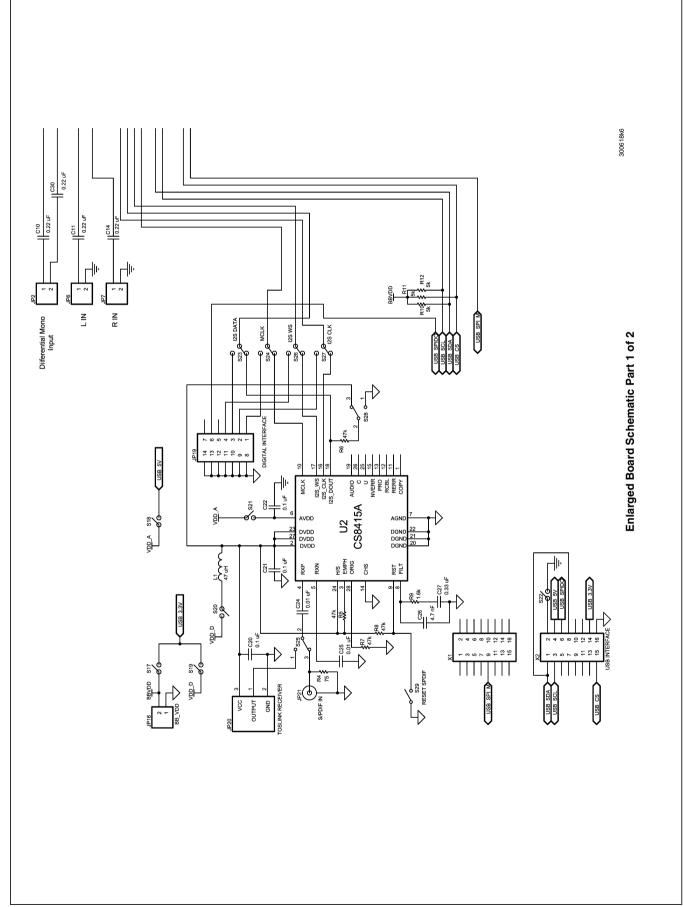

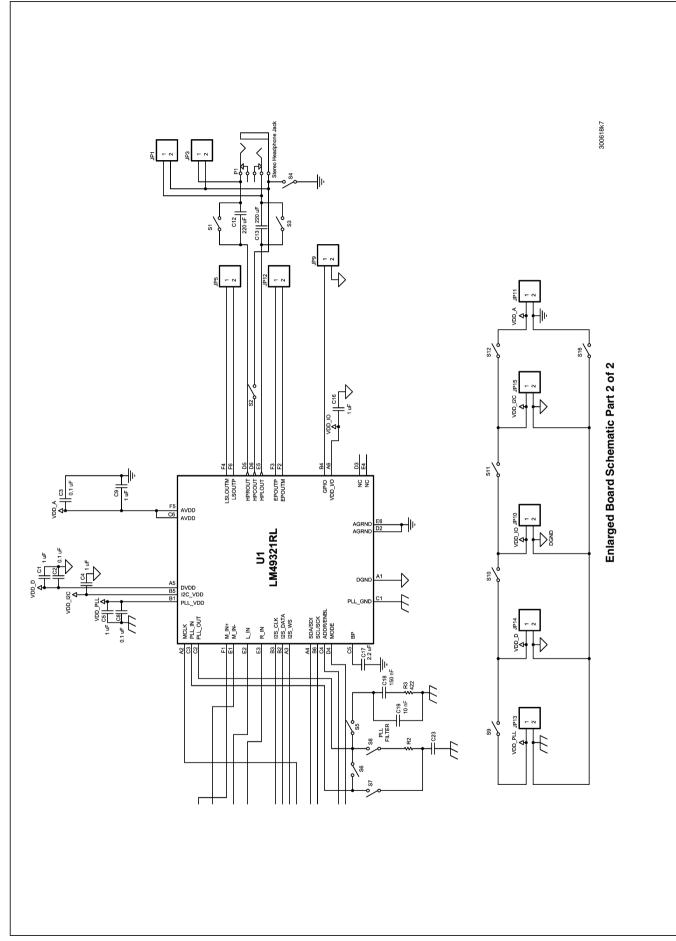

FIGURE 1A: Typical Audio Amplifier Subsystem Application circuit with Output Capacitor-less (OCL) Headphone configuration

FIGURE 1B: Typical Audio Amplifier Subsystem Application circuit with Cap-C`oupled single-ended (SE) Headphone configuration

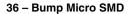

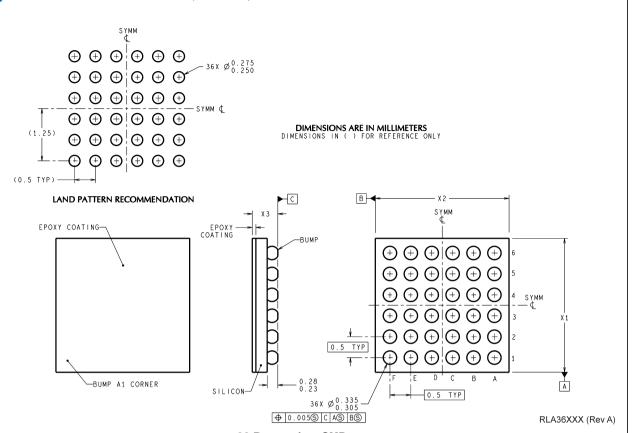

# **Connection Diagrams**

Top View (Bump Side Down)

Order Number LM49321RL

See NS Package Number RLA36LVA

36 – Bump Micro SMD Top Marking Drawing

30061802

Top View

XY — 2 Digit Date Code

TT — Die Traceability

G — Boomer Family

K9 — LM49321RL

# **Pin Descriptions**

| Pin | Pin Name                         | Digital/<br>Analog | I/O, Power | Description                                           |

|-----|----------------------------------|--------------------|------------|-------------------------------------------------------|

| A1  | DGND                             | D                  | Р          | DIGITAL GND                                           |

| A2  | MCLK                             | D                  | I          | MASTER CLOCK                                          |

| A3  | I2S_WS                           | D                  | I/O        | I2S WORD SELECT                                       |

| A4  | SDA/SDI                          | D                  | I/O        | I <sup>2</sup> C SDA OR SPI SDI                       |

| A5  | $DV_DD$                          | D                  | Р          | DIGITAL SUPPLY VOLTAGE                                |

| A6  | I/O_V <sub>DD</sub>              | D                  | Р          | I/O SUPPLY VOLTAGE                                    |

| B1  | PLL_VDD                          | D                  | Р          | PLL SUPPLY VOLTAGE                                    |

| B2  | I2S_SDATA                        | D                  | I          | I <sup>2</sup> S SERIAL DATA INPUT                    |

| В3  | I2S_CLK                          | D                  | I/O        | I <sup>2</sup> S CLOCK SIGNAL                         |

| B4  | GPIO                             | D                  | 0          | TEST PIN (MUST BE LEFT FLOATING)                      |

| B5  | I <sup>2</sup> C_V <sub>DD</sub> | D                  | Р          | I <sup>2</sup> C SUPPLY VOLTAGE                       |

| B6  | SDL/SCK                          | D                  | I          | I <sup>2</sup> C_SCL OR SPI_SCK                       |

| C1  | PLL_GND                          | D                  | Р          | PHASE LOCK LOOP GROUND                                |

| C2  | PLL_OUT                          | D                  | 0          | PHASE LOCK LOOP FILTER OUTPUT                         |

| СЗ  | PLL_IN                           | D                  | I          | PLL FILTER INPUT                                      |

| C4  | ADDR/ENB                         | D                  | I          | I <sup>2</sup> C ADDRESS OR SPI ENB DEPENDING ON MODE |

| C5  | BYPASS                           | Α                  | I          | HALF-SUPPLY BYPASS                                    |

| C6  | AV <sub>DD</sub>                 | Α                  | Р          | ANALOG SUPPLY VOLTAGE                                 |

| D1  | AGND                             | Α                  | Р          | ANALOG GROUND                                         |

| D2  | AGND                             | Α                  | Р          | ANALOG GROUND                                         |

| D3  | NC                               |                    |            | NO CONNECT (MUST BE LEFT FLOATING)                    |

| D4  | MODE                             | D                  | I          | SELECTS BETWEEN I2C OR SPI CONTROL                    |

| D5  | RHP                              | Α                  | 0          | RIGHT HEADPHONE OUTPUT                                |

| D6  | CHP                              | Α                  | 0          | HEADPHONE CENTER PIN OUTPUT (1/2 VDD or GND)          |

| E1  | DIFF-                            | Α                  | I          | ANALOG NEGATIVE DIFFERENTIAL INPUT                    |

| E2  | LIN                              | Α                  | I          | ANALOG LEFT CHANNEL INPUT                             |

| E3  | RIN                              | Α                  | I          | ANALOG RIGHT CHANNEL INPUT                            |

| E4  | NC                               |                    |            | NO CONNECT (MUST BE LEFT FLOATING)                    |

| E5  | LHP                              | Α                  | 0          | LEFT HEADPHONE OUTPUT                                 |

| E6  | AGND                             | Α                  | Р          | ANALOG GROUND                                         |

| F1  | DIFF+                            | Α                  | I          | ANALOG POSITIVE DIFFERENTIAL INPUT                    |

| F2  | EP-                              | Α                  | 0          | MONO EARPIECE- OUTPUT                                 |

| F3  | EP+                              | Α                  | 0          | MONO EARPIECE+ OUTPUT                                 |

| F4  | LS-                              | Α                  | 0          | LOUDSPEAKER OUTPUT-                                   |

| F5  | AV <sub>DD</sub>                 | Α                  | Р          | ANALOG SUPPLY VOLTAGE                                 |

| F6  | LS+                              | Α                  | 0          | LOUDSPEAKER OUTPUT+                                   |

### **Absolute Maximum Ratings** (Note 1, Note

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Analog Supply Voltage (Note 1) 6.0V Digital Supply Voltage (Note 1) 6.0V Storage Temperature -65°C to +150°C Input Voltage -0.3V to  $V_{DD}$  +0.3V Power Dissipation (Note 3) Internally Limited ESD Ratings (Note 4) ESD Ratings (Note 5) 200V Junction Temperature (T<sub>JMAX</sub>) 150°C Thermal Resistance

$\theta_{JA}$  (RLA36) 100°C/W Soldering Information See AN-1279 "Microfill Wafer Level Underfilled Chip Scale package."

### **Operating Ratings** (Note 1, Note 2)

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$   $-40^{\circ}C \le T_A \le +85^{\circ}C$

Supply Voltage

$2.7V \le AV_{DD} \le 5.5V$   $2.7V \le DV_{DD} \le 4.0V$   $1.7V \le I^2C_{-}V_{DD} \le 4.0V$  $1.7V \le I/O_{-}V_{DD} \le 4.0V$

# Audio Amplifier Electrical Characteristics $AV_{DD} = 3.0V$ , $DV_{DD} = 3.0V$ (Note 1, Note

*2*)

The following specifications apply for the circuit shown in Figure 1 with all programmable gain set at 0dB, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                     |                                 |                                                                                                                  | LM49321          |                    | Units                      |  |

|---------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------|------------------|--------------------|----------------------------|--|

| Symbol              | Parameter                       | Conditions                                                                                                       | Typical (Note 6) | Limits<br>(Note 7) | (Limits)                   |  |

|                     |                                 | V <sub>IN</sub> = 0, No Load<br>All Amps On + DAC, OCL (Note 10)                                                 | 13               | 18                 | mA (max)                   |  |

|                     |                                 | Headphone Mode Only, OCL, DAC off                                                                                | 4.6              | 6.25               | mA (max)                   |  |

|                     |                                 | Headphone Mode Only, OCL, DAC Off<br>STEREO_OUTPUT_ONLY = 1,<br>STEREO_INPUT_ONLY = 1                            | 4                | 5.5                | mA                         |  |

| I <sub>DD</sub>     | Supply Current                  | Headphone Mode only OCL, DAC On,<br>OSR = 64, DAC_INPUT_ONLY = 1<br>STEREO_OUTPUT_ONLY = 1                       | 7.5              | 10                 | mA (max)                   |  |

|                     |                                 | Mono Loudspeaker Mode Only (Note 11)                                                                             | 6.5              | 11.5               | mA (max)                   |  |

|                     |                                 | Mono Earpiece Speaker Mode Only MONO_ONLY = 1 (register 01h) MONO_ONLY = 0  DAC Off, All Amps On (OCL) (Note 10) | 3.7<br>3.3<br>10 | 5 13.5             | mA (max)<br>mA<br>mA (max) |  |

| ı                   | Shutdown Current                | (Note 8)                                                                                                         | 0.6              | 1                  | ` ′                        |  |

| I <sub>SD</sub>     | Shutdown Current                | ,                                                                                                                |                  | <u> </u>           | μA (max)                   |  |

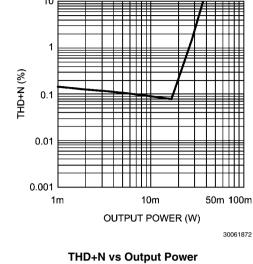

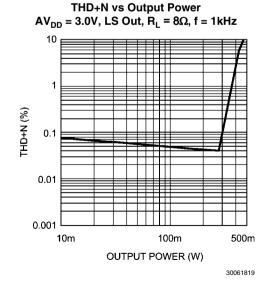

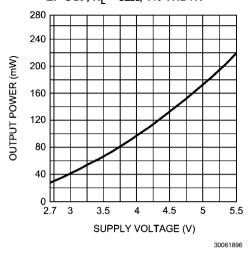

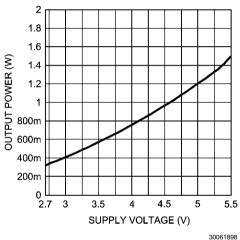

| Б                   | Output Power                    | Speaker; THD = 1%; $f = 1kHz$ , $8\Omega$ BTL                                                                    | 420              | 370                | mW (min)                   |  |

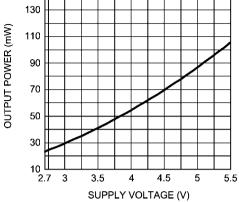

| $P_{O}$             |                                 | Headphone; THD = 1%; $f = 1kHz$ , $32\Omega$ SE                                                                  | 27               | 24                 | mW (min)                   |  |

| M                   | 5 110 1 5400 1 1                | Earpiece; THD = 1%; f = 1kHz, 32Ω BTL                                                                            | 45               | 40                 | mW (min)                   |  |

| V <sub>FS DAC</sub> | Full Scale DAC Output           |                                                                                                                  | 2.4              |                    | V <sub>RMS</sub>           |  |

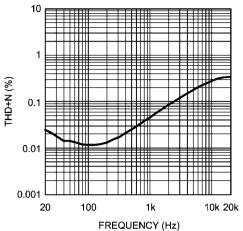

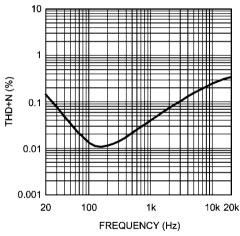

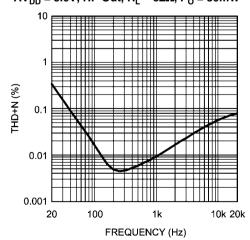

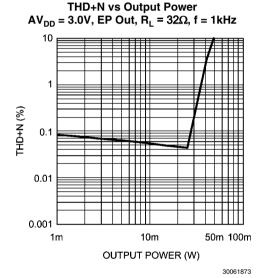

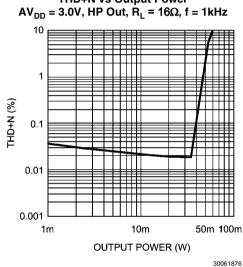

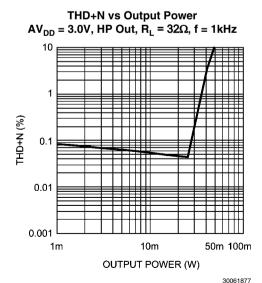

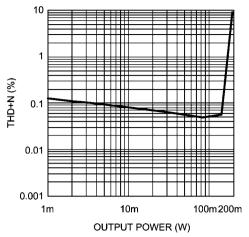

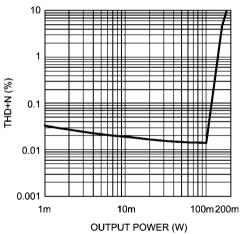

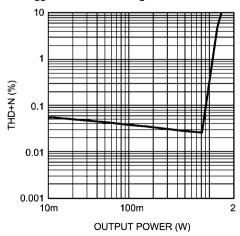

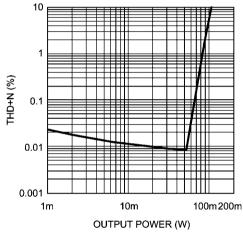

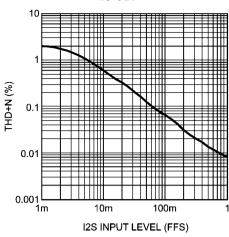

|                     |                                 | Speaker; $P_O = 200$ mW;<br>$f = 1$ kHz, $8\Omega$ BTL                                                           | 0.04             |                    | %                          |  |

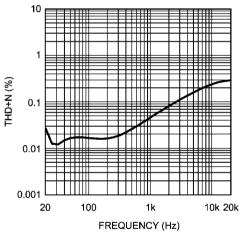

| THD+N               | Total Harmonic Distortion+Noise | Headphone; $P_0 = 10$ mW; $f = 1$ kHz, $32\Omega$ SE                                                             | 0.01             |                    | %                          |  |

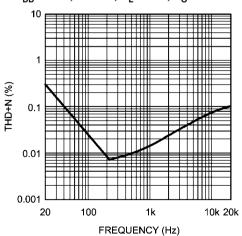

|                     |                                 | Earpiece; $P_O = 20$ mW;<br>$f = 1$ kHz, $32\Omega$ BTL                                                          | 0.04             |                    | %                          |  |

|                     |                                 | Speaker                                                                                                          | 10               | 55                 | mV (max)                   |  |

| V <sub>os</sub>     | Offset Voltage                  | Earpiece                                                                                                         | 8                | 50                 | mV (max)                   |  |

|                     |                                 | Headphone (OCL)                                                                                                  | 8                | 15                 | mV (max)                   |  |

| ∈o                  | Output Noise                    | A-weighted; 0dB gain                                                                                             | Table 1          |                    |                            |  |

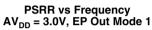

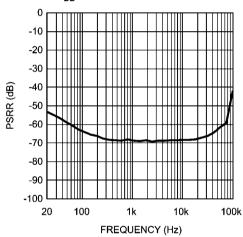

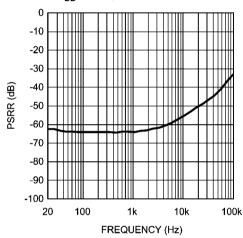

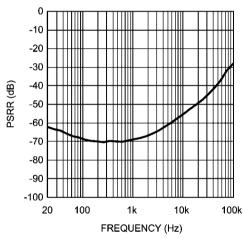

| PSRR                | Power Supply Rejection Ratio    | $f = 217Hz; V_{RIPPLE} = 200mV_{P-P}$<br>$C_B = 2.2\mu F$                                                        | Table 2          |                    |                            |  |

|                   |                             |                                                   | LM49321          |                    | 11                |

|-------------------|-----------------------------|---------------------------------------------------|------------------|--------------------|-------------------|

| Symbol            | Parameter                   | Conditions                                        | Typical (Note 6) | Limits<br>(Note 7) | Units<br>(Limits) |

| X <sub>TALK</sub> | Crosstalk                   | Headphone; P <sub>O</sub> = 10mW, f = 1kHz; OCL   | -60              |                    | dB                |

|                   | Moke He Time                | $C_B = 2.2 \mu F, CD_6 = 0$                       | 35               |                    | ms                |

| I <sub>WU</sub>   | Wake-Up Time                | C <sub>B</sub> = 2.2μF, CD_6 = 1                  | 85               |                    | ms                |

| CMRR              | Common-Mode Rejection Ratio | f = 217Hz, V <sub>RMS</sub> = 200mV <sub>PP</sub> | 56               |                    | dB                |

# Audio Amplifier Electrical Characteristics $AV_{DD} = 5.0V$ , $DV_{DD} = 3.3V$ (Note 1, Note

**2**)

The following specifications apply for the circuit shown in Figure 1 with all programmable gain set at 0dB, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                     |                                   |                                                                                             | LM49321                                           |                 | Units            |

|---------------------|-----------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|------------------|

| Symbol              | Parameter                         | Conditions                                                                                  | Typical (Note 6)                                  | Limits (Note 7) | (Limits)         |

|                     |                                   | V <sub>IN</sub> = 0, No Load<br>All Amps On + DAC, OCL (Note 10)                            | 17.5                                              |                 | mA (max)         |

|                     |                                   | Headphone Mode Only, OCL, DAC Off                                                           | 5.8                                               |                 | mA (max)         |

| 1                   | Complex Comment                   | Headphone Mode Only, OCL, DAC Off<br>STEREO_OUTPUT_ONLY = 1,<br>STEREO_INPUT_ONLY = 1       | 5.5                                               |                 | mA               |

| DD                  | Supply Current                    | Headphone Mode Only, OCL, DAC On,<br>OSR = 64, DAC_INPUT_ONLY = 1<br>STEREO_OUTPUT_ONLY = 1 | 9.5                                               |                 | mA               |

|                     |                                   | Mono Loudspeaker Mode Only (Note 10)                                                        | 11.6                                              |                 | mA               |

|                     |                                   | Mono Earpiece Mode Only (Note 10)                                                           | 5                                                 |                 | mA               |

|                     |                                   | DAC Off, All Amps On (OCL) (Note 10)                                                        | 12.9                                              |                 | mA               |

| I <sub>SD</sub>     | Shutdown Current                  | (Note 8)                                                                                    | 1.6                                               |                 | μΑ               |

|                     |                                   | Speaker; THD = 1%;<br>$f = 1kHz$ , $8\Omega$ BTL                                            | 1.25                                              |                 | mW               |

| P <sub>o</sub>      | Output Power                      | Headphone; THD = 1%; $f = 1kHz$ , $32\Omega$ SE                                             | 80                                                |                 | mW               |

|                     |                                   | Earpiece; THD = 1%;<br>f = 1kHz, 32Ω BTL                                                    | 175                                               |                 | mW               |

| V <sub>FS DAC</sub> | Full Scale DAC Output             |                                                                                             | 2.4                                               |                 | V <sub>RMS</sub> |

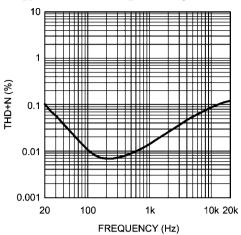

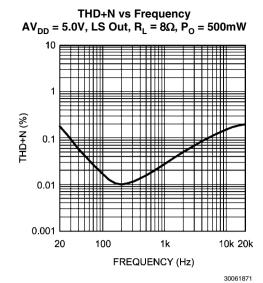

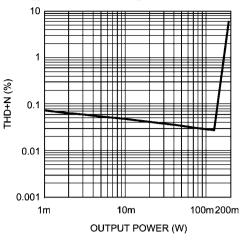

|                     |                                   | Speaker; $P_O = 500$ mW;<br>$f = 1$ kHz, $8\Omega$ BTL                                      | 0.03                                              |                 | %                |

| THD+N               | Total Harmonic Distortion + Noise | Headphone; $P_O = 30$ mW; $f = 1$ kHz, $32\Omega$ SE                                        | 0.01                                              |                 | %                |

|                     |                                   | Earpiece; $P_O = 40$ mW; $f = 1$ kHz, $32\Omega$ BTL                                        | 0.04                                              |                 | %                |

|                     |                                   | Speaker                                                                                     | 10                                                |                 | mV               |

| V <sub>os</sub>     | Offset Voltage                    | Earpiece                                                                                    | 8                                                 |                 | mV               |

|                     |                                   | HP (OCL)                                                                                    | 8                                                 |                 | mV               |

| = <sub>0</sub>      | Output Noise                      | A-weighted; 0dB gain;                                                                       | Table 1                                           |                 |                  |

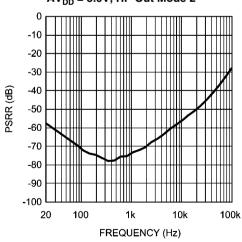

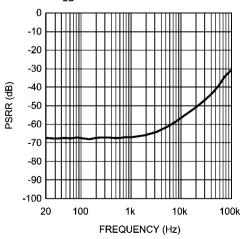

| PSRR                | Power Supply Rejection Ratio      | $f = 217Hz; V_{ripple} = 200mV_{P-P}$ $C_B = 2.2\mu F$                                      | 217Hz; V <sub>ripple</sub> = 200mV <sub>P-P</sub> |                 |                  |

| X <sub>TALK</sub>   | Crosstalk                         | Headphone; P <sub>O</sub> = 15mW, f = 1kHz; OCL                                             | -56                                               |                 | dB               |

|                     |                                   | $C_B = 2.2 \mu F, CD_6 = 0$                                                                 | 45                                                |                 | ms               |

| $T_{WU}$            | Wake-Up Time                      | $C_B = 2.2 \mu F, CD_6 = 1$                                                                 | 130                                               |                 | ms               |

### **Volume Control Electrical Characteristics** (Note 1, Note 2)

The following specifications apply for  $3.0V \le AV_{DD} \le 5.0V$  and  $2.7V \le DV_{DD} \le 4.0V$ , unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                     |                                                          |                                                                          | LM49321          |                    | Units    |  |

|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------|------------------|--------------------|----------|--|

| Symbol              | Parameter                                                | Conditions                                                               | Typical (Note 6) | Limits<br>(Note 7) | (Limits) |  |

|                     |                                                          | minimum gain aatting                                                     | -6               | -7                 | dB (min) |  |

|                     | Stereo Analog Inputs Pre-Amp Gain                        | minimum gain setting                                                     | -6               | <b>-</b> 5         | dB (max) |  |

|                     | Setting Range                                            | maximum gain cotting                                                     | 15               | 15.5               | dB (max) |  |

| PGR                 |                                                          | maximum gain setting                                                     | 15               | 14.5               | dB (min) |  |

| run                 |                                                          | minimum gain setting                                                     | -12              | -13                | dB (min) |  |

|                     | Differential Mono Analog Input Pre-                      | Thininian gain setting                                                   | -12              | -11                | dB (max) |  |

|                     | Amp Gain Setting Range                                   | maximum gain setting                                                     | 9                | 9.5                | dB (max) |  |

|                     |                                                          |                                                                          |                  | 8.5                | dB (min) |  |

|                     |                                                          | minimum gain setting                                                     | -56              | <b>–</b> 59        | dB (min) |  |

| VCR                 | Output Volume Control for Loudspeaker, Headphone Output, |                                                                          |                  | <b>-</b> 53        | dB (max) |  |

| VCh                 | or Earpiece Output                                       | maximum gain setting                                                     | +5               | 4.5                | dB (min) |  |

|                     | or Earpiess Surpur                                       |                                                                          |                  | 5.5                | dB (max) |  |

| ΔA <sub>CH-CH</sub> | Stereo Channel to Channel Gain<br>Mismatch               |                                                                          | 0.3              |                    | dB       |  |

| A <sub>MUTE</sub>   | Mute Attenuation                                         | V <sub>IN</sub> = 1V <sub>RMS</sub> , Gain = 0dB<br>with load, Headphone | -90              |                    | dB       |  |

|                     | DIFF+, DIFF-, L <sub>IN</sub> and R <sub>IN</sub> Input  |                                                                          |                  | 18                 | kΩ (min) |  |

| R <sub>INPUT</sub>  | Impedance                                                |                                                                          | 23               | 28                 | kΩ (max) |  |

# Digital Section Electrical Characteristics (Note 1, Note 2)

The following specifications apply for  $3.0V \le AV_{DD} \le 5.0V$  and  $2.7V \le DV_{DD} \le 4.0V$ , unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                            |                                              |                                                                                   | LM49321          |                    |                   |  |

|----------------------------|----------------------------------------------|-----------------------------------------------------------------------------------|------------------|--------------------|-------------------|--|

| Symbol                     | Parameter                                    | Conditions                                                                        | Typical (Note 6) | Limits<br>(Note 7) | Units<br>(Limits) |  |

| DI                         | District Chartelesses Comment                | Mode 0, DV <sub>DD</sub> = 3.0V                                                   |                  |                    |                   |  |

| DI <sub>SD</sub>           | Digital Shutdown Current                     | No MCLK                                                                           | 0.01             |                    | μΑ                |  |

| DI <sub>DD</sub>           | Digital Power Supply Current                 | $f_{MCLK} = 12MHz, DV_{DD} = 3.0V$<br>ALL MODES EXCEPT 0                          | 5.3              | 6.5                | mA (max           |  |

| PLLI <sub>DD</sub>         | PLL Quiescent Current                        | $f_{MCLK} = 12MHz, DV_{DD} = 3.0V$                                                | 4.8              | 6                  | mA (max           |  |

| Audio DAC                  | (Typical numbers are with 6.144MHz           | z audio clock and 48kHz sampling frequenc                                         | у                |                    |                   |  |

| R <sub>DAC</sub>           | Audio DAC Ripple                             | 20Hz - 20kHz through headphone output                                             | +/-0.1           |                    | dB                |  |

| PB <sub>DAC</sub>          | Audio DAC Passband width                     | -3dB point                                                                        | 22.6             |                    | kHz               |  |

| SBA <sub>DAC</sub>         | Audio DAC Stop band Attenuation              | Above 24kHz                                                                       | 76               |                    | dB                |  |

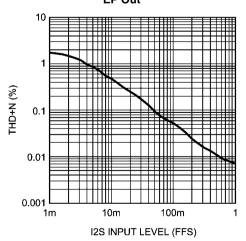

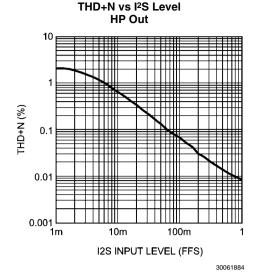

| DR <sub>DAC</sub>          | Audio DAC Dynamic Range                      | DC - 20kHz, -60dBFS; AES17 Standard                                               | Table 4          |                    | dB                |  |

| SNR                        | Audio DAC-AMP Signal to Noise Ratio          | A-Weighted, Signal = $V_O$ at 0dBFS, f = 1kHz<br>Noise = digital zero, A-weighted | Table 4          |                    | dB                |  |

| SNR <sub>DAC</sub>         | Internal DAC SNR                             | A-weighted (Note 9)                                                               | 95               |                    | dB                |  |

| PLL                        | •                                            |                                                                                   |                  |                    |                   |  |

| f                          | Input Frequency on MCLK pin                  |                                                                                   | 12               | 10                 | MHz               |  |

| f <sub>IN</sub>            | Input Frequency on MCER pin                  |                                                                                   | 12               | 26                 | IVITZ             |  |

| SPI/I <sup>2</sup> C (1.7\ | / ≤ I <sup>2</sup> C_V <sub>DD</sub> ≤ 2.2V) |                                                                                   |                  |                    |                   |  |

| f <sub>SPI</sub>           | Maximum SPI Frequency                        |                                                                                   |                  | 1000               | kHz (max          |  |

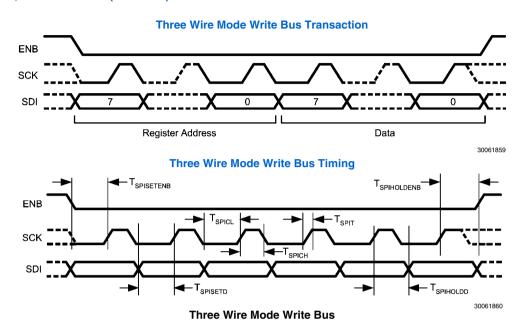

| t <sub>SPISETD</sub>       | SPI Data Setup Time                          |                                                                                   |                  | 250                | ns (max           |  |

| t <sub>SPISETENB</sub>     | SPI ENB Setup Time                           |                                                                                   |                  | 250                | ns (max)          |  |

|                           |                                              | LM49321                         |                                  | 19321                                      | Haita              |

|---------------------------|----------------------------------------------|---------------------------------|----------------------------------|--------------------------------------------|--------------------|

| Symbol                    | Parameter                                    | Conditions                      | Typical (Note 6)                 | Limits (Note 7)                            | Units<br>(Limits)  |

|                           | SPI Data Hold Time                           |                                 | (Note 0)                         | 250                                        | ns (max)           |

| SPIHOLDD                  | SPI ENB Hold Time                            |                                 |                                  | 250                                        | ns (max)           |

| SPIHOLDENB                | SPI Clock Low Time                           |                                 |                                  | 500                                        | ns (max            |

| SPICL                     | SPI Clock High Time                          |                                 |                                  | 500                                        | ns (max            |

| SPICH                     | I <sup>2</sup> C_CLK Frequency               |                                 |                                  | 400                                        | kHz (max           |

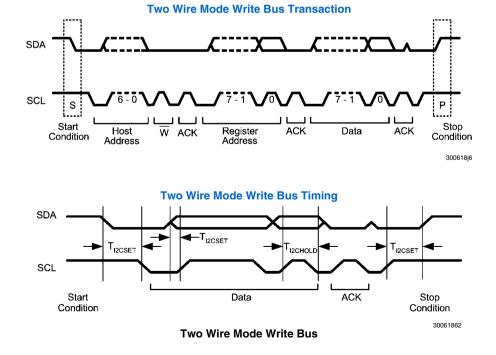

| CLKI2C                    | I <sup>2</sup> C_DATA Hold Time              |                                 |                                  | 250                                        | ns (max            |

| 2CHOLD                    | I <sup>2</sup> C_DATA Setup Time             |                                 |                                  | 250                                        | ns (max            |

| I2CSET                    | I <sup>2</sup> C/SPI Input High Voltage      |                                 | I <sup>2</sup> C_V <sub>DD</sub> | 0.7 x<br>I <sup>2</sup> C_V <sub>DD</sub>  | V (min)            |

| / <sub>IL</sub>           | I <sup>2</sup> C/SPI Input Low Voltage       |                                 | 0                                | 0.25 x<br>I <sup>2</sup> C_V <sub>DD</sub> | V (max)            |

| PI/I <sup>2</sup> C (2.2V | ' ≤ I <sup>2</sup> C_V <sub>DD</sub> ≤ 4.0V) |                                 | Į.                               |                                            |                    |

| SPI                       | Maximum SPI Frequency                        |                                 |                                  | 4000                                       | kHz (max           |

| SPISETD                   | SPI Data Setup Time                          |                                 |                                  | 100                                        | ns (max            |

| PISETENB                  | SPI ENB Setup Time                           |                                 |                                  | 100                                        | ns (max            |

| SPIHOLDD                  | SPI Data Hold Time                           |                                 |                                  | 100                                        | ns (max            |

| SPIHOLENB                 | SPI ENB Hold Time                            |                                 |                                  | 100                                        | ns (max            |

| SPICL                     | SPI Clock Low Time                           |                                 |                                  | 125                                        | ns (max            |

| PICH                      | SPI Clock High Time                          |                                 |                                  | 125                                        | ns (max            |

| LKI2C                     | I <sup>2</sup> C_CLK Frequency               |                                 |                                  | 400                                        | kHz (ma            |

| 2CHOLD                    | I <sup>2</sup> C_DATA Hold Time              |                                 |                                  | 100                                        | ns (max            |

| 2CSET                     | I <sup>2</sup> C_DATA Setup Time             |                                 |                                  | 100                                        | ns (max            |

| IH                        | I <sup>2</sup> C/SPI Input High Voltage      |                                 | I <sup>2</sup> C_V <sub>DD</sub> | 0.7 x<br>I <sup>2</sup> C_V <sub>DD</sub>  | V (min)            |

| 'IL                       | I <sup>2</sup> C/SPI Input Low Voltage       |                                 | 0                                | 0.3 x<br>I <sup>2</sup> C_V <sub>DD</sub>  | V (max             |

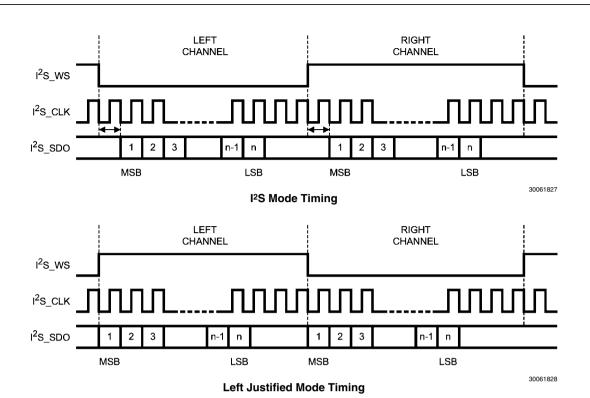

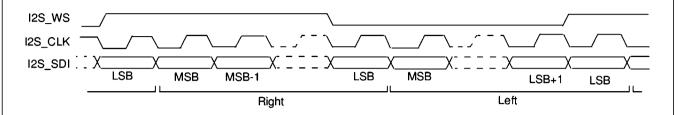

| <sup>2</sup> S (1.7V ≤ I/ | O_V <sub>DD</sub> ≤ 2.7V)                    |                                 | L                                |                                            |                    |

|                           |                                              | I2S_RESOLUTION = 1              | 1536                             | 6144                                       | kHz (max           |

|                           | I2S_CLK Frequency                            | I <sup>2</sup> S_RESOLUTION = 0 | 3072                             | 12288                                      | kHz (ma            |

| CLKI2S                    | I <sup>2</sup> S_WS Duty Cycle               |                                 | 50                               | 40                                         | % (min             |

|                           | 125_WS Duty Cycle                            |                                 | 50                               | 60                                         | % (max             |

| <b>′</b> ін               | Digital Input High Voltage                   |                                 |                                  | 0.75<br>x I/O_V <sub>DD</sub>              | V (min)            |

| / <sub>IL</sub>           | Digital Input Low Voltage                    |                                 |                                  | 0.25 x<br>I/O_V <sub>DD</sub>              | V (max             |

| <sup>2</sup> S (2.7V ≤ I/ | O_V <sub>DD</sub> ≤ 4.0V)                    | •                               | ·                                |                                            |                    |

|                           | I <sup>2</sup> S_CLK Frequency               | I2S_RESOLUTION = 0              | 1536<br>3072                     | 6144<br>12288                              | kHz (ma<br>kHz (ma |

| CLKI2S                    | I <sup>2</sup> S_WS Duty Cycle               | I2S_RESOLUTION = 1              | 50                               | 40<br>60                                   | %<br>%             |

| / <sub>IH</sub>           | Digital Input High Voltage                   |                                 |                                  | 0.7 x<br>I/O_V <sub>DD</sub>               | V (min)            |

| / <sub>IL</sub>           | Digital Input Low Voltage                    |                                 |                                  | 0.3 x<br>I/O_V <sub>DD</sub>               | V (max             |

9

**Note 1:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum RatingsRatings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 3: Maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower.

Note 4: Human body model, applicable std. JESD22-A114C.

Note 5: Machine model, applicable std. JESD22-A115-A.

Note 6: Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the *Recommended Operation Conditions* at the time of product characterization and are not guaranteed.

Note 7: Datasheet min/max specification limits are guaranteed by test or statistical analysis.

Note 8: Shutdown current is measured in a normal room environment.

Note 9: Internal DAC only with DAC modes 00 and 01.

Note 10: Enabling mono bit (MONO\_ONLY in Output Control Register 01h) will save 400µA (typ) form specified current.

### **TABLE 1. Output Noise**

Output Noise  $AV_{DD}$  = 5.0V and  $AV_{DD}$  = 3.0V. All gains set to 0dB. Units in  $\mu$ V, A-weighted, Inputs terminated to ground.

| MODE | EP | LS | HP OCL | Units |

|------|----|----|--------|-------|

| 1    | 22 | 22 | 8      | μV    |

| 2    | 22 | 22 | 8      | μV    |

| 3    | 22 | 22 | 8      | μV    |

| 4    | 68 | 88 | 46     | μV    |

| 5    | 38 | 48 | 24     | μV    |

| 6    | 29 | 34 | 18     | μV    |

| 7    | 38 | 48 | 24     | μV    |

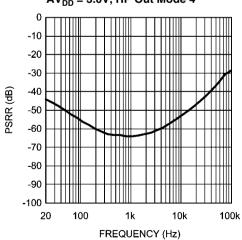

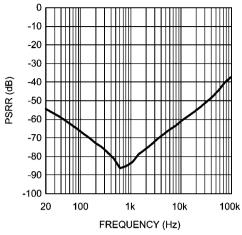

### TABLE 2. PSRR $AV_{DD} = 3.0V$

PSRR AV<sub>DD</sub> = 3.0V,  $f_{RIPPLE}$  = 217Hz;  $V_{RIPPLEe}$  = 200mV<sub>P-P</sub>;  $C_B$  = 2.2 $\mu$ F; All gains set to 0dB..

|      | , IIII I EE | , , , , , , , , , , , , , , , , , , , , | 1-17 0     | . , •    |            |       |

|------|-------------|-----------------------------------------|------------|----------|------------|-------|

| MODE | EP(Typ)     | LS (Typ)                                | LS (Limit) | НР (Тур) | HP (Limit) | Units |

| 1    | 69          | 76                                      |            | 72       |            | dB    |

| 2    | 69          | 76                                      | 67         | 72       | 68         | dB    |

| 3    | 69          | 76                                      |            | 72       |            | dB    |

| 4    | 63          | 62                                      |            | 55       |            | dB    |

| 5    | 69          | 68                                      |            | 61       |            | dB    |

| 6    | 69          | 70                                      |            | 64       |            | dB    |

| 7    | 69          | 68                                      |            | 61       |            | dB    |

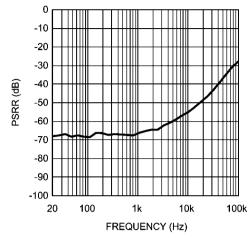

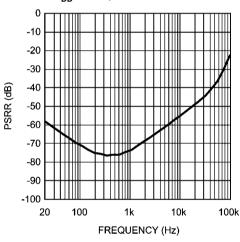

### TABLE 3. PSRR $AV_{DD} = 5.0V$

PSRR AV $_{DD}$  = 5.0V,  $f_{RIPPLE}$  = 217Hz;  $V_{RIPPLE}$  = 200m $V_{P-P}$ ;  $C_{B}$  = 2.2 $\mu$ F; All gains set to 0dB,

|      | 111111111111111111111111111111111111111 | 1-1 - 0  | _ <del></del> |       |

|------|-----------------------------------------|----------|---------------|-------|

| MODE | EP (Typ)                                | LS (Typ) | НР (Тур)      | Units |

| 1    | 68                                      | 72       | 71            | dB    |

| 2    | 68                                      | 72       | 71            | dB    |

| 3    | 68                                      | 72       | 71            | dB    |

| 4    | 68                                      | 66       | 69            | dB    |

| 5    | 68                                      | 69       | 70            | dB    |

| 6    | 69                                      | 72       | 71            | dB    |

| 7    | 68                                      | 69       | 70            | dB    |

### **TABLE 4. Dynamic Range and SNR**

Dynamic Range and SNR. 3.0V  $\leq$  AV<sub>DD</sub>  $\leq$  5.0V. All programmable gain set to 0dB. Units in dB.

|    | DR (Typ) | SNR (Typ) | Units |

|----|----------|-----------|-------|

| LS | 95       | 85        | dB    |

| HP | 95       | 85        | dB    |

| EP | 97       | 85        | dB    |

### **System Control**

The LM49321 is controlled via either a two wire I<sup>2</sup>C compatible interface or three wire SPI interface, selectable with the MODE pin. This interface is used to configure the operating mode, interfaces, data converters, mixers and amplifiers. The LM49321 is controlled by writing 8 bit data into a series of write-only registers, the device is always a slave for both type of interfaces.

### THREE WIRE, SPI INTERFACE (MODE = 1)

When the part is configured as an SPI device and the enable (ENB) line is lowered the serial data on SDI is clocked in on the rising edge of the SCK line. The protocol used is 16bit, MSB first. The upper 8 bits (15:8) are used to select an address within the device, the lower 8 bits (7:0) contain the updated data for this register.

### TWO WIRE I2C COMPATIBLE INTERFACE (MODE = 0)

When the part is configured as an I<sup>2</sup>C device then the LM49321 will respond to one of two addresses, according to the ADDR input. If ADDR is low then the address portion of the I<sup>2</sup>C transaction should be set to write to 0010000. When ADDR is high then the address input should be set to write to 1110000.

### **TABLE 5. Chip Address**

|              | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|--------------|----|----|----|----|----|----|----|----|

| Chip Address | 0  | EC | EC | 1  | 0  | 0  | 0  | 0  |

| ADR = 0      | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| ADR = 1      | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

EC — Externally configured by ADR pin

|                |                                                      |                     |                       | TABLE              | TABLE 6. Control Registers |                 |                   |                    |                                   |

|----------------|------------------------------------------------------|---------------------|-----------------------|--------------------|----------------------------|-----------------|-------------------|--------------------|-----------------------------------|

| Address        | Register                                             | <b>D7</b>           | 9 <b>0</b>            | D2                 | D4                         | EO              | D2                | D1                 | D0                                |

| 00h            | MODE_CONTROL                                         | 0                   | 0_CD_6                | 0                  | OCL                        |                 | MODE              | MODE_CONTROL       |                                   |

| 01h            | OUTPUT_<br>CONTROL                                   | STEREO_<br>OUT_ONLY | MONO_ONLY             | DAC_INPUT_<br>ONLY | STEREO_INPUT_<br>ONLY      | HP_R_<br>OUTPUT | HP_L_<br>OUTPUT   | LS_<br>OUTPUT      | MONO_<br>OUTPUT                   |

| 02h            | EP_VOL                                               | 0                   | 0                     | 0                  |                            |                 | EP_VOL            |                    |                                   |

| 03h            | LS_VOL                                               | 0                   | 0                     | 0                  |                            |                 | TOA_S1            |                    |                                   |

| 04h            | RESERVED                                             | 0                   | 0                     | 0                  | 0                          | 0               | 0                 | 0                  | 0                                 |

| 05h            | HP_L_VOL                                             | 0                   | 0                     | 0                  |                            |                 | HP_L_VOL          |                    |                                   |

| 190            | HP_R_VOL                                             | 0                   | 0                     | 0                  |                            |                 | HP_R_VOL          |                    |                                   |

| 07h            | ANALOG_INPUT<br>_GAIN                                | 0                   | 0                     |                    | ANA_R_GAIN                 |                 |                   | ANA_L_GAIN         |                                   |

| 08h            | ANALOG_DAC<br>_GAIN                                  | 0                   | DAC_                  | R_GAIN             | DAC_L_GAIN                 | _GAIN           |                   | MONO_L_GAIN        |                                   |

| 09h            | CLOCKS                                               |                     |                       | R_DIV              |                            | PLL_<br>ENABLE  | AUDIO<br>_CLK_SEL | PLL_INPUT          | FAST_<br>CLOCK                    |

| 0Ah            | PLL_M                                                | 0                   |                       |                    |                            | $PLL_{-}M$      |                   |                    |                                   |

| 0Bh            |                                                      |                     |                       |                    | PLL_N                      |                 |                   |                    |                                   |

| 9Ch            | PLL_N_MOD                                            | VCO_FAST            | VCO_FAST DITHER_LEVEL | DITHER_LEVEL       |                            |                 | PLL_N_MOD         |                    |                                   |

| ODh            | PLL_P                                                | 0                   | 0                     | 0                  | 0                          |                 | <u>P</u>          | PLL_P              |                                   |

| 0Eh            | DAC_SET UP                                           | 0                   | CUST_COMP             | DITHER_ALW_ON      | DITHER_OFF                 | MUTE_R          | MUTE_L            | DAC_MODE           |                                   |

| 0Fh            | INTERFACE                                            | 0                   | 0                     | 0                  | 0                          | PC_FAST         | I2S_MODE          | I2S_<br>RESOLUTION | I <sup>2</sup> S_MASTER_<br>SLAVE |

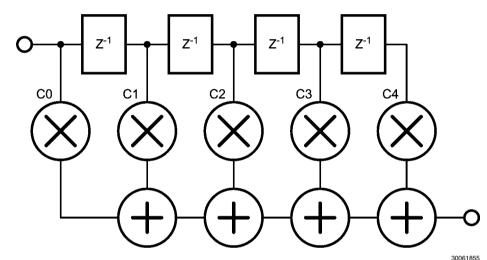

| 10h            |                                                      |                     |                       | COM                | COMPENSATION_C OFFF0_LSB   | F0_LSB          |                   |                    |                                   |

| 11h            |                                                      |                     |                       | COMF               | COMPENSATION_C OEFF0_MSB   | F0_MSB          |                   |                    |                                   |

| 12h            |                                                      |                     |                       | COM                | COMPENSATION _C OEFF1_LSB  | F1_LSB          |                   |                    |                                   |

| 13h            |                                                      |                     |                       | COMF               | COMPENSATION _C OEFF1_MSB  | F1_MSB          |                   |                    |                                   |

| 14h            |                                                      |                     |                       | COMI               | COMPENSATION_C OEFF2_LSB   | F2_LSB          |                   |                    |                                   |

| 15h            |                                                      |                     |                       | COMF               | COMPENSATION _C OEFF2_MSB  | F2_MSB          |                   |                    |                                   |

| Noto: A    100 | Note: All registers default to 0 on initial power-up | DOMOR-IID           |                       |                    |                            |                 |                   |                    |                                   |

Note: All registers default to 0 on initial power-up.

# **Mixer Control Registers**

### **TABLE 7. Mode Control Register (00h)**

This register is used to control the different mixer modes that the LM49321 supports.

| Bits | Field    |                                                                            |             | Desc              | ription                        |                   |                    |

|------|----------|----------------------------------------------------------------------------|-------------|-------------------|--------------------------------|-------------------|--------------------|

| 3:0  | MODE     | This sets the differen                                                     | nt mixer ou | tput modes.       |                                |                   |                    |

|      | _CONTROL | MODE_CONTROL                                                               | Mode        | Mono Earpiece     | Loudspeaker                    | Headphone<br>Left | Headphone<br>Right |

|      |          | 0000                                                                       | 0           | SD                | SD                             | SD                | SD                 |

|      |          | 1001                                                                       | 1           | М                 | М                              | M                 | М                  |

|      |          | 1010                                                                       | 2           | AL+AR             | AL+AR                          | AL                | AR                 |

|      |          | 1011                                                                       | 3           | M+AL+AR           | M+AL+AR                        | M+AL              | M+AR               |

|      |          | 1100                                                                       | 4           | DL+DR             | DL+DR                          | DL                | DR                 |

|      |          | 1101                                                                       | 5           | DL+DR+AL+AR       | DL+DR+AL+AR                    | DL+AL             | DR+AR              |

|      |          | 1110                                                                       | 6           | M+DL+DR+AL<br>+AR | M+DL+DR+AL<br>+AR              | M+DL+AL           | M+DR+AR            |

|      |          | 1111                                                                       | 7           | M+DL+DR           | M+DL+DR                        | M+DL              | M+DR               |

| 4    | OCL      | This sets the headphone output to use output capacitor-less configuration. |             |                   | ration.                        |                   |                    |

|      |          |                                                                            | OCL         |                   | Headphone output configuration |                   | juration           |

|      |          |                                                                            | 0           |                   | Cap-couple                     | ed Single-ended I | Mode (SE)          |

|      |          |                                                                            | 1           |                   | Output capacitor-less (OCL)    |                   |                    |

SD — Shutdown

M — Mono Differential Input

AL — Analog Left Channel AR — Analog Right Channel DL — I<sup>2</sup>S DAC Left Channel

DR — I2S DAC Right Channel Note: Power-On Default Mode is Mode 0

### **TABLE 8. Output Control (01h)**

This register is used to control the different output configurations.

| Bits          | Field     |                          | Description                                        |

|---------------|-----------|--------------------------|----------------------------------------------------|

| 0             | EP_OUTPUT | This enables the Mono Ea | rpiece output.                                     |

|               |           | EP_OUTPUT                | Status                                             |

|               |           | 0                        | Mono earpice output off                            |

|               |           | 1                        | Mono earpice output on                             |

| 1             | LS_OUTPUT | This enables the Mono Lo | udspeaker output.                                  |

|               |           | LS_OUTPUT                | Status                                             |

|               |           | 0                        | Loudspeaker output off                             |

|               |           | 1                        | Loudspeaker output on                              |

| 2 HP_L_OUTPUT |           | This enables the Headpho | ne left output.                                    |

|               |           | HP_L_OUTPUT              | Status                                             |

|               |           | 0                        | Headphone left output off. If OCL=1, output is in  |

|               |           |                          | mute.                                              |

|               |           | 1                        | Headphone left output on                           |

| 3 HP_R_OUTPUT |           | This enables the Headpho | ne right output.                                   |

|               |           | HP_R_OUTPUT              | Status                                             |

|               |           | 0                        | Headphone right output off. If OCL=1, output is in |

|               |           |                          | mute.                                              |

|               |           | 1                        | Headphone right output on                          |

| Bits | Field              |                                                                                                                                                           | Description                                          |  |

|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| 4    | STEREO_INPUT_ONLY  | This enables the analog left inputs.                                                                                                                      | (AL) and analog right (AR) and disables all other    |  |

|      |                    | STEREO_INPUT_ONLY                                                                                                                                         | Status                                               |  |

|      |                    | 0                                                                                                                                                         | Normal                                               |  |

|      |                    | 1                                                                                                                                                         | Enables AL and AR inputs only                        |  |

| 5    | DAC_INPUT_ONLY     | This enables the DAC left (DL                                                                                                                             | and analog right (DR) and disables all other inputs. |  |

|      |                    | DAC_INPUT_ONLY                                                                                                                                            | Status                                               |  |

|      |                    | 0                                                                                                                                                         | Normal                                               |  |

|      |                    | 1                                                                                                                                                         | Enables DL and DR inputs only                        |  |

| 6    | MONO_ONLY          | This enables mono earpiece (EP) and loudspeaker (LS) outputs MUX and disables the headphone outputs MUX. Enabling this mode can save up to 40 of current. |                                                      |  |

|      |                    | MONO_ONLY                                                                                                                                                 | Status                                               |  |

|      |                    | 0                                                                                                                                                         | Normal                                               |  |

|      |                    | 1                                                                                                                                                         | Enable mono earpiece and loudspeaker outputs MUX     |  |

| 7    | STEREO_OUTPUT_ONLY | This enables the headphone                                                                                                                                | output MUX only and disables all other output        |  |

|      |                    | MUX's. Enabling this mode of                                                                                                                              | can save up to 200µA of current.                     |  |

|      |                    | STEREO_OUTPUT_ONLY                                                                                                                                        | Status                                               |  |

|      |                    | 0                                                                                                                                                         | Normal                                               |  |

|      |                    | 1                                                                                                                                                         | Enables the headphone output MUX                     |  |

# **Volume Control Registers**

# TABLE 9. Volume Control Register EP\_VOL (02h), LS\_VOL (03h), HP\_L\_VOL (05h), HP\_R\_VOL (06h)

These registers are used to control output volume control levels for Earpiece, Loudspeaker and Headphone.

| Bits | Field    | Description                    |                          |  |

|------|----------|--------------------------------|--------------------------|--|

| 4:0  | EP_VOL   | This programs the Earpiece, Lo | oudspeaker and Headphone |  |

|      | LS_VOL   | volume level.                  |                          |  |

|      | HP_L_VOL | VOL                            | Level (dB)               |  |

|      | HP_R_VOL | 00000                          | MUTE                     |  |

|      |          | 00001                          | -56                      |  |

|      |          | 00010                          | <b>-</b> 52              |  |

|      |          | 00011                          | -48                      |  |

|      |          | 00100                          | <b>–45</b>               |  |

|      |          | 00101                          | -42                      |  |

|      |          | 00110                          | -39                      |  |

|      |          | 00111                          | -36                      |  |

|      |          | 01000                          | -33                      |  |

|      |          | 01001                          | -30                      |  |

|      |          | 01010                          | -28                      |  |

|      |          | 01011                          | -26                      |  |

|      |          | 01100                          | -24                      |  |

|      |          | 01101                          | -22                      |  |

|      |          | 01110                          | -20                      |  |

|      |          | 01111                          | -18                      |  |

|      |          | 10000                          | -16                      |  |

|      |          | 10001                          | -14                      |  |

|      |          | 10010                          | -12                      |  |

|      |          | 10011                          | -10                      |  |

|      |          | 10100                          | -8                       |  |

|      |          | 10101                          | -6                       |  |

|      |          | 10110                          | -4                       |  |

|      |          | 10111                          | -3                       |  |

|      |          | 11000                          | -2                       |  |

|      |          | 11001                          | <b>–1</b>                |  |

|      |          | 11010                          | 0                        |  |

|      |          | 11011                          | 1                        |  |

|      |          | 11100                          | 2                        |  |

|      |          | 11101                          | 3                        |  |

|      |          | 11110                          | 4                        |  |

|      |          | 11111                          | 5                        |  |

### TABLE 10. Analog Left and Right Input Control (07h)

This register is used to control input gain for left and right analog inputs.

| Bits           | Field      | Description                               | n          |

|----------------|------------|-------------------------------------------|------------|

| 2:0            | ANA_L_GAIN | This program the analog left input gain.  |            |

|                |            | ANA_L_GAIN                                | Level (dB) |

|                |            | 000                                       | -6         |

|                |            | 001                                       | -3         |

|                |            | 010                                       | 0          |

|                |            | 011                                       | 3          |

|                |            | 100                                       | 6          |

|                |            | 101                                       | 9          |

|                |            | 110                                       | 12         |

|                |            | 111                                       | 15         |

| 5:3 ANA_R_GAIN |            | This program the analog Right input gain. |            |

|                |            | ANA_R_GAIN                                | Level (dB) |

|                |            | 000                                       | -6         |

|                |            | 001                                       | -3         |

|                |            | 010                                       | 0          |

|                |            | 011                                       | 3          |

|                |            | 100                                       | 6          |

|                |            | 101                                       | 9          |

|                |            | 110                                       | 12         |

|                |            | 111                                       | 15         |

### TABLE 11. Mono and DAC Input Gain Control (08h)

This register is sued to control input gain for Mono, DAC left and right inputs.

| Bits | Field        | Descri                    | ption                                 |  |  |

|------|--------------|---------------------------|---------------------------------------|--|--|

| 2:0  | MONO_IN_GAIN | This program the mono inp | ut gain.                              |  |  |

|      |              | MONO_IN_GAIN              | Level (dB)                            |  |  |

|      |              | 000                       | -12                                   |  |  |

|      |              | 001                       | -9                                    |  |  |

|      |              | 010                       | -6                                    |  |  |

|      |              | 011                       | -3                                    |  |  |

|      |              | 100                       | 0                                     |  |  |

|      |              | 101                       | 3                                     |  |  |

|      |              | 110                       | 6                                     |  |  |

|      |              | 111                       | 9                                     |  |  |

| 4:3  | DAC_L_GAIN   | This program the DAC left | This program the DAC left input gain. |  |  |

|      |              | DAC_L_GAIN                | Level (dB)                            |  |  |

|      |              | 00                        | -3                                    |  |  |

|      |              | 01                        | 0                                     |  |  |

|      |              | 10                        | 3                                     |  |  |

|      |              | 11                        | 6                                     |  |  |

| 6:5  | DAC_R_GAIN   | This program the DAC Rigi | nt input gain.                        |  |  |

|      |              | DAC_R_GAIN                | Level (dB)                            |  |  |

|      |              | 00                        | -3                                    |  |  |

|      |              | 01                        | 0                                     |  |  |

|      |              | 10                        | 3                                     |  |  |

|      |              | 11                        | 6                                     |  |  |

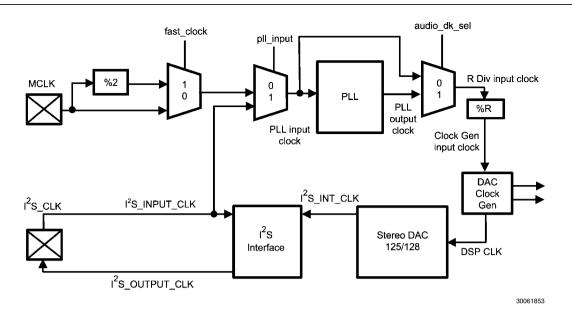

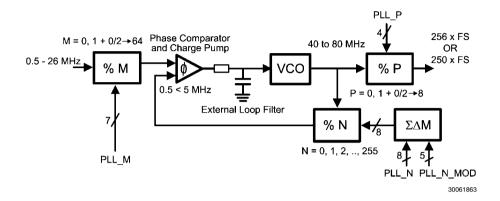

# **Clock Configuration Register**

This register is used to control the multiplexers and clock R divider in the clock module.

TABLE 12. CLOCK (09h)

| Bits            | Register   | Description                                |                              |  |

|-----------------|------------|--------------------------------------------|------------------------------|--|

| 0               | FAST_CLOCK | If set master clock is divided by two.     |                              |  |

|                 |            | FAST_CLOCK                                 | MCLK Frequency               |  |

|                 |            | 0                                          | Normal                       |  |

|                 |            | 1                                          | Divided by 2                 |  |

| 1               | PLL_INPUT  | Programs the PLL input multiplexer to sele | ect:                         |  |

|                 |            | PLL_INPUT                                  | PLL Input Source             |  |

|                 |            | 0                                          | MCLK                         |  |

|                 |            | 1                                          | I <sup>2</sup> S Input Clock |  |

| 2 AUDIO_CLK_SEL |            | Selects which clock is passed to the audio | sub-system                   |  |

|                 |            | DAC_CLK_SEL                                | DAC Sub-system               |  |

|                 |            |                                            | Input Source                 |  |

|                 |            | 0                                          | PLL Input                    |  |

|                 |            | 1                                          | PLL Output                   |  |

| 3               | PLL_ENABLE |                                            |                              |  |

| 7:4             | R_DIV      | Programs the R divider                     |                              |  |

|                 | R_DIV      | Divide Value                               |                              |  |

|                 |            | 0000                                       | 1                            |  |

|                 |            | 0001                                       | 1                            |  |

|                 |            | 0010                                       | 1.5                          |  |

|                 |            | 0011                                       | 2                            |  |

|                 |            | 0100                                       | 2.5                          |  |

|                 |            | 0101                                       | 3                            |  |

|                 |            | 0110                                       | 3.5                          |  |

|                 |            | 0111                                       | 4                            |  |

|                 |            | 1000                                       | 4.5                          |  |

|                 |            | 1001                                       | 5                            |  |

|                 |            | 1010                                       | 5.5                          |  |

|                 |            | 1011                                       | 6                            |  |

|                 |            | 1100                                       | 6.5                          |  |

|                 |            | 1101                                       | 7                            |  |

|                 |            | 1110                                       | 7.5                          |  |

|                 |            | 1111                                       | 8                            |  |

By default the stereo DAC operates at 250\*fs, i.e. 12.000MHz (at the clock generator input clock) for 48kHz data. It is expected that the PLL be used to drive the audio system unless a 12.000MHz master clock is supplied. The PLL can also use the I2S clock input as a source. In this case, the audio DAC uses the clock from the output of the PLL.

### **Common Clock Settings for the DAC**

The DAC can work in 4 modes, each with different oversampling rates, 125,128,64 & 32. In normal operation 125x oversampling provides for the simplest clocking solution as it will work from 12.000MHz (common in most systems with Bluetooth or USB) at 48kHz exactly. The other modes are useful if data is being provided to the DAC from an uncontrollable isochronous source (such as a CD player, DAB, or other external digital source) rather than being decoded from memory. In this case the PLL can be used to derive a clock for the DAC from the I2S clock.

The DAC oversampling rate can be changed to allow simpler clocking strategies, this is controlled in the DAC SETUP register but the oversampling rates are as follows:

TABLE 13.

| DAC MODE | Over sampling Ratio Used |

|----------|--------------------------|

| 00       | 125                      |

| 01       | 128                      |