# 4 A continuous (more than 5 A pulsed) step-down switching regulator with synchronous rectification

Datasheet - production data

#### **Features**

- 4 A output current (more than 5 pulsed)

- Operating input voltage from 2.9 V to 18 V

- External 1.8 V ± 2% reference voltage

- Output voltage from 0.6 to input voltage

- MLCC compatible

- 200 ns T<sub>ON</sub>

- Programmable UVLO matches 3.3 V, 5 V and 12 V bus

- F<sub>SW</sub> programmable up to 1 MHz

- Voltage feed forward

- · Zero load current operation

- Programmable current limit on both switches

- Programmable sink current capability

- Pre-bias start up capability

- Thermal shutdown

## **Applications**

- Consumer: STB, DVD, LCD TV, VCR, car radio, LCD monitors

- Networking: XDSL, modems, routers and switches

- Computer and peripherals: printers, audio / graphic cards, optical storage, hard disk drive

- Industrial: DC-DC modules, factory automation

- HC LED driving

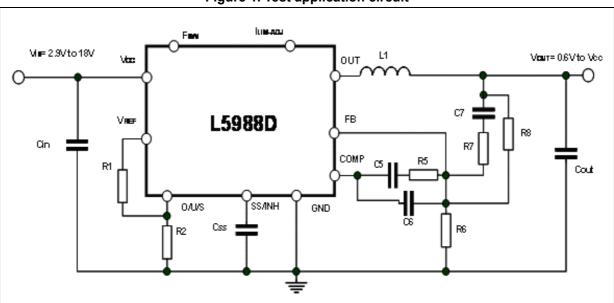

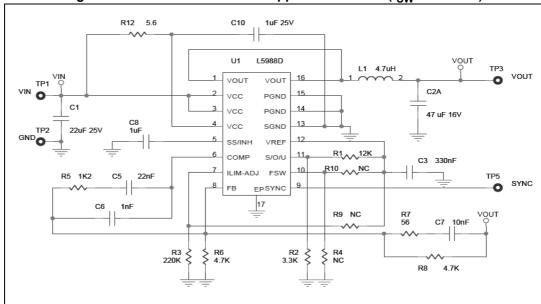

Figure 1. Test application circuit

Contents L5988D

## **Contents**

| 1 | Desc  | cription                                     | 6  |

|---|-------|----------------------------------------------|----|

| 2 | Pin f | unction                                      | 7  |

| 3 | Max   | imum ratings                                 | 8  |

| 4 | Elec  | trical characteristics                       | 9  |

| 5 | Fund  | ctional description                          | 12 |

|   | 5.1   | Multifunction pin                            | 13 |

|   | 5.2   | Oscillator and synchronization               | 15 |

|   | 5.3   | External voltage reference                   | 18 |

|   | 5.4   | Soft-start                                   | 18 |

|   | 5.5   | Monitoring and protections                   | 19 |

|   |       | 5.5.1 Overvoltage                            | 19 |

|   |       | 5.5.2 Current limiting                       | 21 |

|   |       | 5.5.3 UVLO                                   | 23 |

|   |       | 5.5.4 Thermal shutdown                       | 23 |

|   | 5.6   | Minimum on time                              | 23 |

|   | 5.7   | Error amplifier                              | 24 |

| 6 | App   | lication information                         | 25 |

|   | 6.1   | Input capacitor selection                    | 25 |

|   | 6.2   | Inductor selection                           | 26 |

|   | 6.3   | Output capacitor selection                   | 27 |

|   | 6.4   | Compensation network                         | 28 |

|   |       | 6.4.1 Type III compensation network          | 29 |

|   |       | 6.4.2 Type II compensation network           | 33 |

|   | 6.5   | R.M.S. current of the embedded power MOSFETs | 36 |

|   | 6.6   | Thermal considerations                       | 37 |

|   | 6.7   | Layout considerations                        | 41 |

|   | 6.8   | Application circuit                          | 43 |

|   |       |                                              |    |

| L5988D |                              | Contents |

|--------|------------------------------|----------|

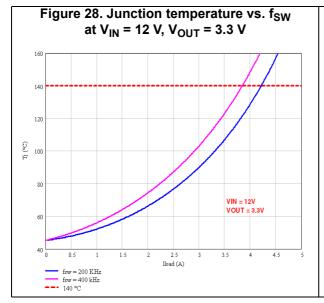

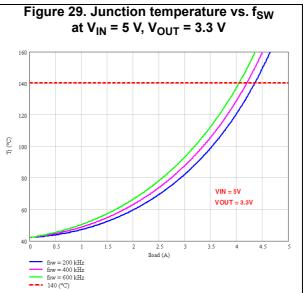

| 7      | Typical characteristics      | 46       |

| 8      | Package information          |          |

|        | HTSSOP16 package information | 49       |

| 9      | Order codes                  | 51       |

| 10     | Revision history             | 51       |

List of tables L5988D

## List of tables

| Table 1.  | Pinout description                                             | 7    |

|-----------|----------------------------------------------------------------|------|

| Table 2.  | Absolute maximum ratings                                       | 8    |

| Table 3.  | Thermal data                                                   | 8    |

| Table 4.  | ESD protection                                                 | 8    |

| Table 5.  | Electrical characteristic                                      | 9    |

| Table 6.  | A/D voltage windows                                            | . 14 |

| Table 7.  | UOS voltage biasing                                            | . 14 |

| Table 8.  | FSW resistor examples                                          | . 16 |

| Table 9.  | ILIM-ADJ resistor examples                                     | . 23 |

| Table 10. | Uncompensated error amplifier                                  | . 24 |

| Table 11. | Input capacitors                                               | . 26 |

| Table 12. | Inductors                                                      | . 27 |

| Table 13. | Output capacitors                                              | . 28 |

| Table 14. | Component list application circuit (f <sub>SW</sub> = 400 kHz) | . 44 |

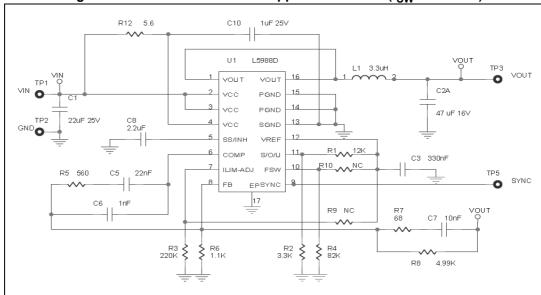

| Table 15. | Component list application circuit (f <sub>SW</sub> = 600 kHz) | . 45 |

| Table 16. | HTSSOP16 package mechanical data                               | . 50 |

| Table 17. | Order codes                                                    | . 51 |

| Table 18  | Document revision history                                      | 51   |

L5988D List of figures

## List of figures

| Figure 1.  | Test application circuit                                                                                                    | 1    |

|------------|-----------------------------------------------------------------------------------------------------------------------------|------|

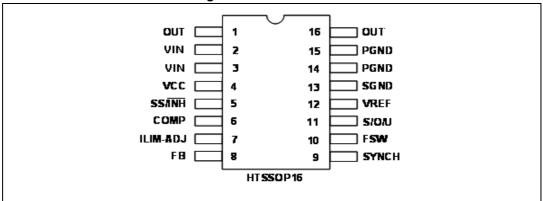

| Figure 2.  | Pin connection                                                                                                              |      |

| Figure 3.  | Voltage mode control loop                                                                                                   | . 12 |

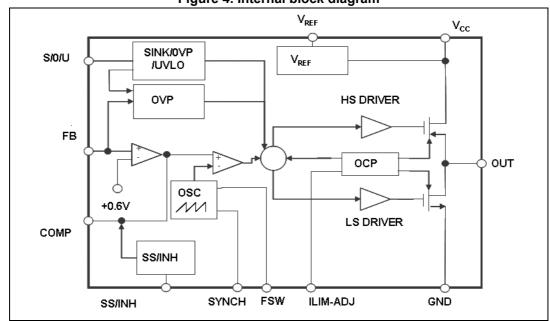

| Figure 4.  | Internal block diagram                                                                                                      | . 12 |

| Figure 5.  | Oscillator circuit block diagram                                                                                            | . 15 |

| Figure 6.  | Sawtooth: voltage feed forward                                                                                              |      |

| Figure 7.  | Sawtooth: synchronization and frequency adjust                                                                              |      |

| Figure 8.  | Input RMS current of two synchronized regulators                                                                            | . 18 |

| Figure 9.  | OVP not latched                                                                                                             |      |

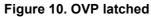

| Figure 10. | OVP latched                                                                                                                 | . 20 |

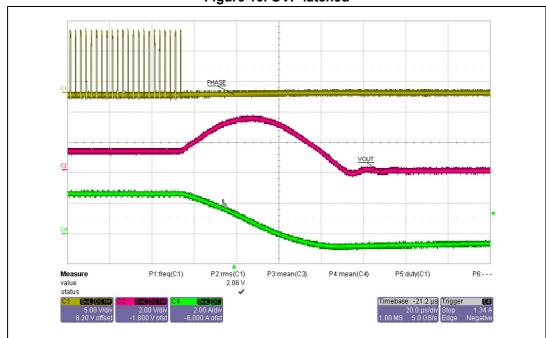

| Figure 11. | Constant current protection at extreme duty cycles                                                                          | . 22 |

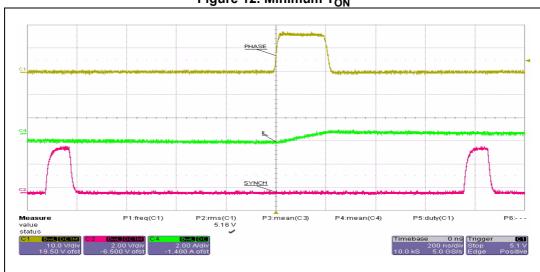

| Figure 12. | Minimum TON                                                                                                                 | . 24 |

| Figure 13. | Type III compensation network                                                                                               | . 30 |

| Figure 14. | Open loop gain: module bode diagram                                                                                         |      |

| Figure 15. | Open loop gain bode diagram with ceramic output capacitor                                                                   |      |

| Figure 16. | Type II compensation network                                                                                                |      |

| Figure 17. | Open loop gain: module bode diagram                                                                                         |      |

| Figure 18. | Open loop gain bode diagram with high ESR output capacitor                                                                  |      |

| Figure 19. | Maximum continuous output current vs. duty cycle                                                                            |      |

| Figure 20. | Switching losses                                                                                                            |      |

| Figure 21. | Estimation of the internal power losses ( $V_{IN}$ = 12 V, $V_{OUT}$ = 1.2 V, $f_{SW}$ = 400 kHz)                           |      |

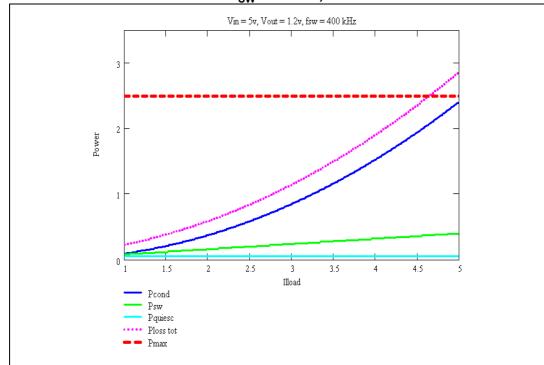

| Figure 22. | Estimation of the internal power losses ( $V_{IN} = 5 \text{ V}$ , $V_{OUT} = 1.2 \text{ V}$ , $f_{SW} = 400 \text{ kHz}$ ) |      |

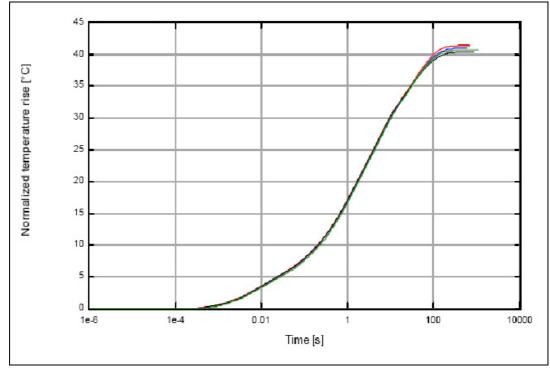

| Figure 23. | Measurement of the thermal impedance of the evaluation board                                                                |      |

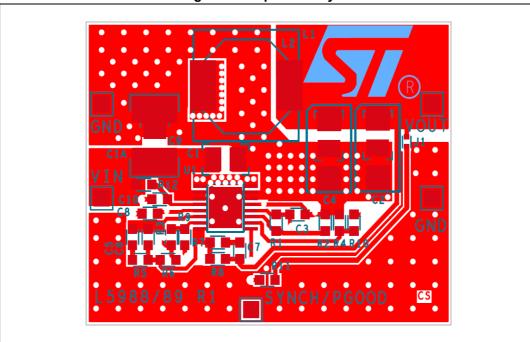

| Figure 24. | Top board layout                                                                                                            |      |

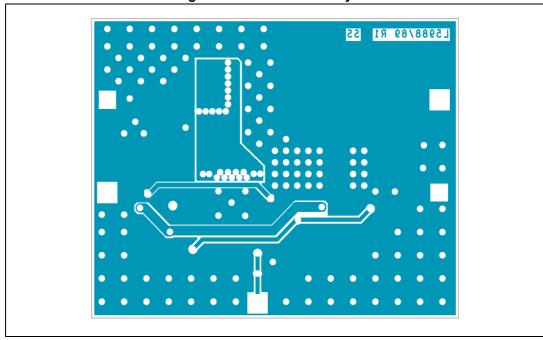

| Figure 25. | Bottom board layout                                                                                                         |      |

| Figure 26. | Demonstration board application circuit (f <sub>SW</sub> = 400 kHz)                                                         |      |

| Figure 27. | Demonstration board application circuit (f <sub>SW</sub> = 600 kHz)                                                         |      |

| Figure 28. | Junction temperature vs. f <sub>SW</sub> at V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 3.3 V                                | . 46 |

| Figure 29. | Junction temperature vs. f <sub>SW</sub> at V <sub>IN</sub> = 5 V, V <sub>OUT</sub> = 3.3 V                                 | . 46 |

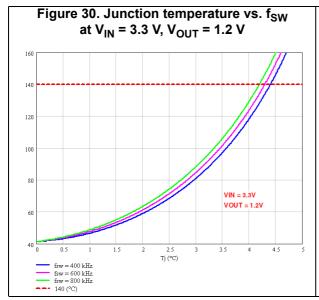

| Figure 30. | Junction temperature vs. f <sub>SW</sub> at V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 1.2 V                               |      |

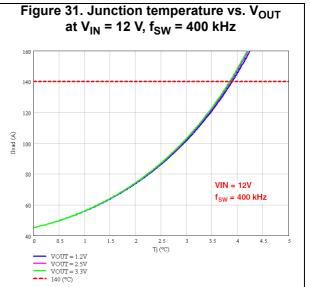

| Figure 31. | Junction temperature vs. V <sub>OUT</sub> at V <sub>IN</sub> = 12 V, f <sub>SW</sub> = 400 kHz                              |      |

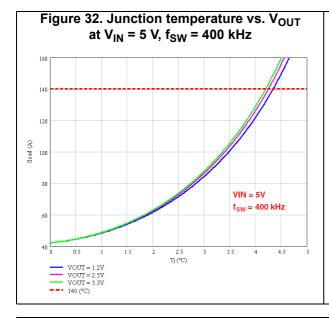

| Figure 32. | Junction temperature vs. V <sub>OUT</sub> at V <sub>IN</sub> = 5 V, f <sub>SW</sub> = 400 kHz                               |      |

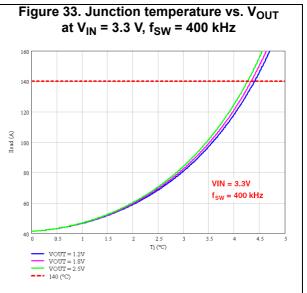

| Figure 33. | Junction temperature vs. $V_{OUT}$ at $V_{IN}$ = 3.3 V, $f_{SW}$ = 400 kHz                                                  |      |

| Figure 34. | Efficiency vs. output current at V <sub>IN</sub> = 3.3 V, f <sub>SW</sub> = 400 kHz                                         |      |

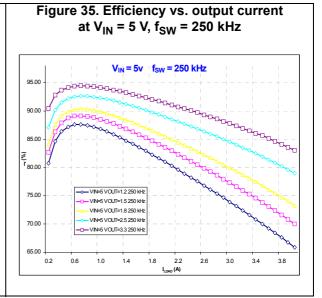

| Figure 35. | Efficiency vs. output current at V <sub>IN</sub> = 5 V, f <sub>SW</sub> = 250 kHz                                           |      |

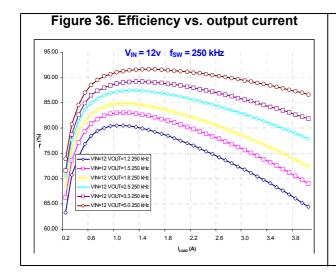

| Figure 36. | Efficiency vs. output current                                                                                               |      |

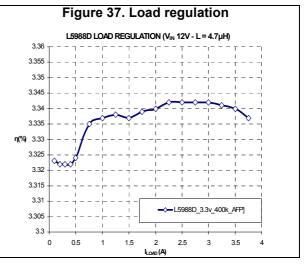

| Figure 37. | Load regulation                                                                                                             |      |

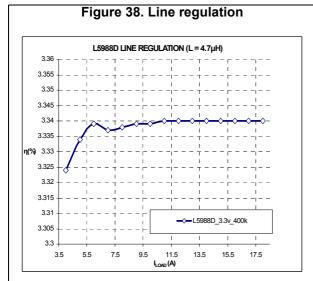

| Figure 38. | Line regulation                                                                                                             |      |

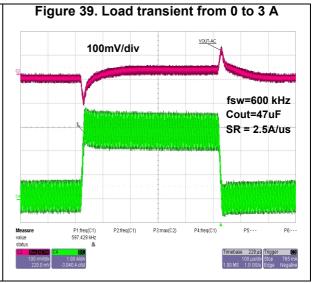

| Figure 39. | Load transient from 0 to 3 A                                                                                                |      |

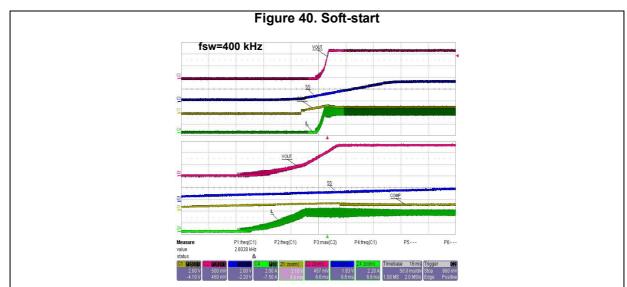

| Figure 40. | Soft-start                                                                                                                  |      |

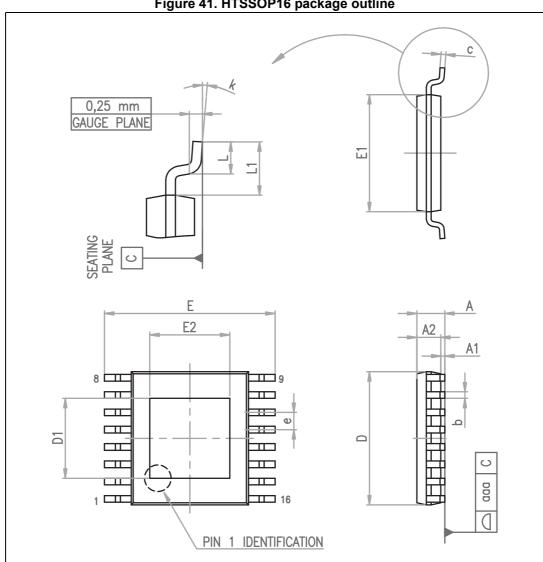

| Figure 41. | HTSSOP16 package outline                                                                                                    | . 49 |

Description L5988D

## 1 Description

The L5988D is a monolithic step down power switching regulator able to deliver a continuous output current of 4 A to the load in most of the application conditions limited only by the thermal performance. The device is able to deliver more than 5 A to the load for a maximum time which is dependent on the thermal impedance of the system and the specific operating conditions).

The input voltage can range from 2.9 V to 18 V. The device is capable of 100% duty cycle operation thanks to the embedded high side PMOS switch which doesn't need external bootstrap capacitor to be driven.

The internal switching frequency is adjustable by external resistor and can be set continuously from 100 kHz to 1 MHz. The L5988D can also be synchronized to an external frequency signal driven to the SYNCH pin I/O pin.

The multifunction UOS pin allows to set-up properly the additional embedded features depending on the value of the voltage level.

- U (UVLO): two UVLO thresholds can be selected to match the 3.3 V and 5 V or 12 V input buses

- O (OVP): latched or not latched OVP protection selectable. In latched mode the switching activity is interrupted until an UVLO or INH event happens

- S (SINK): the sink capability is always disabled during soft-start time to support prebiased output voltage. Afterwards the sink capability can be enabled or not depending on the voltage set on the multifunction pin.

During soft-start phase a constant current protection is active to deliver extra current necessary to load the output capacitor. The current limit protection is achieved by sensing the current flowing in both embedded switches to assure an effective protection even at extreme duty cycle operations. Finished the soft-start phase the current protection feature triggers the "HICCUP" mode forcing the soft-start capacitor to be discharged and recharged. The current thresholds of both switches can be adjusted in tracking by using an external resistor to dimension the current protection accordingly to the local application.

The soft-start time is based on a constant current charge of an external capacitor. As a consequence the time can be set accordingly to the value of the output capacitor.

The latest smart power technology BCD6 (Bipolar-CMOS-DMOS version 6) features a low resistance of the embedded switches (35 m $\Omega$  typical for a NMOS, 50 m $\Omega$  typical for a PMOS), achieving high efficiency levels.

The HTSSOP16 package with exposed pad accomplishes low  $R_{thJA}$  (40 °C/W), useful in dissipating power internally generated during high output current / high frequency operations.

L5988D Pin function

## 2 Pin function

Figure 2. Pin connection

Table 1. Pinout description

| No.    | Name     | Description                                                                                                                                                                                                                                             |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 16  | OUT      | Regulator output                                                                                                                                                                                                                                        |

| 2, 3   | VIN      | Unregulated DC input voltage                                                                                                                                                                                                                            |

| 4      | VCC      | Unregulated DC signal input voltage                                                                                                                                                                                                                     |

| 5      | SS/INH   | An external logic signal (active LOW) disables the device. In case the pin is floating the device deliver a constant current (22 $\mu$ A typ.) to charge the soft-start capacitor (see Section 5.4 on page 18)                                          |

| 6      | COMP     | Error amplifier output for frequency compensation                                                                                                                                                                                                       |

| 7      | ILIM-ADJ | Connecting a pull-up resistor to VREF or a pull-down resistor to GND the internal current limit thresholds can be tuned to match the local application. In case the pin is left floating no changes are applied to the default current limit thresholds |

| 8      | FB       | Feedback input. Connecting the output voltage directly to this pin results in a regulation voltage of 600 mV. An external resistive divider is required for higher output voltages                                                                      |

| 9      | SYNCH    | Master/slave synchronization                                                                                                                                                                                                                            |

| 10     | FSW      | Connecting a pull-up resistor to VREF or a pull-down resistor to GND the internal oscillator frequency will be increased or decreased respectively. In case the pin is left floating the predefined oscillator frequency (400 kHz ± 10%) is active      |

| 11     | U/O/S    | Multifunction pin used to program additional features: UVLO thresholds, OVP latched/not latched, SINK enabled/disabled                                                                                                                                  |

| 12     | VREF     | 1.8 V voltage reference                                                                                                                                                                                                                                 |

| 13     | SGND     | Signal ground                                                                                                                                                                                                                                           |

| 14, 15 | PGND     | Power ground                                                                                                                                                                                                                                            |

Maximum ratings L5988D

## 3 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                          | Parameter                                   | Value                      | Unit |

|-------------------------------------------------|---------------------------------------------|----------------------------|------|

| VCC                                             | Input voltage                               | 20                         | V    |

| VOUT                                            | Output DC voltage                           | -0.3 <sup>(1)</sup> to VCC | V    |

| U/O/S, SS/INH,<br>COMP, SYNCH,<br>Fsw, ILIM-ADJ | Analog pins                                 | -0.3 to 4                  | V    |

| FB                                              | Feedback voltage                            | 1.5                        | V    |

| P <sub>tot</sub>                                | Power dissipation at T <sub>A</sub> < 60 °C | 2.25                       | W    |

| T <sub>J</sub>                                  | Junction temperature range                  | -40 to 150                 | °C   |

| T <sub>STG</sub>                                | Storage temperature range                   | -55 to 150                 | °C   |

During the switching activity the negative peak voltage could reach -1.5 V without any damage for the device.

Table 3. Thermal data

| Symbol            | Parameter                                   | Value             | Unit |

|-------------------|---------------------------------------------|-------------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient max. | 40 <sup>(1)</sup> | °C/W |

<sup>1.</sup> HTSSOP16 package mounted on ST demonstration board.

Table 4. ESD protection

| Symbol | bol Test condition |     | Unit |

|--------|--------------------|-----|------|

| ESD    | НВМ                | 1   | kV   |

| ESD    | CDM                | 250 | V    |

## 4 Electrical characteristics

$V_{CC}$  = 12 V,  $T_{J}$  = 25 °C unless otherwise specified.

**Table 5. Electrical characteristic**

| Symbol                                  | Parameter                                 | Test condition                        |     | Min.  | Тур. | Max.  | Unit |

|-----------------------------------------|-------------------------------------------|---------------------------------------|-----|-------|------|-------|------|

| $V_{CC}$                                | Operating input voltage range             | Vout = 0.6 V; lout = 3 A              |     | 2.9   |      | 18    | V    |

| D LIC                                   | High side MOOFFT are resistance           | lout = 1.0 A                          |     | 75    | 85   | 95    | mΩ   |

| R <sub>DS(on)</sub> HS                  | High side MOSFET on resistance            | 10ut - 1.0 A                          | (1) | 111   | 120  | 132   | mΩ   |

| D 10                                    | Law side MOSEET on registance             | lout = 1.0 A                          |     | 62    | 67   | 72    | mΩ   |

| R <sub>DS(on)</sub> LS                  | Low side MOSFET on resistance             | lout = 1.0 A                          | (1) | 92    | 100  | 106   | mΩ   |

| I <sub>L HIGH SIDE</sub>                | Maximum peak limiting current             | I <sub>LIM-ADJ</sub> = float          |     | 3.6   | 4    | 4.4   | Α    |

| I <sub>L LOW SIDE</sub>                 | Maximum valley limiting current           | I <sub>LIM-ADJ</sub> = float          |     | 4.14  | 4.6  | 5.06  | Α    |

| f <sub>SW</sub>                         | Switching frequency                       | FSW = floating                        |     | 360   | 400  | 440   | kHz  |

| f <sub>SW ADJ</sub>                     | adjusted switching frequency              | R <sub>FSW PULL DWN</sub> = 27 kΩ     |     |       | 1000 |       | kHz  |

| D                                       | Duty cycle                                |                                       |     | 0     |      | 100   | %    |

| Selectable u                            | nder voltage lockout (UVLO)               |                                       | •   |       |      |       |      |

|                                         | Turn ON Vcc threshold                     |                                       |     |       | 2.7  | 2.8   | V    |

| 3.3 V BUS                               | Turn OFF Vcc threshold                    |                                       |     | 2.4   | 2.5  |       | V    |

|                                         | Hysteresis                                |                                       |     |       | 200  |       | mV   |

|                                         | Turn ON Vcc threshold                     |                                       |     |       | 8    | 8.6   | V    |

| 12 V BUS                                | Turn OFF Vcc threshold                    |                                       |     | 6.8   | 7    |       | V    |

|                                         | Hysteresis                                |                                       |     |       | 1    |       | V    |

| DC characte                             | ristic                                    |                                       |     |       |      |       |      |

|                                         | Coft start ourrant                        | V <sub>SS/INH</sub> = 2 V             |     |       | 22   |       | μА   |

| I <sub>SS</sub>                         | Soft-start current                        | V <sub>SS/INH</sub> = 0               |     |       | 5    |       | μΑ   |

| INILI                                   | Device ON level                           |                                       |     | 0.8   |      |       | V    |

| INH                                     | Device OFF level                          |                                       |     |       |      | 0.3   | V    |

| Iq                                      | Quiescent current                         | Duty cycle = 0; V <sub>FB</sub> = 1 V |     |       |      | 3     | mA   |

| I <sub>q st-by</sub>                    | Total stand-by quiescent current          |                                       |     |       |      | 35    | μΑ   |

| Dynamic cha                             | aracteristic (see <i>Figure 1 on page</i> | 2 1)                                  | •   |       |      |       |      |

| \/ED                                    | Veltere for all and in an end of an       | 0.07/ 47/00 4407/                     |     | 0.595 | 0.6  | 0.605 |      |

| VFB                                     | Voltage feedback in regulation            | 2.9 V < VCC < 18 V                    | (1) | 0.592 | 0.6  | 0.609 | V    |

| Error amplifi                           | ier                                       | 1                                     |     | 1     |      | I     |      |

| V <sub>OH</sub>                         | High level output voltage                 | V <sub>FB</sub> = 0.2 V; SS floating  |     | 3.1   |      |       | V    |

| • • • • • • • • • • • • • • • • • • • • |                                           | 1 -                                   |     |       |      |       |      |

Electrical characteristics L5988D

Table 5. Electrical characteristic (continued)

| Symbol                  | Parameter                                                                | Test condition                                     |     | Min.  | Тур. | Max.  | Unit            |

|-------------------------|--------------------------------------------------------------------------|----------------------------------------------------|-----|-------|------|-------|-----------------|

| I <sub>O SOURCE</sub>   | Source output current                                                    | V <sub>FB</sub> = 0.2 V                            | (2) |       | 25   |       | mA              |

| I <sub>O SRCE LIM</sub> | Source current limitation                                                | V <sub>FB</sub> = 0.2 V, V <sub>COMP</sub> = 3 V   |     |       | 2    |       | mA              |

| I <sub>O SINK</sub>     | Sink output current                                                      | V <sub>FB</sub> = 1.0 V, V <sub>COMP</sub> = 0.5 V |     |       | 30   |       | mA              |

| A <sub>V0</sub>         | DC open loop gain                                                        |                                                    | (2) |       | 100  |       | dB              |

| Sync function           | on                                                                       | •                                                  |     |       |      |       |                 |

|                         | High input voltage                                                       |                                                    |     | 2.9   |      | 4.0   | V               |

|                         | Low input voltage                                                        |                                                    |     |       |      | 0.74  | V               |

|                         | Slave sink current                                                       | V <sub>SYNC</sub> = 3.3 V; FSW = float             |     |       | 1    |       | mA              |

|                         | Master output amplitude                                                  | I <sub>SOURCE</sub> = 5 mA                         |     | 2.9   |      |       | V               |

|                         | Output pulse width                                                       | SYNCH = floating                                   |     |       | 100  |       | ns              |

|                         | Input pulse width                                                        |                                                    |     | 70    |      |       | ns              |

| Reference s             | ection                                                                   |                                                    |     |       |      |       |                 |

|                         |                                                                          |                                                    |     | 1.756 | 1.8  | 1.837 | V               |

| $V_{REF}$               | Reference voltage                                                        | Vcc = 2.9 V to 18 V                                | (1) | 1.754 | 1.8  | 1.852 | V               |

|                         | Line regulation                                                          | Vcc = 2.9 V to 18 V                                |     | 101   | 6    | 12    | mV              |

|                         | Line regulation                                                          | I <sub>REF</sub> = 0 mA                            |     |       |      | 12    | 111 V           |

|                         | Load regulation                                                          | I <sub>REF</sub> = 0 to 5 mA                       |     |       | 7.5  | 15    | mV              |

|                         | Short circuit current                                                    |                                                    |     | 12    | 18   | 24    | mA              |

| Protections             |                                                                          |                                                    |     |       |      |       |                 |

| V <sub>FB_OVP</sub>     | Overvoltage trip                                                         | V <sub>FB</sub> rising                             |     | 15    | 20   | 24    | %               |

| *FB_OVP                 | (V <sub>FB_OVP</sub> - V <sub>FB</sub> ) / V <sub>FB</sub>               | VFB (15)(19)                                       |     | 10    |      | Z-T   | V <sub>FB</sub> |

| Bus thresho             | olds                                                                     |                                                    |     |       |      |       |                 |

| TH1                     | <ul><li>UVLO 3.3 V bus</li><li>OVP not latched</li><li>No sink</li></ul> |                                                    | (3) | 0     |      | 0.2   | ٧               |

| TH2                     | <ul><li>UVLO 3.3 V bus</li><li>OVP not latched</li><li>Sink</li></ul>    |                                                    | (3) | 0.26  |      | 0.425 | ٧               |

| TH3                     | <ul><li>UVLO 3.3 V bus</li><li>OVP latched</li><li>No sink</li></ul>     |                                                    | (3) | 0.48  |      | 0.65  | ٧               |

| TH4                     | <ul><li>UVLO 3.3 V bus</li><li>OVP latched</li><li>Sink</li></ul>        |                                                    | (3) | 0.71  |      | 0.875 | ٧               |

| TH5                     | <ul><li>UVLO 12 V bus</li><li>OVP not latched</li><li>No sink</li></ul>  |                                                    | (3) | 0.93  |      | 1.085 | V               |

Table 5. Electrical characteristic (continued)

| Symbol | Parameter                                                            | Test condition |     | Min.  | Тур. | Max.  | Unit |

|--------|----------------------------------------------------------------------|----------------|-----|-------|------|-------|------|

| TH6    | <ul><li>UVLO 12 V bus</li><li>OVP not latched</li><li>Sink</li></ul> |                | (3) | 1.16  |      | 1.31  | V    |

| TH7    | <ul><li>UVLO 12 V bus</li><li>OVP latched</li><li>No sink</li></ul>  |                | (3) | 1.385 |      | 1.525 | V    |

| TH8    | <ul><li>UVLO 12 V bus</li><li>OVP latched</li><li>Sink</li></ul>     |                | (3) | 1.615 |      | VREF  | V    |

Specification over the junction temperature range (T<sub>J</sub>) of -40 to +125 °C are guaranteed by design, characterization and statistical correlation.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup>  $V_{CC} = 4 V$ .

## 5 Functional description

The L5988D is based on a voltage mode control loop. Therefore the duty ratio of the internal switch is obtained through a comparison between a saw-tooth waveform (generated by an oscillator) and the output voltage of the error amplifier as shown in *Figure 3*. The advantage of this technique is the very short conduction time of the power elements thanks to the proper operation of the control loop without a precise current sense, which instead is required in current mode regulators. Thanks to this architecture the L5988D supports extremely low conversion ratio (D =  $V_{OUT}/V_{IN}$ ) even at very high switching frequency (up to 1 MHz).

V<sub>REF</sub> VOILATOR RAMP

PWM

PWM

V<sub>RAMP</sub>

V<sub>OUT\_EA</sub>

TO DRIVERS

TO DRIVERS

Figure 3. Voltage mode control loop

The main internal blocks are represented in Figure 4.

Figure 4. Internal block diagram

Below follows a brief description of the main blocks:

- A voltage pre-regulator supplies the internal circuitry. The external 1.8 V voltage reference is supplied by this regulator.

- A voltage monitor circuit that checks the input and internal voltages

- A fully integrated sawtooth oscillator whose frequency is 400 kHz ± 10% when the Fsw pin is floating. Its frequency can be increased/decreased connecting a proper resistor to GND or VREF

- The internal current limitation circuitry monitors the current flowing in both embedded switches to guarantee an effective protection even in extreme duty cycle conditions

- The over voltage protection (OVP) monitors the feedback voltage. If the voltage of this

pin overcomes the 20% of the internal reference value (600 mV ± 1%) it will force the

conduction of the low side switch until the overshoot is present

- A voltage mode amplifier. The inverting input and the output are externally available for compensation

- A pulse width modulator (PWM) comparator and the relative logic to drive the embedded switches

- The soft-start circuit charges an external capacitor with a constant current equal to 20  $\mu$ A (typ.). The soft-start feature is realized clamping the output of the error amplifier until the voltage across the capacitor is below 2.7 V

- The circuitry acting on the SYNCH pin provides external signal reference to slave devices when the regulator works as a master or accept the synchronization from an external reference source

- The circuitry related to the UOS multifunction pin is composed of a 3 bit A/D converter and the decoding logic. It recognizes eight different voltage windows of a VREF voltage magnitude for selecting additional features.

- An inhibit block for stand-by operation

- A circuit to realize the thermal protection function

## 5.1 Multifunction pin

The UOS pin is used to configure the device additional features accordingly to the voltage bias imposed through VREF voltage partitioning.

The selectable options are:

- UVLO level: two pre-defined the under voltage lock out thresholds can be selected to match the 3.3 V and 5 V or 12 V power bus

- SINK capability: this feature is always disabled during the soft-start period to be compatible with pre-biased output voltages. After the soft-start phase, the synchronous rectification can be enabled or not depending on the status of the UOS pin. Anyway, in case an overvoltage is detected, the sink capability is always enabled to bring the FB back to regulation as fast as possible

- OVP management: in case the latched mode is selected and an overvoltage event recurs, the switching activity will be suspended until VCC is reapplied or the SS/INH pin is toggled. Otherwise when the overvoltage transient is ended the regulator will work accordingly to the load request without regulation discontinuity

The circuitry related to the UOS multifunction pin is composed of a 3 bit A/D converter and the decoding logic. *Table 6* shows the internal thresholds of each voltage window composing the VREF magnitude. The voltage biasing of the multifunction can be set accordingly to table *Table 7*.

Table 6. A/D voltage windows

|         | UVLO      | OVP      | SINK    |

|---------|-----------|----------|---------|

| 4.0.1/  |           |          |         |

| 1.8 V   | 12 V BUS  | LATCH    | SINK    |

| 1.575 V | 12 V BUS  | LATCH    | NO SINK |

| 1.35 V  | 12 V BUS  | NO LATCH | SINK    |

| 1.125 V | 12 V BUS  | NO LATCH | NO SINK |

| 0.9 V   | 3.3 V BUS | LATCH    | SINK    |

| 0.675 V | 3.3 V BUS | LATCH    | NO SINK |

| 0.45 V  | 3.3 V BUS | NO LATCH | SINK    |

| 0.225 V | 3.3 V BUS | NO LATCH | NO SINK |

| 0 V     |           |          |         |

Table 7. UOS voltage biasing

| <b>R1</b> ( <b>k</b> Ω) | <b>R2</b> ( <b>k</b> Ω) | V <sub>OUS</sub> (V) | UVLO      | OVP      | SINK    |

|-------------------------|-------------------------|----------------------|-----------|----------|---------|

| 0                       | N.C.                    | 1.8                  | 12 V BUS  | LATCH    | SINK    |

| 0.68                    | 2.7                     | 1.438                | 12 V BUS  | LATCH    | NO SINK |

| 1.2                     | 2.7                     | 1.246                | 12 V BUS  | NO LATCH | SINK    |

| 2                       | 2.7                     | 1.034                | 12 V BUS  | NO LATCH | NO SINK |

| 3.3                     | 2.7                     | 0.810                | 3.3 V BUS | LATCH    | SINK    |

| 6.2                     | 2.7                     | 0.546                | 3.3 V BUS | LATCH    | NO SINK |

| 11                      | 2.7                     | 0.355                | 3.3 V BUS | NO LATCH | SINK    |

| N.C.                    | 0                       | 0                    | 3.3 V BUS | NO LATCH | NO SINK |

## 5.2 Oscillator and synchronization

The generation of the internal saw-tooth waveform is based on the constant current charge / discharge of an internal capacitor. The current generator is designed to get a switching frequency of  $400 \text{ kHz} \pm 10\%$  in case the FSW pin is left floating.

The current mirror connected to FSW (see *Figure 5*) pin acts increasing / decreasing the value of the internal charging current to adjust the oscillator frequency. Since the internal circuitry forces the FSW voltage bias at 1.235 V, the user can easily source / sink current in this pin connecting a pull up resistor to VREF or a pull down to GND respectively.

Clock

Generator

Ramp

Generator

Ramp

Generator

Figure 5. Oscillator circuit block diagram

The value of the pull up resistor versus VREF to decrease the oscillator frequency follows the formula:

#### **Equation 1**

$$R_1(K\Omega) = \frac{8.5 \cdot 10^3}{400 - F_{SW}(KHz)} + 0.95$$

In the same way to increase the switching frequency the pull down resistor is selected using the formula:

#### **Equation 2**

$$R_2(K\Omega) = \frac{18 \cdot 10^3}{F_{SW}(KHz) - 400} - 2.1$$

Table 11 on page 26 shows some resistor values to adjust the oscillator frequency.

| Table 6. F3VV Tesistor examples |                       |                         |                       |  |  |

|---------------------------------|-----------------------|-------------------------|-----------------------|--|--|

| <b>R1</b> ( <b>k</b> Ω)         | f <sub>SW</sub> (kHz) | <b>R2</b> ( <b>k</b> Ω) | f <sub>SW</sub> (kHz) |  |  |

| 43                              | 198                   | 360                     | 450                   |  |  |

| 47                              | 215                   | 180                     | 499                   |  |  |

| 56                              | 245                   | 120                     | 548                   |  |  |

| 62                              | 261                   | 91                      | 594                   |  |  |

| 82                              | 295                   | 56                      | 711                   |  |  |

| 110                             | 322                   | 43                      | 801                   |  |  |

| 150                             | 343                   | 33                      | 915                   |  |  |

| 220                             | 361                   | 27                      | 1022                  |  |  |

Table 8. FSW resistor examples

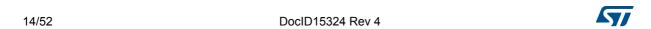

To improve the line transient performance, the voltage feed forward is implemented by changing the slope of the sawtooth according to the input voltage change (see *Figure 6* a).

Figure 6. Sawtooth: voltage feed forward

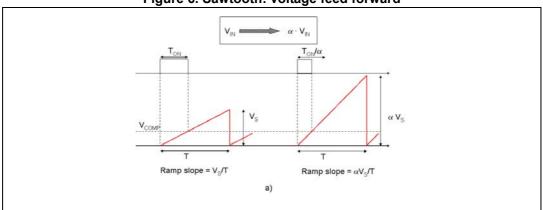

The slope of the sawtooth does not change if the oscillator frequency is increased by an external signal or adjusted by the external resistor (see *Figure 7*). As a consequence the gain of the PWM stage is a function of the switching frequency and its contribution must be taken in account when performing the calculations of the compensation network (see *Section 6.4.1 on page 29* and *Section 6.4.2 on page 33*).

Figure 7. Sawtooth: synchronization and frequency adjust

4

Beating frequency noise is an issue when more than one voltage rail is on the same board. A simple way to avoid this problem is to operate all the regulators at the same switching frequency. The synchronization feature of a set of L5988D is simply get connecting together their SYNCH pin. The device with highest switching frequency will be the MASTER and provides the synchronization signal to the others. Therefore the SYNCH is a I/O pin to deliver or recognize a frequency signal.

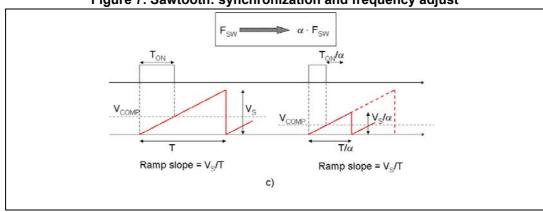

In order to minimize the RMS current flowing through the input filter, the L5988D provides a phase shift of 180° between the master and the SLAVES. In cases where more than two devices are synchronized, all slaves will have a common 180° phase shift with respect to the master.

In case the synchronized set shares a switching frequency different to the nominal 400 kHz, it is suggested to provide the proper FSW resistor to each device. In this way all the devices will have a common peak amplitude of the internal sawtooth signal so the same oscillator gain in the open loop gain transfer function. In this way the same compensation network is valid for all the devices.

Taking in account the case of two synchronized L5988D regulating the same output voltage, the RMS current in the input filter will be optimized and will observe the following formula:

#### **Equation 3**

$$I_{RMS} = \begin{cases} \frac{I_{OUT}}{2} \cdot \sqrt{2D \cdot (1 - 2D)} & \text{if } D < 0.5 \\ \frac{I_{OUT}}{2} \cdot \sqrt{(2D - 1) \cdot (2 - 2D)} & \text{if } D > 0.5 \end{cases}$$

Multiple regulators can be also synchronized to an external frequency signal fed to the SYNCH pin. In this case the set is phased to the reference and all the devices will work with 0° phase shift.

The graphical representation of the input RMS current of the input filter in the case of two devices with 0° phase shift (synchronized to an external signal) or 180° phase shift (synchronized connecting their SYNCH pins) regulating the same output voltage is provided in *Figure 8*. To dimension the proper input capacitor please refer to *Section 6.1 on page 25*.

Figure 8. Input RMS current of two synchronized regulators

### 5.3 External voltage reference

An external 1.8 V regulated voltage is provided. This reference is useful to set the voltage at the multifunction pin (see Section 5.1 on page 13) or to source current to ILIM-ADJ and FSW pins (see Section 5.2 and Section 5.5.2). The typical current capability is 4 mA.

#### 5.4 Soft-start

When VCC is above the selected UVLO threshold the start-up phase takes place. At start-up, a voltage ramp is generated charging the external capacitor  $C_{SS}$  with an internal current generator. The device is in inhibit mode as long as  $SS/\overline{INH}$  pin is below the INH threshold.

The L5988D implements the soft-start phase by clamping the output of the error amplifier and, being based on a voltage mode control, the duty cycle. In fact the comparison between the output of the error amplifier and the internal saw tooth waveform generates the duty cycle needed to keep the output voltage in regulation.

Two different current sources charge the external capacitor depending on the pin voltage in order to reduce the power consumption in INH mode.

#### **Equation 4**

$$I_{SS} = \begin{cases} I_{SS1} = 5 \mu A & 0 < V_{SS/INH} < 1 \\ I_{SS2} = 22 \mu A & 1 < V_{SS/INH} < 2.9 \end{cases}$$

The equation for the soft-start time is:

#### **Equation 5**

$$T_{SS} = \Delta T_1 + \Delta T_2 = \frac{C_{SS}}{I_{SS1}} \times (1 - 0) + \frac{C_{SS}}{I_{SS2}} \times (2.9 - 1)$$

Considering  $I_{SS2}/I_{SS1} = 22/5 = 4.4$ , the proper soft-start capacitor is simply calculated as follows:

#### **Equation 6**

$$C(nF) = Tss(mS) \times 3.5$$

During the soft-start phase ( $V_{SS}$  < 2.9 V):

- the sink capability is always disabled (independently from the multifunction pin settings) to be compatible with pre-biased output voltage

- in case the overcurrent limit is detected, a constant current protection is provided in order to deliver extra current for charging the output capacitor (see Section 5.5.2 for description of current protection management).

During normal operation the  $C_{SS}$  is discharged with a constant current of 22  $\mu$ A (typ.) only if:

- HICCUP mode is triggered (see Section 5.5.2)

- the input voltage goes below the UVLO threshold (see Section 5.5.3)

- the internal temperature is over 150°C (see Section 5.5.4)

A new SS cycle will start when the V<sub>SS</sub> drops below the INH threshold.

New high performance ICs often require more than one supply voltage. Most of these applications require well defined start-up sequencing, in order to avoid potential damage and latch-up of the processing core. Sharing the same soft-start capacitor for a set of regulators, the output voltages increase with the same slew rate implementing a "simultaneous start-up" sequencing method.

## 5.5 Monitoring and protections

#### 5.5.1 Overvoltage

The device provides the overvoltage protection monitoring the output voltage through the FB pin. If the voltage sensed on FB pin reaches a value 20% (typ.) greater than the reference of the error amplifier, the low-side MOSFET is turned on to discharge as fast as possible the output capacitor. It is possible to set two different behaviors in case of OVP:

- In case the OVP latched mode is active (see <u>Section 5.1 on page 13</u>), the internal

oscillator is suspended and the low side switch will be kept on until the input voltage

goes below the selected UVLO threshold or the <u>SS/INH</u> pin is forced below the INH

threshold.

- In case of NOT latched OVP mode is active, the low side MOS is forced ON until the feedback voltage is higher than the OVP threshold (20% greater than the reference of the error amplifier).

Measure P1:freq(C1) P2:ms(C1) P3:mean(C3) P4:mean(C4) P5:duty(C1) P6--value status

C1 Evalue 1 3.41 V

Status C2 Evalue 1 3.41 V

Status C3 Evalue 1 3.41 V

Status C4 Evalue 1 3.41 V

Status C4 Evalue 1 3.41 V

Status C5 Evalue 1 3.41 V

Status C6 Evalue 1 3.44 Evalue 1 3.41 V

Status C7 Evalue 1 3.44 Evalue 1 3.

Figure 9. OVP not latched

#### 5.5.2 Current limiting

The current limiting feature acts in different ways depending on the operative conditions.

- In case an overcurrent detection happens after the soft-start phase, the internal logic will trigger the "HICCUP" mode. Both switches are turned off and the soft-start capacitor is discharged with a constant current of 22 μA (typ.). When the SS/INH voltage drops below the INH threshold a new SS cycle will start.

- During the soft-start phase the overcurrent information is used to provide a constant current protection. In this way additional current is available to charge the output capacitor during power up.

The most common way is to sense the current flowing through the power MOSFETs. However, due to the noise created by the switching activity of the power MOSFETs, the current sense is disabled during the initial phase of the conduction time. This avoids an erroneous detection of a fault condition. This interval is generally known as "masking time" or "blanking time". For this reason, the current cannot be sensed through the high-side MOSFET in the case of extremely low duty cycles, nor through the low-side MOSFET in the case of very high duty cycles.

The L5988D assures the effective protection sensing the current flowing in both embedded switches. The protection achieved by sensing the current in the high-side MOSFET is called "peak overcurrent protection", while the protection achieved by sensing the current in the low-side MOSFET is called "valley overcurrent protection". When the current limit is reached during normal operation, the so called HICCUP mode is triggered, and the soft-start cap is discharged and recharged. However, during the start-up phase, additional current is required to charge the output capacitor. This could continuously trigger the HICCUP intervention preventing the system from reaching a steady working condition. For this reason the HICCUP feature is disabled during the start-up phase and a constant current mode is active to charge the output capacitor. In this case, when the peak current limit is triggered after a conduction time equal to the "masking time", the high-side MOSFET is turned off and the low side MOSFET is kept on until the flowing current goes below the "valley" current limit. If necessary, some switching pulses are skipped, as illustrated in Figure 11. Thus, the combination of the "peak" and "valley" current limits assure the effectiveness of the overcurrent protection even in extreme duty cycle conditions. The current threshold of the low side is designed higher than the high side one to guarantee the proper protection.

The constant current mode during the soft-start phase limits the maximum current up to:

#### **Equation 7**

$$I_{MAX} = I_{VALLEY\_TH} + \frac{V_{IN} - V_{OUT}}{L} \cdot T_{MASK}$$

The overcurrent limit protection is adjustable (higher or lower than the nominal value) through an external resistor. To guarantee effective protection, both thresholds (valley and peak) are in tracking.

The typical active thresholds in case of ILIM-ADJ pin left floating are  $I_{PEAK\_TH}$  = 4.0 A,  $I_{VALLEY\_TH}$  = 4.7 A. The dimensioning of the pull up resistor versus VREF to decrease the peak (and valley) thresholds follows the formula:

#### **Equation 8**

$$R_9(\Omega) = \frac{1.2 \cdot 10^5}{4.0 - I_{PEAK\_TH}}$$

In the same way the pull down resistor is selected using the following formula to increase the maximum current thresholds:

#### **Equation 9**

$$R_3(\Omega) = \frac{2.706 \cdot 10^5}{I_{PEAK\_TH} - 4.0}$$

Table 9 shows some resistor values to adjust the current limits

Table 9. ILIM-ADJ resistor examples

| <b>R9(k</b> Ω) | I <sub>LIM PEAK</sub> (A) | I <sub>LIM VALLEY</sub> (A) | <b>R3(k</b> Ω) | I <sub>LIM PEAK</sub> (A) | I <sub>LIM VALLEY</sub> (A) |

|----------------|---------------------------|-----------------------------|----------------|---------------------------|-----------------------------|

| 43             | 1.24                      | 1.62                        | 1500           | 4.2                       | 4.75                        |

| 47             | 1.47                      | 1.87                        | 750            | 4.38                      | 4.95                        |

| 56             | 1.88                      | 2.31                        | 470            | 4.6                       | 5.18                        |

| 68             | 2.26                      | 2.71                        | 330            | 4.8                       | 5.42                        |

| 91             | 2.71                      | 3.18                        | 270            | 5.0                       | 5.62                        |

| 120            | 3.03                      | 3.52                        | 220            | 5.20                      | 5.82                        |

| 200            | 3.43                      | 3.94                        | 180            | 5.50                      | 6.12                        |

| 560            | 3.81                      | 4.35                        | 160            | 5.70                      | 6.30                        |

#### 5.5.3 UVLO

The under-voltage-lockout (UVLO) is adjustable by the multifunction pin (see Section 5.1 on page 13). It is possible to set two different thresholds:

- 2.9 V for 3.3 V BUS

- 8 V for 12 V BUS

#### 5.5.4 Thermal shutdown

When the junction temperature reaches 150 °C the device enters in thermal shutdown. Both MOSFETs are turned off and the soft-start capacitor is discharged with a current of 22  $\mu$ A. The device doesn't restart until the junction temperature goes down to 120 °C.

#### 5.6 Minimum on time

The L5988D is based on a voltage mode control loop. The advantage of this technique is the very short conduction time of the power elements thanks to the proper functioning of the control loop without a current sense (that is challenging with low conduction times), which instead is required in current mode regulators. The optimized architecture, the design solutions and the high performance fabrication technique allow power elements to achieve extremely short conduction times. This allows very high switching frequency operation even in very low duty cycle applications. *Figure 12* shows how the L5988D can easily manage a minimum conduction time of 200ns. Moreover, thanks to the embedded P-MOS used for the high-side, no bootstrap capacitor is required. This means that the device is able to manage a duty cycle of 100%.

Figure 12. Minimum T<sub>ON</sub>

## 5.7 Error amplifier

The error amplifier (E/A) provides the error signal to be compared with the sawtooth to perform the pulse width modulation. Its non-inverting input is internally connected to a 0.6 V voltage reference, while its inverting input (FB) and output (COMP) are externally available for feedback and frequency compensation. In this device the error amplifier is a voltage mode operational amplifier so with high DC gain and low output impedance.

The uncompensated error amplifier characteristics are the following:

| Parameter description       | Value         |  |

|-----------------------------|---------------|--|

| Low frequency gain          | 100 dB        |  |

| GBWP                        | 4.5 MHz       |  |

| Slew rate                   | 7 V/μs        |  |

| Output voltage swing        | 0 to 3.3 V    |  |

| Maximum source/sink current | 25 mA / 40 mA |  |

Table 10. Uncompensated error amplifier

In continuous conduction mode (CCM), the transfer function of the power section has two poles due to the LC filter and one zero due to the ESR of the output capacitor. Different kinds of compensation networks can be used depending on the ESR value of the output capacitor. In case the zero introduced by the output capacitor helps to compensate the double pole of the LC filter a type II compensation network can be used. Otherwise, a type III compensation network has to be used (see *Section 6.4 on page 28* for details about the compensation network selection).

Anyway the methodology to compensate the loop is to introduce zeros to obtain a safe phase margin.

577

## 6 Application information

### 6.1 Input capacitor selection

The capacitor connected to the input has to be capable to support the maximum input operating voltage and the maximum RMS input current required by the device. The input capacitor is subject to a pulsed current, the RMS value of which is dissipated over its ESR, affecting the overall system efficiency.

So the input capacitor must have a RMS current rating higher than the maximum RMS input current and an ESR value compliant with the expected efficiency.

The maximum RMS input current flowing through the capacitor can be calculated as:

#### **Equation 10**

$$I_{RMS} = I_O \cdot \sqrt{D - \frac{2 \cdot D^2}{\eta} + \frac{D^2}{\eta^2}}$$

Where *Io* is the maximum DC output current, *D* is the duty cycles,  $\eta$  is the efficiency. This function has a maximum at D = 0.5 and, considering  $\eta$  = 1, it is equal to Io/2.

In a specific application the range of possible duty cycles has to be considered in order to find out the maximum RMS input current. The maximum and minimum duty cycles can be calculated as:

#### **Equation 11**

$$D_{MAX} = \frac{V_{OUT} + \Delta V_{LOW\_SIDE}}{V_{INMIN} + \Delta V_{LOW\_SIDE} - \Delta V_{HIGH\_SIDE}}$$

and

#### **Equation 12**

$$\mathsf{D}_{\mathsf{MIN}} = \frac{\mathsf{V}_{\mathsf{OUT}} + \Delta \mathsf{V}_{\mathsf{LOW\_SIDE}}}{\mathsf{V}_{\mathsf{INMAX}} + \Delta \mathsf{V}_{\mathsf{LOW\_SIDE}} - \Delta \mathsf{V}_{\mathsf{HIGH\_SIDE}}}$$

Where  $\Delta V_{HIGH\ SIDE}$  and  $\Delta V_{LOW\ SIDE}$  are the voltage drops across the embedded switches.

The peak to peak voltage across the input filter can be calculated as:

#### **Equation 13**

$$V_{PP} = \frac{I_{O}}{C_{IN} \cdot f_{SW}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right] + ESR \cdot I_{O}$$

Given a physical dimension, ceramic capacitors can met well the requirements of the input filter substaining an higher input current than electrolytic / tantalum types. In this case the equation of  $C_{\mathsf{IN}}$  as a function of the target  $V_{\mathsf{PP}}$  can be written as follows:

#### **Equation 14**

$$C_{IN} = \frac{I_O}{V_{PP} \cdot f_{SW}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right]$$

Considering  $\eta = 1$  this function has its maximum in D = 0.5:

#### **Equation 15**

$$C_{IN\_MIN} = \frac{I_O}{2 \cdot V_{PP\ MAX} \cdot f_{SW}}$$

Typically  $C_{IN}$  is dimensioned to keep the maximum peak-peak voltage across the input filter in the order of 1%  $V_{IN\ MAX}$ .

Manufacture

Series

Cap value (μF)

Rated voltage (V)

MURATA

GRM31

10

25

GRM55

10

25

TDK

C3225

10

25

Table 11. Input capacitors

### 6.2 Inductor selection

The inductance value fixes the current ripple flowing through the output capacitor. So the minimum inductance value in order to have the expected current ripple has to be selected. The rule to fix the current ripple value is to have a ripple at 20% - 40% of the output current. The inductance value can be calculated by the following equation:

#### **Equation 16**

$$\Delta I_{L} = \frac{V_{IN} - V_{OUT}}{I} \cdot T_{ON} = \frac{V_{OUT}}{I} \cdot T_{OFF}$$

Where  $T_{ON}$  and  $T_{OFF}$  are the on and off time of the internal power switch. The maximum current ripple, at fixed Vout, is obtained at maximum  $T_{OFF}$  that is at minimum duty cycle (see previous section to calculate minimum duty). So fixing  $\Delta I_L = 20\%$  to 40% of the maximum output current, the minimum inductance value can be calculated:

#### **Equation 17**

$$L_{MIN} = \frac{V_{OUT} + V_F}{\Delta I_{MAX}} \cdot \frac{1 - D_{MIN}}{F_{SW}}$$

where  $F_{SW}$  is the switching frequency  $1/(T_{ON} + T_{OFF})$ .

For example for  $V_{OUT}$  = 3.3 V,  $V_{IN}$  = 12 V,  $I_O$  = 4 A and  $F_{SW}$  = 400 kHz the minimum inductance value to have  $\Delta I_L$  = 30% of  $I_O$  is about 4.7  $\mu$ H.

The peak current through the inductor is given by:

#### **Equation 18**

$$I_{L,PK} = I_O + \frac{\Delta I_L}{2}$$

So if the inductor value decreases, the peak current (that has to be lower than the current limit of the device) increases. The higher is the inductor value, the higher is the average output current that can be delivered, without reaching the current limit.

577

In *Table 12* some inductor part numbers are listed.

| Manufacturer | Series          | Inductor value (μH) | Saturation current (A) |

|--------------|-----------------|---------------------|------------------------|

| Coilcraft    | XPL7030         | 2.2 to 4.7          | 6.8 to 10.5            |

|              | MSS1048         | 2.2 to 6.8          | 4.14 to 6.62           |

|              | MSS1260         | 10                  | 5.5                    |

|              | WE-HC/HCA       | 3.3 to 4.7          | 7 to 11                |

| Wurth        | WE-TPC type XLH | 3.6 to 6.2          | 4.5 to 6.4             |

|              | WE-PD type L    | 10                  | 5.6                    |

| Coiltronics  | DR74            | 3.3 to 4.7          | 4.3 to 5.4             |

|              | DR125           | 10                  | 5.3                    |

| BI           | HM78-60         | 4.7 to 10           | 5.4 to 6.8             |

| SUMIDA       | HM78-60         | 4.7 to 10           | 5.4 to 6.8             |

**Table 12. Inductors**

### 6.3 Output capacitor selection

The current in the capacitor has a triangular waveform (with zero average value) which generates a voltage ripple across it. This ripple is due to the capacitive component and the resistive component (ESR). So the output capacitor has to be selected in order to have a voltage ripple compliant with the application requirements.

The amount of the voltage ripple can be calculated starting from the current ripple obtained by the inductor selection.

#### **Equation 19**

$$\Delta V_{OUT} = ESR \cdot \Delta I_{MAX} + \frac{\Delta I_{MAX}}{8 \cdot C_{OUT} \cdot f_{SW}}$$

Usually the resistive component of the ripple is much higher than the capacitive one, if the output capacitor adopted is not a multi layer ceramic capacitor (MLCC) with very low ESR value.

The output capacitor is important also for loop stability: it fixes the double LC filter pole and the zero due to its ESR. In *Section 6.4*, it will be illustrated how to consider its effect in the system stability.

For example with V<sub>OUT</sub> = 3.3 V, V<sub>IN</sub> = 12 V,  $\Delta I_L$  = 0.6 A (resulting by the inductor value), in order to have a  $\Delta V_{OUT}$  = 0.01·V<sub>OUT</sub>, if the multi layer capacitor are adopted, 10  $\mu F$  are needed and the ESR effect on the output voltage ripple can be neglected. In case of not negligible ESR (electrolytic or tantalum capacitors), the capacitor is chosen taking into account its ESR value. So 100  $\mu F$  with ESR = 40 m $\Omega$  is compliant with the requested output voltage ripple.

The output capacitor is also important to sustain the output voltage when a load transient with high slew rate is required by the load. When the load transient slew rate exceeds the system bandwidth the output capacitor provides the current to the load. So if the high slew rate load transient is required by the application the output capacitor and system bandwidth

have to be chosen in order to sustain load transient and to have a fast response to the transient.

In Table 13 some capacitor series are listed.

| Table 10. Output capacitors |         |                |                   |                   |

|-----------------------------|---------|----------------|-------------------|-------------------|

| Manufacturer                | Series  | Cap value (μF) | Rated voltage (V) | ESR (m $\Omega$ ) |

| MURATA                      | GRM32   | 22 to 100      | 6.3 to 25         | < 5               |

|                             | GRM31   | 10 to 47       | 6.3 to 25         | < 5               |

| PANASONIC                   | ECJ     | 10 to 22       | 6.3               | < 5               |

|                             | EEFCD   | 10 to 68       | 6.3               | 15 to 55          |

| SANYO                       | TPA/B/C | 100 to 470     | 4 to 16           | 40 to 80          |

| TDK                         | C3225   | 22 to 100      | 6.3               | < 5               |

Table 13. Output capacitors

### 6.4 Compensation network

The compensation network has to assure stability and good dynamic performance. The loop of the L5988D is based on the voltage mode control. The error amplifier is a voltage operational amplifier with high bandwidth. So selecting the compensation network the E/A will be considered as ideal, that is, its bandwidth is much larger than the system one.

The transfer functions of PWM modulator and the output LC filter are studied. The transfer function PWM modulator, from the error amplifier output (COMP pin) to the OUT pin, results:

Equation 20

$$G_{PW0}(f_{SW0}) = \frac{V_{IN}}{V_s} \cdot H(f_{SW0})$$

where  $V_S$  is the sawtooth amplitude and H represent its reliance on the switching frequency. As seen in Section 5.2 on page 15, the voltage feed forward generates a sawtooth amplitude directly proportional to the input voltage, that is:

#### **Equation 21**

$$V_{S}(f_{SW0}) = K \cdot V_{IN} \cdot H(f_{SW0})$$

The internal saw tooth is designed in order to have the maximum amplitude at the natural switching frequency of the device.

At  $f_{SW0}$  = 400 kHz the PWM modulator can be written as:

#### **Equation 22**

$$G_{PW0}(400 \text{ kHz}) = \frac{1}{K} = \frac{V_{IN}}{V_{S}(400 \text{ kHz})} = 9$$

The synchronization of the device with an external clock fed into the SYNCH pin and the adjustment of the switching frequency through the FSW pin modify the gain of the internal saw tooth (see *Section 5.2 on page 15*).

577

The PWM modulator gain is a function of the switching frequency:

#### **Equation 23**

$$G_{PW0}(f_{SW}) = G_{PW0}(400 \text{ kHz}) \cdot \frac{f_{SW}(kHz)}{400} = 9 \cdot \frac{f_{SW}(kHz)}{400}$$

The transfer function on the LC filter is given by:

#### **Equation 24**

$$G_{LC}(s) = \frac{1 + \frac{s}{2\pi \cdot f_{zESR}}}{1 + \frac{s}{2\pi \cdot Q \cdot f_{LC}} + \left(\frac{s}{2\pi \cdot f_{LC}}\right)^2}$$

where:

#### **Equation 25**

$$f_{LC} = \frac{1}{2\pi \cdot \sqrt{L \cdot C_{OUT}} \cdot \sqrt{1 + \frac{ESR}{R_{OUT}}}}, \qquad f_{zESR} = \frac{1}{2\pi \cdot ESR \cdot C_{OUT}}$$

#### **Equation 26**

$$\label{eq:Q} Q \, = \, \frac{\sqrt{R_{OUT} \cdot L \cdot C_{OUT} \cdot (R_{OUT} + ESR)}}{L + C_{OUT} \cdot R_{OUT} \cdot ESR}, \qquad \quad R_{OUT} = \frac{V_{OUT}}{I_{OUT}}$$

Two different kinds of networks can compensate the loop depending on the output capacitor.

Type II network is used to compensate the loop with high ESR output capacitors, type III with low ESR output capacitors (MLCC). In the two following paragraph the guidelines to select the Type II and Type III compensation network are illustrated.

#### 6.4.1 Type III compensation network

The methodology to stabilize the loop consists of placing two zeros to compensate the effect of the LC double pole, so increasing phase margin; then to place one pole in the origin to minimize the dc error on regulated output voltage; finally to place other poles far away the zero dB frequency.

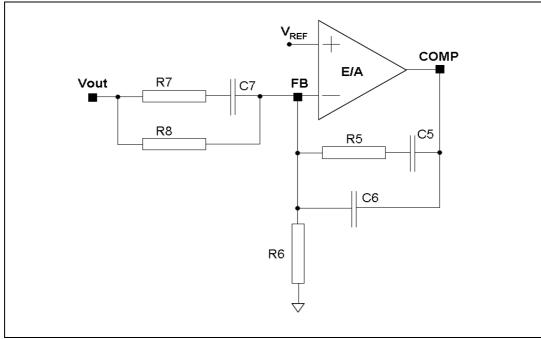

In *Figure 13* the type III compensation network is shown. This network introduces two zeros  $(f_{Z1}, f_{Z2})$  and three poles  $(f_{P0}, f_{P1}, f_{P2})$ . They expression are:

### **Equation 27**

$$f_{Z1} = \frac{1}{2\pi \cdot C_7 \cdot (R_8 + R_7)}, \qquad f_{Z2} = \frac{1}{2\pi \cdot R_5 \cdot C_5}$$

#### **Equation 28**

$$f_{P0} = 0, \qquad f_{P1} = \frac{1}{2\pi \cdot R_7 \cdot C_7}, \qquad f_{P2} = \frac{1}{2\pi \cdot R_5 \cdot \frac{C_5 \cdot C_6}{C_5 + C_6}}$$

Figure 13. Type III compensation network

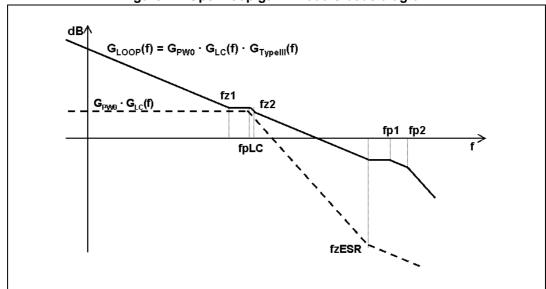

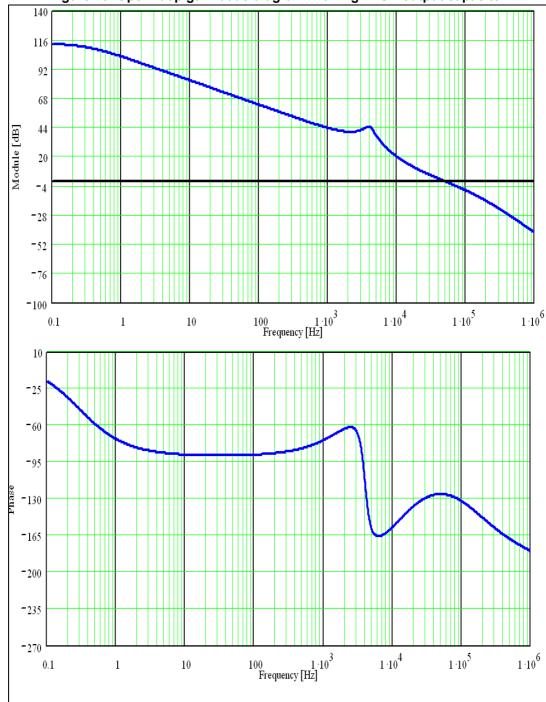

In Figure 14 the Bode diagram of the PWM and LC filter transfer function [ $G_{PW0} \cdot G_{LC}(f)$ ] and the open loop gain [ $G_{LOOP}(f) = G_{PW0} \cdot G_{LC}(f) \cdot G_{TYPEIII}(f)$ ] are drawn.

Figure 14. Open loop gain: module bode diagram

The guidelines for positioning the poles and the zeroes and for calculating the component values can be summarized as follow:

- 1. Choose a value for  $R_1$ , usually between 1  $k\Omega$  and 5  $k\Omega$ .

- 2. Choose a gain (R<sub>5</sub>/R<sub>8</sub>) in order to have the required bandwidth (BW), that means:

#### **Equation 29**

$$R_5 = \frac{BW}{f_{LC}} \cdot \frac{1}{K} \cdot R_8$$

where K is the feed forward constant and 1/K is equals to 18.

3. Calculate C<sub>5</sub> by placing the zero at 50% of the output filter double pole frequency (f<sub>LC</sub>):

#### **Equation 30**

$$C_5 = \frac{1}{\pi \cdot R_5 \cdot f_{LC}}$$

4. Calculate  $C_6$  by placing the second pole at four times the system bandwidth (BW):

#### **Equation 31**

$$C_6 = \frac{C_5}{2\pi \cdot R_5 \cdot C_5 \cdot 4 \cdot BW - 1}$$

5. Set also the fist pole at four times the system bandwidth and also the second zero at the output filter double pole:

#### **Equation 32**

$$R_7 = \frac{R_8}{\frac{4 \cdot BW}{f_{1,C}} - 1}, \qquad C_7 = \frac{1}{2\pi \cdot R_7 \cdot 4 \cdot BW}$$

The suggested maximum system bandwidth is equals to the switching frequency divided by 3.5 ( $F_{SW}$ /3.5), anyway lower than 120 kHz if the  $F_{SW}$  is set higher than 500kHz.

For example with V<sub>OUT</sub> = 1.2 V, V<sub>IN</sub> = 12 V, I<sub>O</sub> = 4 A, L = 4.7  $\mu$ H, C<sub>OUT</sub> = 47  $\mu$ F, the type III compensation network is:

#### **Equation 33**

$$R_8 = 4.7 \text{k}\Omega, \quad R_6 = 4.7 \text{k}\Omega, \quad R_7 = 56\Omega, \quad R_5 = 1.2 \text{K}\Omega, \quad C_7 = 10 \text{nF}, \quad C_5 = 22 \text{nF}, \quad C_6 = 1 \text{nF}$$

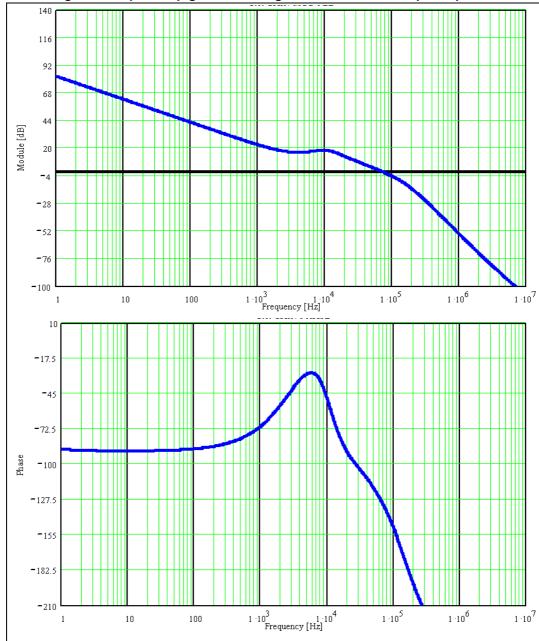

In *Figure 15* is shown the module and phase of the open loop gain. The bandwidth is about 68 kHz and the phase margin is  $50^{\circ}$ .

Figure 15. Open loop gain bode diagram with ceramic output capacitor

#### 6.4.2 Type II compensation network

In Figure 16 the type II network is shown.

Vout R8 FB C5

Figure 16. Type II compensation network

The singularities of the network are:

#### **Equation 34**

$$f_{Z1} = \frac{1}{2\pi \cdot R_5 \cdot C_5}, \qquad f_{P0} = 0, \qquad f_{P1} = \frac{1}{2\pi \cdot R_5 \cdot \frac{C_5 \cdot C_6}{C_5 + C_6}}$$

In Figure 17 the bode diagram of the PWM and LC filter transfer function ( $G_{PW0} \cdot G_{LC}(f)$ ) and the open loop gain ( $G_{LOOP}(f) = G_{PW0} \cdot G_{LC}(f) \cdot G_{TYPEII}(f)$ ) are drawn.

$dB / G_{LOOP}(f) = G_{PW0} \cdot G_{LC}(f) \cdot G_{Typell}(f)$   $G_{PW0} \cdot G_{LC}(f)$  fz1 fpLC fp1 f

Figure 17. Open loop gain: module bode diagram

The guidelines for positioning the poles and the zeroes and for calculating the component values can be summarized as follow:

- 1. Choose a value for R<sub>8</sub>, usually between 1k and 5k, in order to have values of C5 and C6 not comparable with parasitic capacitance of the board.

- 2. Choose a gain (R<sub>5</sub>/R<sub>8</sub>) in order to have the required bandwidth (BW), that means:

#### **Equation 35**

$$R_5 = \left(\frac{f_{ESR}}{f_{LC}}\right)^2 \cdot \frac{BW}{f_{ESR}} \cdot \frac{V_S}{V_{IN}} \cdot R_8$$

Where  $f_{ESR}$  is the ESR zero:

#### **Equation 36**

$$f_{ESR} = \frac{1}{2\pi \cdot ESR \cdot C_{OUT}}$$

and  $V_S$  is the saw-tooth amplitude. The voltage feed forward keeps the ratio Vs/Vin constant.

3. Calculate C<sub>5</sub> by placing the zero one decade below the output filter double pole:

#### **Equation 37**

$$C_5 = \frac{10}{2\pi \cdot R_5 \cdot f_{LC}}$$

4. Then calculate C<sub>7</sub> in order to place the second pole at four times the system bandwidth (BW):

#### **Equation 38**

$$C_7 = \frac{C_5}{2\pi \cdot R_5 \cdot C_5 \cdot 4 \cdot BW - 1}$$

For example with V<sub>OUT</sub> = 1.2V, V<sub>IN</sub> = 12 V, I<sub>O</sub> = 4 A, L = 4.7  $\mu$ H, C<sub>OUT</sub> = 330  $\mu$ F, ESR = 35 m $\Omega$ , the type II compensation network is:

#### **Equation 39**

$${\rm R_8 = 4.7 k\Omega}, \quad {\rm R_6 = 4.7 K\Omega}, \quad {\rm R_5 = 22 k\Omega}, \quad {\rm C_5 = 2.2 nF}, \quad {\rm C_6 = 33 pF}$$

In *Figure 18* is shown the module and phase of the open loop gain. The bandwidth is about 42 kHz and the phase margin is 56°.

Figure 18. Open loop gain bode diagram with high ESR output capacitor

The response of the system to a load transition in terms of output voltage regulation is affected not only by the designed compensation network but it also rely on the selection of the power components (the inductor value, for example, limits the slew rate of the current).

Some measurements of the output regulation during load transient for the examples provided in Section 6.8 on page 43 are provided at the end of this document.

## 6.5 R.M.S. current of the embedded power MOSFETs

The L5988D integrates both the power elements (high side and low side) and so the power dissipation is often the bottleneck for the output current capability (refer to *Section 6.6* for the estimation of the operating temperature).

Nevertheless, as mentioned in *Section 1: Description on page 6* the device can manage a continuous output current of 4 A in most of the application conditions.

However the rated continuous current is 5 A and the rated RMS current of the power elements is 4.5 A, where:

#### **Equation 40**

$$I_{RMS HS} = I_{LOAD} \cdot \sqrt{D}$$

#### **Equation 41**

$$I_{RMSLS} = I_{LOAD} \cdot \sqrt{1 - D}$$

and the duty cycle D:

#### **Equation 42**

$$D = \frac{V_{OUT} + (R_{DS ON LS} + DCR) \cdot I_{LOAD}}{V_{IN} + (R_{DS ON LS} - R_{DS ON HS}) \cdot I_{LOAD}}$$

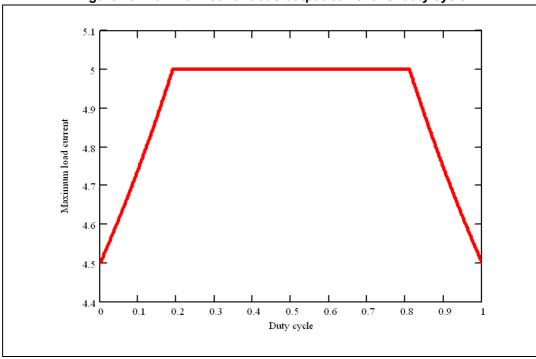

Fixing the limit of 4.5 A for  $I_{RMS\ HS}$  and  $I_{RMS\ LS}$  the maximum output current can be derived, as illustrated in *Figure 19*.

Figure 19. Maximum continuous output current vs. duty cycle

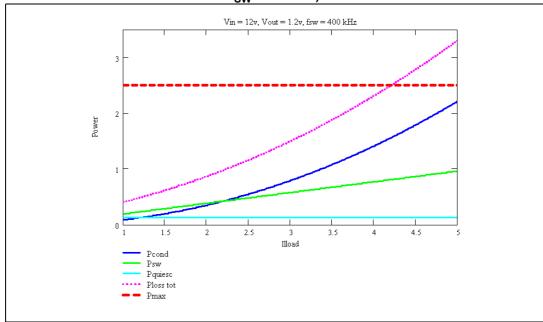

### 6.6 Thermal considerations

The thermal design is important to prevent the thermal shutdown of the device if the junction temperature goes above 150 °C. The three different sources of losses within the device are:

conduction losses due to the not negligible R<sub>DSON</sub> of the power switch; these are equal to:

### **Equation 43**

$$\mathsf{P}_{\mathsf{ON}} = \, \mathsf{R}_{\mathsf{DSON\_HS}} \cdot (\mathsf{I}_{\mathsf{OUT}})^2 \cdot \mathsf{D} + \mathsf{R}_{\mathsf{DSON\_LS}} \cdot (\mathsf{I}_{\mathsf{OUT}})^2 \cdot (1 - \mathsf{D})$$

Where D is the duty cycle of the application. Note that the duty cycle is theoretically given by the ratio between  $V_{OUT}$  an  $V_{IN}$ , but actually it is quite higher to compensate the losses of the regulator. So the conduction losses increases compared with the ideal case.

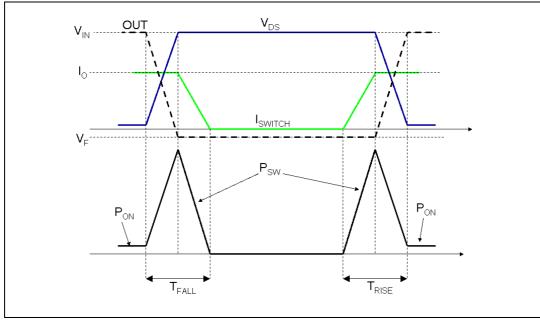

switching losses due to power MOSFET turn ON and OFF; these can be calculated as:

### **Equation 44**

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \frac{(\mathsf{T}_{\mathsf{RISE}} + \mathsf{T}_{\mathsf{FALL}})}{2} \cdot \mathsf{Fsw} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{T}_{\mathsf{SW}} \cdot \mathsf{F}_{\mathsf{SW}}$$

Where  $T_{RISE}$  and  $T_{FALL}$  represent the switching times of the power element that cause the switching losses when driving an inductive load (see *Figure 20*).  $T_{SW}$  is the equivalent switching time.

Figure 20. Switching losses

c) Quiescent current losses, calculated as:

### **Equation 45**

$$P_Q = V_{IN} \cdot I_Q$$

where  $I_{O}$  is the quiescent current.

The junction temperature T<sub>J</sub> can be calculated as:

### **Equation 46**

$$T_J = T_A + Rth_{JA} \cdot P_{TOT}$$

Where  $T_A$  is the ambient temperature and  $P_{TOT}$  is the sum of the power losses just seen.

$R_{thJA}$  is the equivalent static thermal resistance junction to ambient of the device; it can be calculated as the parallel of many paths of heat conduction from the junction to the ambient. For this device the path through the exposed pad is the one conducting the largest amount of heat. The static  $Rth_{JA}$  measured on the application is about 40 °/W.

The thermal impedance of the system, considered as the device in HTSSOP16 package soldered on the application board, takes on an important rule when the maximum output power is limited by the static thermal performance and not by the electrical performance of the device. Therefore the embedded power elements could manage an higher current but the system is already taking away the maximum power generated by the internal losses.

In case the output power increases the thermal shutdown will be triggered because the junction temperature triggers the designed thermal shutdown threshold.

The R<sub>TH</sub> is a static parameter of the package: it sets the maximum power loss which can be generated from the system given the operation conditions.