# TCM4400 Data Manual

## GSM/DCS Baseband and Voice A/D D/A Interface Circuit

SLWS029B January 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

## Contents

| Sec | tion                     | Title                                                                                                                                                                                                                                                                             | Page              |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|     | 1.1<br>1.2<br>1.3<br>1.4 | Features Functional Block Diagram Terminal Assignments Terminal Functions                                                                                                                                                                                                         | 1–1<br>1–2<br>1–3 |

|     | 2.1<br>2.2<br>2.3        | trical Specifications                                                                                                                                                                                                                                                             | 2–1<br>2–1        |

|     | Ranç                     | 2.3.1 Digital Inputs And Outputs 2.3.2 Voltage References 2.3.3 Master Clock Input (MCLK)                                                                                                                                                                                         | 2–1<br>2–2        |

|     |                          | <ul> <li>2.3.4 Baseband Uplink Path</li> <li>2.3.5 dc Accuracy – Baseband Uplink Path</li> <li>2.3.6 Dynamic Parameters – Baseband Uplink Path</li> </ul>                                                                                                                         | 2–3<br>2–3<br>2–3 |

|     | 2.4                      | <ul> <li>2.3.7 Smoothing Filters Characteristics – Baseband Uplink Path</li> <li>2.3.8 I and Q Channels Gain and Phase Matching – Baseband Uplink Path</li> <li>2.3.9 Baseband Uplink Path Global Characteristics</li> <li>Timing Requirements of Baseband Uplink Path</li> </ul> | 2–3<br>2–4        |

|     | 2.4                      | 2.4.1 Programmable Delays – Baseband Uplink Path  2.4.2 Fixed Delays – Baseband Uplink Path  2.4.3 Baseband Downlink Path  2.4.4 dc Accuracy – Baseband Downlink Path                                                                                                             | 2–4<br>2–4<br>2–4 |

|     | 2.5                      | Channel Characteristics                                                                                                                                                                                                                                                           | 2–5<br>2–5<br>2–5 |

|     | 2.6                      | <ul> <li>2.5.4 Group Delay – Baseband Downlink Path</li></ul>                                                                                                                                                                                                                     | 2–5<br>2–6<br>2–6 |

|     | 2.7                      | Automatic Power Control (APC)  2.7.1 APC Level (8-bit DAC)  2.7.2 APC Shaper (5-bit DAC)  2.7.3 APC Output Stage                                                                                                                                                                  | 2–6<br>2–6<br>2–6 |

|     | 2.8                      | Monitoring ADC  2.8.1 10-bit ADC                                                                                                                                                                                                                                                  | 2–7               |

|     | 2.9                      | Automatic Gain Control (AGC)                                                                                                                                                                                                                                                      | 2–7               |

|   |      | 2.9.2 AGC Output Stage                                                | 2–8    |

|---|------|-----------------------------------------------------------------------|--------|

|   | 2.10 | Automatic Frequency Control (AFC)                                     | 2–8    |

|   |      | 2.10.1 AFC 13-bit DAC                                                 | 2–8    |

|   |      | 2.10.2 AFC Output Stage                                               | 2–8    |

|   | 2.11 | Voice Uplink Path                                                     | 2–9    |

|   |      | 2.11.1 Global Characteristics of Voice Uplink Path                    | 2–9    |

|   |      | 2.11.2 Frequency Response of the Voice Band Uplink Path               |        |

|   |      | 2.11.3 Psophometric SNR vs Signal Level of the Voice Band Uplink Path | . 2–10 |

|   |      | 2.11.4 Gain Characteristics of the Voice Band Uplink Path             | . 2–10 |

|   | 2.12 | Voice Downlink Path                                                   | . 2–11 |

|   |      | 2.12.1 Global Characteristics of Voice Downlink Path                  | . 2–11 |

|   |      | 2.12.2 Frequency Response of the Voice Band Downlink Path             | . 2–12 |

|   |      | 2.12.3 Psophometric SNR vs Signal Level Downlink Path                 | . 2–12 |

|   |      | 2.12.4 Gain Characteristics of the Voice Band Downlink Path           | . 2–13 |

|   | 2.13 | Power Consumption                                                     | . 2–14 |

|   |      | 2.13.1 Consumption by Circuit Block                                   | . 2–14 |

|   |      | 2.13.2 Current Consumption for Typical Configurations                 | . 2–14 |

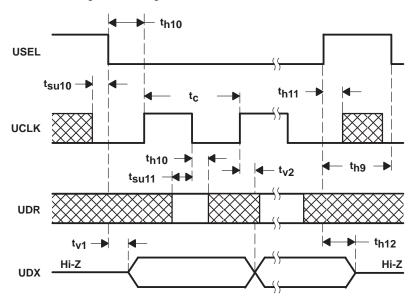

|   |      | 2.13.3 MCU Serial Interface Timing Requirements                       | . 2–15 |

|   |      | 2.13.4 DSP Serial Interface Timing Requirements                       |        |

|   |      | 2.13.5 Voice Timing Requirements                                      | . 2–15 |

| 3 | Para | nmeter Measurement Information                                        | . 3–1  |

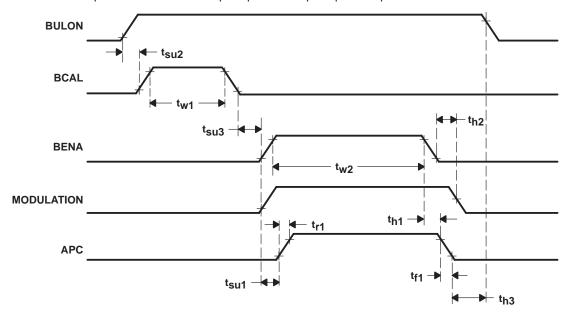

| • | 3.1  | Uplink Timing Considerations                                          |        |

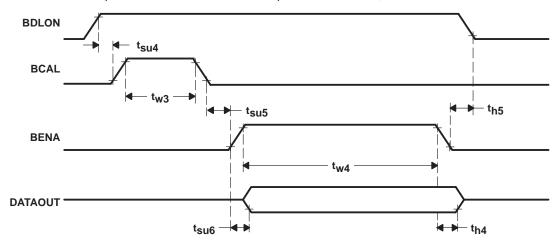

|   | 3.2  | Downlink Timing Considerations                                        |        |

|   | 3.3  | Microcontroller Unit Serial Interface Timing Considerations           |        |

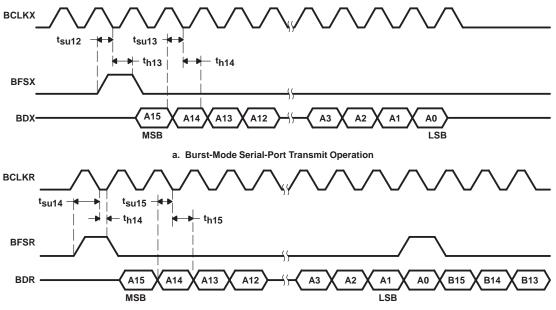

|   | 3.4  | DSP Serial Port Timing Considerations                                 |        |

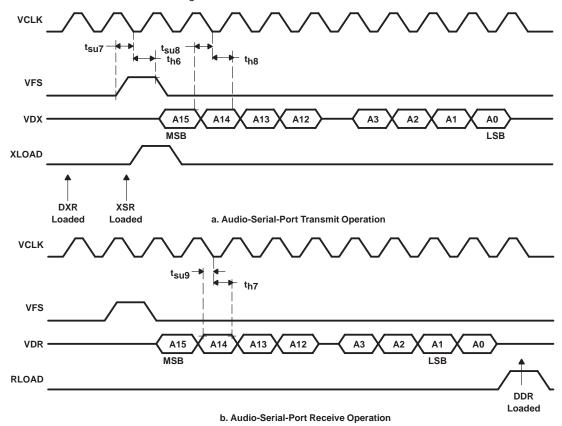

|   | 3.5  | Voice Band Serial Interface Timing Considerations                     |        |

| 4 | Drin | ciples of Operation                                                   |        |

| - | 4.1  |                                                                       |        |

|   | 4.2  | ·                                                                     |        |

|   | 4.3  | Auxiliary RF Functions                                                |        |

|   | 4.5  | 4.3.1 Automatic Frequency Control (AFC)                               |        |

|   |      | 4.3.2 Auxiliary Analog Converter (Automatic Gain Control (AGC))       |        |

|   |      | 4.3.3 RF Power Control                                                |        |

|   |      | 4.3.4 Monitoring                                                      |        |

|   | 4.4  | Voice Codec                                                           |        |

|   |      | 4.4.1 Voice Uplink Path                                               |        |

|   |      | 4.4.2 Voice Downlink Path                                             |        |

|   | 4.5  | DAI Interface                                                         |        |

|   | 4.6  | JTAG Interface                                                        |        |

|   |      | 4.6.1 Standard User Instructions Available                            |        |

|   | 4.7  | JTAG Interface Scan Chain Descriptions                                |        |

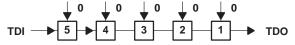

|   |      | 4.7.1 Bypass Register                                                 |        |

|   |      | 4.7.2 Instruction Register                                            |        |

|   |      | 4.7.3 Identification Register                                         |        |

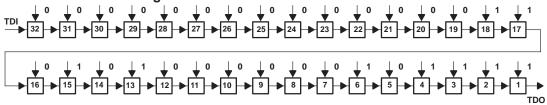

|   |      | 4.7.4 Boundary-Scan Register                                          |        |

|   | 4.8  | Power-Down Functional Description                                     |        |

|   |      | 4.8.1 Direct Control with Internal Register                           |        |

|   |      |                                                                       |        |

|   |      | 4.8.2            | Radio Window Activation Control                       |   |

|---|------|------------------|-------------------------------------------------------|---|

|   |      | 4.8.3            | External Terminal PWRDN Control                       |   |

|   |      |                  | ice Band Serial Interface                             |   |

|   | 4.10 | _                | References                                            |   |

|   |      | 4.10.1           | MCU Serial Baseband Digital Interface                 |   |

|   |      | 4.10.2           | Serial Interface                                      |   |

|   |      | 4.10.3           | DSP/MCU Serial Interface                              |   |

|   |      | 4.10.4           | DSP Serial Digital Interface                          |   |

|   |      | 4.10.5<br>4.10.6 | DSP/MCU Serial Interface Operation and Format         |   |

|   |      | 4.10.6           | DSP/MCU Serial Interface Registers                    |   |

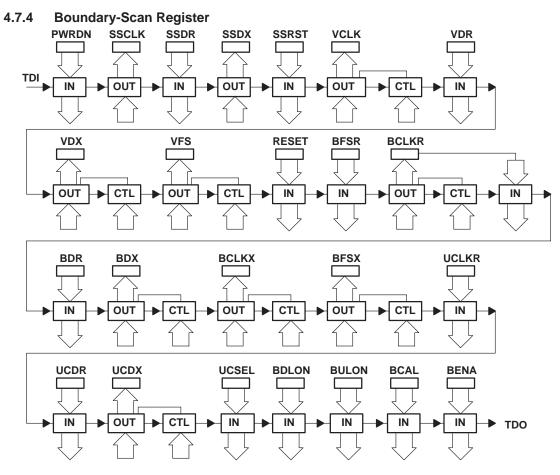

|   |      | 4.10.7           | Baseband Uplink Data Buffer                           |   |

|   |      |                  | Baseband Uplink I and Q Offset Registers 4–18         |   |

|   |      |                  | Baseband Uplink I and Q D/A Conversion Registers 4–20 |   |

|   |      |                  | Power-Down Register 2                                 |   |

|   |      |                  | Power-Down Register No. 1                             |   |

|   |      |                  | Baseband Control Register                             |   |

|   |      |                  | MCU Clocking Schemes                                  |   |

|   |      |                  | Voice Band Uplink Control Register 4–23               |   |

|   |      |                  | Voice Band Downlink Control Register 4–25             |   |

|   |      |                  | Voice Band Control Register 4–26                      |   |

|   |      |                  | Auxiliary Functions Control Register 1                |   |

|   |      | 4.10.19          | Automatic Frequency Control Registers (1 and 2) 4–28  | 3 |

|   |      |                  | Automatic Power Control Register 4–28                 |   |

|   | 4.11 |                  | tic Frequency Control Registers (1 and 2) 4-29        |   |

|   |      |                  | AGC Control Register                                  |   |

|   |      |                  | Auxiliary Functions Control Register 2 4–29           |   |

|   |      |                  | , 1 5                                                 |   |

|   |      | 4.11.4           | Baseband Status Register                              |   |

|   |      | 4.11.5           | Voice Band Control Register 4 (Address 23) 4–31       |   |

|   |      | 4.11.6           | Baseband Uplink Register (Address 24) 4–32            |   |

|   |      | 4.11.7           | Power-On Status Register (Address 25)                 |   |

|   |      | 4.11.8           | Timing and Interface 4–32                             | _ |

| 5 | MEC  | HANICA           | NL DATA 5–1                                           | ı |

# **List of Illustrations**

| Figure | Title                                                  | Page |

|--------|--------------------------------------------------------|------|

| 3–1    | Uplink Timing Diagram                                  | 3–1  |

| 3–2    | Downlink Timing Sequence                               | 3–2  |

| 3–3    | Microcontroller Unit Serial Interface Timing Waveforms | 3–3  |

| 3–4    | DSP Serial Port Timings                                | 3–4  |

| 3–5    | Voice Band Serial Interface Timing Waveforms           | 3–5  |

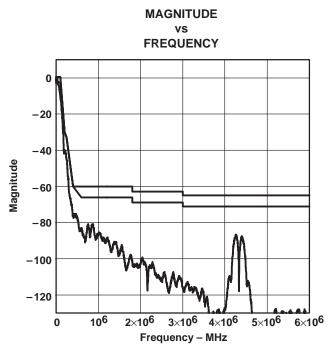

| 4–1    | Typical GSM Modulation Spectrum                        | 4–1  |

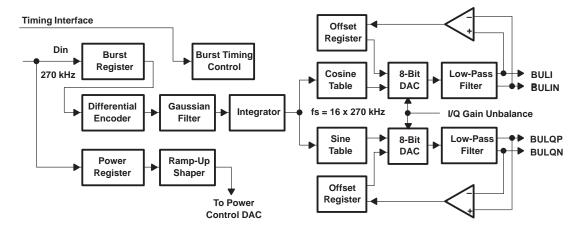

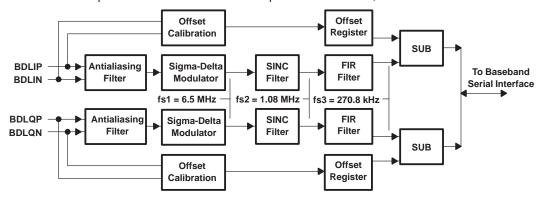

| 4–2    | Functional Structure of The Baseband Uplink Path       | 4–3  |

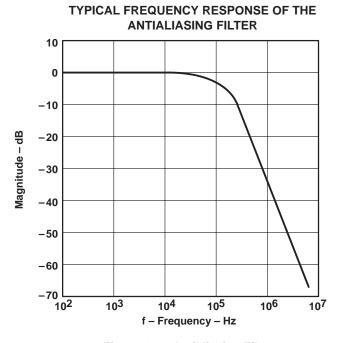

| 4–3    | Antialiasing Filter                                    | 4–3  |

| 4–4    | Functional Structure of the Baseband Downlink Path     | 4–4  |

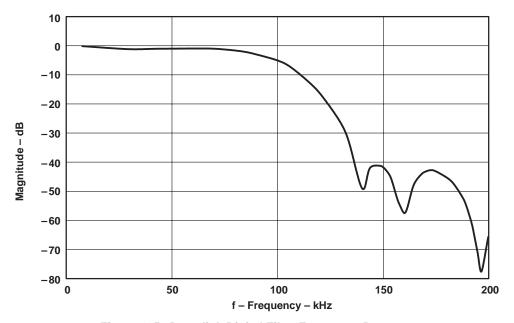

| 4–5    | Downlink Digital Filter Frequency Response             | 4–5  |

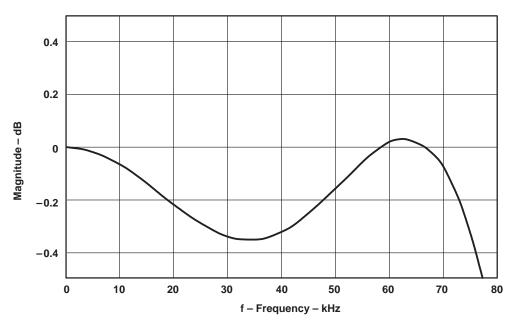

| 4–6    | Downlink Digital Filter In-band Response               | 4–5  |

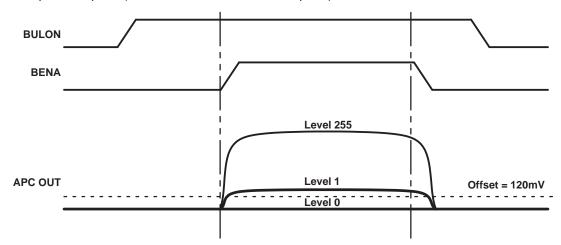

| 4–7    | APC Output When APCMODE = 0                            |      |

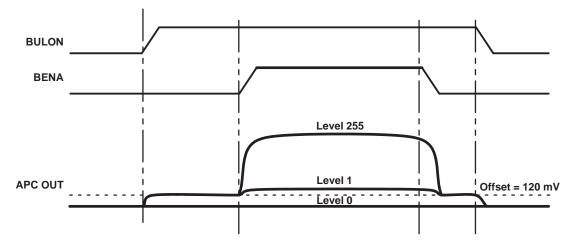

| 4–8    | APC Output When APCMODE = 1                            |      |

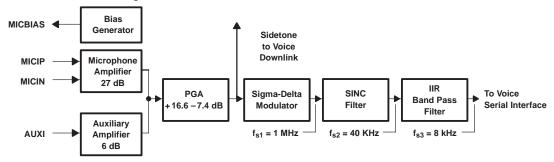

| 4–9    | Uplink Path Block Diagram                              | 4–9  |

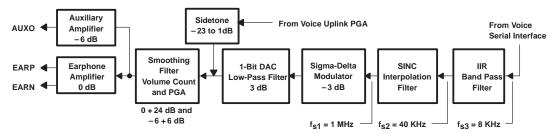

| 4–10   | Downlink Path Block Diagram                            |      |

| 4–11   | DSP Serial Digital Interface                           |      |

| 4–12   | Timing Interface                                       | 4–33 |

## **List of Tables**

| Table | Title                                | Page |

|-------|--------------------------------------|------|

| 4–1   | Voltage References                   | 4–14 |

| 4–2   | Microcontroller Clocking Schemes     | 4–16 |

| 4–3   | Read/Write Data Word                 |      |

| 4–4   | 16-Bit Word Format                   |      |

| 4–5   | Format of 16-Bit Word Transfer       |      |

| 4–6   | Uplink Ramp-Delay Register           |      |

| 4–7   | Uplink Data Buffer                   |      |

| 4–8   | Uplink I Offset Register             | 4-20 |

| 4–9   | Uplink Q Offset Register             |      |

| 4-10  | Uplink I DAC Register                |      |

| 4-11  | Uplink Q DAC Register                | 4-21 |

| 4-12  | PWDNRG2 Register                     | 4-21 |

| 4-13  | PWDNRG1 Register                     | 4-22 |

| 4–14  | Baseband Control Register            | 4-22 |

| 4–15  | MCU Clocking Schemes                 |      |

| 4–16  | Voice Band Uplink Control Register   | 4–23 |

| 4–17  | Uplink PGA Gain                      |      |

| 4–18  | Voice Band Downlink Control Register | 4–25 |

| 4–19  | Downlink PGA Gain                    |      |

| 4–20  | Volume Control Gain Settings         | 4-26 |

| 4–21  | Voice Band Control Register          | 4-26 |

| 4–22  | DAI Mode Selection                   |      |

| 4–23  | AUX Functions Control Register 1     | 4–27 |

| 4–24  | ADC Selection                        |      |

| 4–25  | AFC Selection                        |      |

| 4–26  | AFC Control Register 1               |      |

| 4–27  | AFC Control Register 2               | 4–28 |

| 4–28  | APC Register                         |      |

| 4–29  | APC Ramp Control                     |      |

| 4–30  | Shape DAC Input Register             |      |

| 4–31  | Analog AGC Gain Control Register     |      |

| 4–32  | AUX Functions Control Register 2     |      |

| 4–33  | AUX A/D Converter Output Register    |      |

| 4–34  | Baseband Status Register             |      |

| 4–35  | Voice Band Control Register 4        |      |

| 4–36  | VDLST Status                         |      |

| 4–37  | Uplink Register BULCTL               |      |

| 4–38  | BLKCTL Register                      |      |

| 4–39  | Power-On Status Register PWONCTL     |      |

| 4-40  | 6-Bit TR Register                    | 4-32 |

#### 1 Introduction

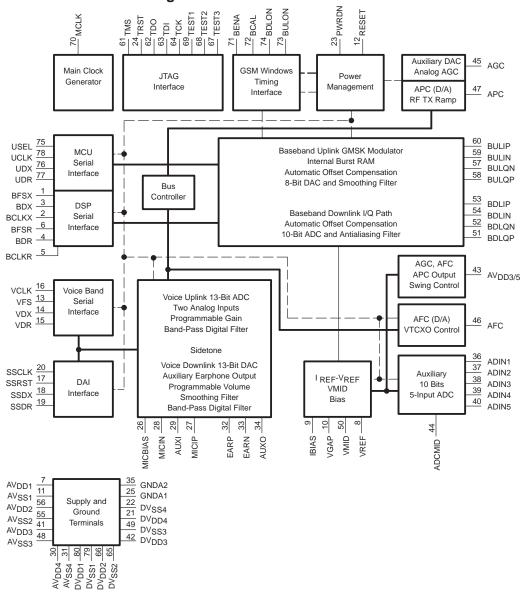

The TCM4400 global system for mobile communication (GSM) baseband RF interface circuit is designed for GSM 900 and DCS 1800 European digital cellular systems (DCS), and PCS 1900 North America personal communications systems (PCS). It includes a complete set of functions to perform the interface and processing of voice signals, generate baseband in-phase (I) and quadrature (Q) signals, and control the signals between a digital signal processor (DSP) and associated RF circuits.

The TCM4400 includes a second serial interface for use with a microcontroller. Through this interface, a microcontroller can access all the internal registers that can be accessed through the DSP digital serial interface. This option is for applications in which part of the L1 software is implemented in the microcontroller.

A 4-pin parallel port is dedicated to the full control of the digital audio interface (DAI) to the GSM system simulator; the DAI consists of system simulator reset (SSRST) control, clock generation, and rate adaptation with the DSP.

The voice processing portion of the device includes microphone and earphone amplifiers, analog-to-digital converter (ADC) and digital-to-analog converter (DAC), speech digital filtering, and a serial port.

The baseband processing portion of the device includes a two-channel uplink path, a two-channel downlink path, a serial port, and a parallel port. The uplink path performs Gaussian minimum shift keying (GMSK) modulation, D/A conversion, and has smoothing filters to provide the external RF circuit with I and Q baseband signals. The downlink path performs antialiasing, analog/digital (A/D) conversion, and channel separation filtering of the baseband I and Q signals. The serial port allows baseband data exchange with the DSP, and the parallel port controls precise timing signals.

Auxiliary RF functions such as automatic frequency control (AFC), automatic gain control (AGC), power control, and analog monitoring are also implemented in the TCM4400. Internal functional blocks of the device can be separately and automatically powered down with GSM RF windows.

#### 1.1 Features

- Applications Include GSM 900, DCS 1800, and PCS 1900 Cellular Telephones

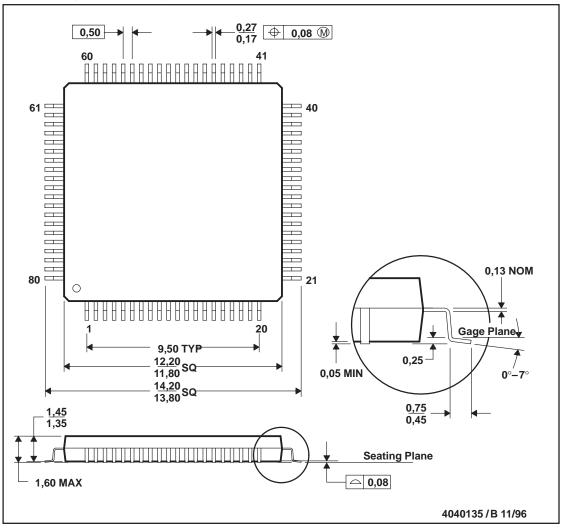

- 80-Pin TQFP Package

- Single 3-V Supply Voltage

- Internal Voltage Reference

- Extended RF Control Voltages

- Advanced Power Management

- GSM-Digital Audio Interface (DAI)

- MCU and DSP Serial Interface

- Five-Port Auxiliary A/D

- Meets JTAG Testability Standard (IEEE Std 1131.1-1990)

- Baseband Codec-GMSK Modulator with On-Chip Burst Buffer

- Voice Codec Features: Microphone Amplifier and Bias Source, Programmable Gain Amplifiers,

Volume Control, and Sidetone Control

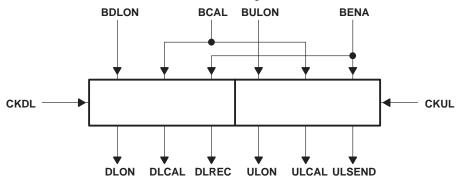

## 1.2 Functional Block Diagram

## 1.3 Terminal Assignments

## 80-PIN TQFP PACKAGE (TOP VIEW)

## 1.4 Terminal Functions

| 1.4 Terminal Functions |      |     |                                                                                                      |  |  |

|------------------------|------|-----|------------------------------------------------------------------------------------------------------|--|--|

| TERM                   | INAL | 1/0 | DESCRIPTION                                                                                          |  |  |

| NAME                   | NO.  |     | DEGGINI HON                                                                                          |  |  |

| ADCMID                 | 44   | I/O | Reference voltage of auxiliary A/D converters; decoupling only (analog)                              |  |  |

| ADIN1                  | 36   | - 1 | Auxiliary 10-bit ADC input 1 (analog)                                                                |  |  |

| ADIN2                  | 37   | - 1 | Auxiliary 10-bit ADC input 2 (analog)                                                                |  |  |

| ADIN3                  | 38   | I   | Auxiliary 10-bit ADC input 3 (analog)                                                                |  |  |

| ADIN4                  | 39   | I   | Auxiliary 10-bit ADC input 4 (analog)                                                                |  |  |

| ADIN5                  | 40   | I   | Auxiliary 10-bit ADC input 5 (analog)                                                                |  |  |

| AFC                    | 46   | 0   | Automatic frequency control DAC output (analog)                                                      |  |  |

| AGC                    | 45   | 0   | Automatic gain control DAC output (analog)                                                           |  |  |

| APC                    | 47   | 0   | Automatic power control DAC output (analog)                                                          |  |  |

| AUXI                   | 29   | ı   | Auxiliary (high-level) speech signal input (analog)                                                  |  |  |

| AUXO                   | 34   | 0   | Auxiliary downlink (voice codec) amplifier output – single-ended (analog)                            |  |  |

| AV <sub>DD1</sub>      | 7    |     | Analog positive power supply (band gap, internal common-mode generator, bias current generator)      |  |  |

| AV <sub>DD2</sub>      | 56   |     | Analog positive power supply (baseband codec)                                                        |  |  |

| AV <sub>DD3</sub>      | 41   |     | Analog positive power supply (auxiliary RF functions)                                                |  |  |

| AV <sub>DD3/5</sub>    | 43   |     | Analog positive power supply (auxiliary RF functions) – can be in the 3-V to 5-V range               |  |  |

| AV <sub>DD4</sub>      | 30   |     | Analog positive power supply (voice codec)                                                           |  |  |

| AVSS1                  | 11   |     | Analog negative power supply (band gap, internal common-mode generator, bias current generator)      |  |  |

| AVSS2                  | 55   |     | Analog negative power supply (baseband codec)                                                        |  |  |

| AV <sub>SS3</sub>      | 48   |     | Analog negative power supply (auxiliary RF functions)                                                |  |  |

| AV <sub>SS4</sub>      | 31   |     | Analog negative power supply (voice codec)                                                           |  |  |

| BCAL                   | 72   | 1   | Baseband uplink or downlink offset calibration enable (timing interface)                             |  |  |

| BCLKR                  | 5    | I/O | DSP serial interface clock input. This clock signal is provided by the DSP or the TCM4400 (digital). |  |  |

| BCLKX                  | 2    | 0   | DSP serial interface clock output. The frequency is the same as MCLK (digital/3-state).              |  |  |

| BDR                    | 4    | ı   | DSP serial interface serial data input (digital)                                                     |  |  |

| BDX                    | 3    | 0   | DSP serial interface serial data output (digital/3-state)                                            |  |  |

| BENA                   | 71   | ı   | Burst transmit or receive enable (depends on status of BULON and BDLON) (digital)                    |  |  |

| BDLON                  | 74   | ı   | Power on of baseband downlink (timing interface)                                                     |  |  |

| BFSR                   | 6    | 1   | DSP serial interface receive frame synchronization input (digital)                                   |  |  |

| BFSX                   | 1    | 0   | DSP serial interface transmit frame synchronization output (digital/3-state)                         |  |  |

| BDLIN                  | 54   | ı   | In-phase baseband input (–) – downlink path (analog)                                                 |  |  |

| BDLIP                  | 53   | ı   | In-phase baseband input (+) – downlink path (analog)                                                 |  |  |

| BDLQN                  | 52   | 1   | Quadrature baseband input (-) - downlink path (analog)                                               |  |  |

| BDLQP                  | 51   | ı   | Quadrature baseband input (+) – downlink path (analog)                                               |  |  |

| BULIN                  | 59   | 0   | In-phase baseband output (–) – uplink path (analog)                                                  |  |  |

| BULIP                  | 60   | 0   | In-phase baseband output (+) – uplink path (analog)                                                  |  |  |

| BULON                  | 73   | ı   | Serial clock input (serial interface) (digital)                                                      |  |  |

| BULQN                  | 57   | 0   | Quadrature baseband output (–) – uplink path (analog)                                                |  |  |

| BULQP                  | 58   | 0   | Quadrature baseband output (+) – uplink path (analog)                                                |  |  |

| DV <sub>DD1</sub>      | 80   |     | Digital positive power supply (baseband and timing serial interfaces)                                |  |  |

| DV <sub>DD2</sub>      | 66   |     | Digital positive power supply (baseband codec)                                                       |  |  |

| DV <sub>DD3</sub>      | 42   |     | Digital positive power supply (auxiliary RF functions)                                               |  |  |

| DV <sub>DD4</sub>      | 21   |     | Digital positive power supply (voice band codec and serial interface)                                |  |  |

## 1.4 Terminal Functions (continued)

| TERMIN            |     |     | nctions (continued)                                                                                                              |

|-------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO. | 1/0 | DESCRIPTION                                                                                                                      |

| DV <sub>SS1</sub> | 79  |     | Digital negative power supply (baseband and timing serial interfaces)                                                            |

| DV <sub>SS2</sub> | 65  |     | Digital negative power supply (baseband codec)                                                                                   |

| DV <sub>SS3</sub> | 49  |     | Digital negative power supply (auxiliary RF functions)                                                                           |

| DV <sub>SS4</sub> | 22  |     | Digital negative power supply (voice band codec and serial interface)                                                            |

| EARN              | 33  | 0   | Earphone amplifier output (–) (analog)                                                                                           |

| EARP              | 32  | 0   | Earphone amplifier output (+) (analog)                                                                                           |

| GNDA1             | 25  |     | Analog signal ground for the microphone amplifier and auxiliary input                                                            |

| GNDA2             | 35  |     | Signal return (ground) for AUXO output                                                                                           |

| IBIAS             | 9   | I/O | Internal bias reference current adjust – adjust with external resistor (analog)                                                  |

| MCLK              | 70  | I   | Master system clock input (13 MHz )                                                                                              |

| MICBIAS           | 26  | Ι   | Microphone bias supply output – also used to decouple bias supply with external capacitor (analog)                               |

| MICIP             | 27  | Ι   | Microphone amplifier input (+) (analog)                                                                                          |

| MICIN             | 28  | Ι   | Microphone amplifier input (-) (analog)                                                                                          |

| PWRDN             | 23  | ı   | Power-down mode control input (digital) – active high                                                                            |

| RESET             | 12  | ı   | Device global hardware reset (digital) – active low                                                                              |

| SSCLK             | 20  | 0   | DAI external 104-kHz clock output (digital)                                                                                      |

| SSDR              | 19  | ı   | DAI data transfer input – connect to GSM-SS TDAI (digital/pullup)                                                                |

| SSDX              | 18  | 0   | DAI data transfer output – connect to GSM-SS RDAI (digital)                                                                      |

| SSRST             | 17  | ı   | DAI reset input (digital/pullup)                                                                                                 |

| TCK               | 64  | ı   | Scan test clock (digital/pulldown)                                                                                               |

| TDI               | 63  | ı   | Scan path input (for testing purposes) (digital/pullup)                                                                          |

| TDO               | 62  | ı   | Scan path output (for testing purposes) (digital/3-state)                                                                        |

| TEST1             | 69  | I/O | Test I/O (digital/3-state and pullup)                                                                                            |

| TEST2             | 68  | I/O | Test I/O (digital/3-state and pullup)                                                                                            |

| TEST3             | 67  | 0   | Test output (digital)                                                                                                            |

| TMS               | 61  | ı   | JTAG test mode select (digital/pullup)                                                                                           |

| TRST              | 24  | Ι   | JTAG serial interface and boundary-scan register reset (digital/pullup) – active low                                             |

| UCLK              | 78  | Ι   | Microcontroller unit (MCU) interface clock input (digital)                                                                       |

| UDR               | 77  | I   | MCU interface data transfer input (digital)                                                                                      |

| UDX               | 76  | 0   | MCU interface data transfer output (digital/3-state)                                                                             |

| USEL              | 75  | Ι   | MCU serial interface select (digital)                                                                                            |

| VCLK              | 16  | 0   | Voice band serial interface clock output (digital/3-state)                                                                       |

| VDR               | 15  | I   | Voice band serial interface receive data input (digital)                                                                         |

| VDX               | 14  | 0   | Voice band serial interface transmit data output (digital/3-state)                                                               |

| VFS               | 13  | 0   | Voice band serial interface transmit frame synchronization output (digital/3-state)                                              |

| VGAP              | 10  | I/O | Band gap reference voltage – decouple with external capacitor (analog)                                                           |

| VMID              | 50  | 0   | Baseband uplink midrail voltage output – serves as reference common-mode voltage for RF device when directly dc coupled (analog) |

| V <sub>REF</sub>  | 8   | I/O | Reference voltage – decouple with external capacitor (analog)                                                                    |

## 2 Electrical Specifications

# 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (Unless Otherwise Noted)†

| Supply voltage range, AV <sub>DD</sub> , DV <sub>DD</sub> (see Note 1)  | . $-0.3$ to 6 V    |

|-------------------------------------------------------------------------|--------------------|

| Maximum voltage on any input, V <sub>I</sub> max V <sub>DD</sub> +0.3 \ | $I/V_{SS} - 0.3 V$ |

| Storage temperature, T <sub>stq</sub> –                                 | 65°C to 150°C      |

| Maximum junction temperature, T <sub>1</sub>                            | 150°C              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage measurements in respect to GND

## 2.2 Recommended Operating Conditions

|                                                                                 | MIN  | NOM | MAX                    | UNIT |

|---------------------------------------------------------------------------------|------|-----|------------------------|------|

| Supply voltage range (AV <sub>DD</sub> , DV <sub>DD</sub> )                     | 2.7  | 3.0 | 3.3                    | Vdc  |

| Supply extended voltage range for RF blocks (AVDD3/5) – 3-V supply              | 2.7  | 3.0 | 3.3                    | Vdc  |

| Supply extended voltage range for RF blocks (AV <sub>DD</sub> 3/5) – 5-V supply | 4.75 | 5.0 | 5.25                   | Vdc  |

| Operating temperature range                                                     | -25  |     | 85                     | °C   |

| Digital I/O voltage with respect to DVSS                                        | -0.3 |     | DV <sub>DD</sub> + 0.3 | Vdc  |

| Analog I/O voltage with respect to AVSS                                         | -0.3 |     | $AV_{DD} + 0.3$        | V    |

| Difference between any AV <sub>DD</sub> or DV <sub>DD</sub>                     |      |     | 0.3                    | V    |

# 2.3 Electrical Characteristics Over Recommended Operating Free-Air Temperature Range (Unless Otherwise Noted)

### 2.3.1 Digital Inputs And Outputs

| PARAMETER                                                                             | MIN                  | TYP MAX              | UNIT |

|---------------------------------------------------------------------------------------|----------------------|----------------------|------|

| Low-level output current with digital pad lower than 0.1 V (CMOS)                     | 0                    | 40                   | μΑ   |

| Low-level output current with digital pad lower than 0.4 V (TTL)                      | 0                    | 1                    | mA   |

| High-level output current with digital pad higher than $V_{\mbox{DD}}$ = 0.1 V (CMOS) | -40                  | 0                    | μΑ   |

| High-level output current with digital pad higher than V <sub>DD</sub> = 0.4 V (TTL)  | -1                   | 0                    | mA   |

| Minimum high-level input voltage, VIH                                                 | V <sub>DD</sub> -0.3 |                      | V    |

| Maximum low-level input voltage, V <sub>IL</sub>                                      |                      | V <sub>SS</sub> +0.3 | V    |

| Output current on high-impedance state outputs                                        | -15                  | +15                  | μΑ   |

| Input current (any input) when input high                                             | -1                   |                      | μΑ   |

| Input current (standard inputs) when input low                                        |                      | 1                    | μΑ   |

| Input current (inputs with pullup TMS, TDI, TEST1, TEST2) when input low              |                      | 15                   | μΑ   |

## 2.3.2 Voltage References

|         | REFERENCE                                                                       | MIN  | TYP                | MAX  | UNIT |

|---------|---------------------------------------------------------------------------------|------|--------------------|------|------|

| VGAP    | Voltage on band gap (used for all other references)                             | 1.16 | 1.22               | 1.28 | Vdc  |

|         | Band gap output resistance                                                      |      | 200                |      | kΩ   |

|         | Band gap external decoupling capacitance                                        |      | 0.1                |      | μF   |

|         | Band gap start time (bit CHGUP = 0)                                             |      | 100                |      | ms   |

|         | Band gap start time (bit CHGUP = 1)                                             |      | 2.5                |      | ms   |

| VREF    | Voltage reference of GMSK internal ADC and DAC: VVREF                           | 1.66 | 1.75               | 1.84 | Vdc  |

|         | Voltage reference output resistance                                             |      | 200                |      | kΩ   |

|         | Voltage reference external decoupling capacitance                               |      | 0.1                |      | μF   |

|         | Voltage reference start time (bit CHGUP = 0)                                    |      | 300                |      | ms   |

|         | Voltage reference start time (bit CHGUP = 1)                                    |      | 10                 |      | ms   |

| VMID    | Common-mode reference for baseband uplink: $V_{VMID}$ (bit SELV-MID = 0)        | -10% | V <sub>DD</sub> /2 | 10%  | Vdc  |

|         | Common-mode reference for baseband uplink: V <sub>VMID</sub> (bit SELV-MID = 1) | 1.25 | 1.35               | 1.45 | Vdc  |

|         | Load resistance on VMID output                                                  | 10   |                    |      | kΩ   |

| MICBIAS | Microphone-driving voltage (bit MICBIAS = 0)                                    | 1.80 | 2                  | 2.20 | Vdc  |

|         | Microphone-driving voltage (bit MICBIAS = 1)                                    | 2.25 | 2.5                | 2.75 | Vdc  |

|         | Microphone-bias current drive capability (bit MICBIAS = 1)                      | 450  | 500                |      | μΑ   |

|         | Microphone-bias current drive capability (bit MICBIAS = 0)                      | 350  | 400                |      | μΑ   |

| ADCMID  | DC bias reference of the auxiliary ADCs                                         | -10% | V <sub>DD</sub> /2 | 10%  | Vdc  |

|         | ADCMID external decoupling capacitance                                          |      | 0.1                |      | μF   |

| IBIAS   | Bias current adjust external resistance                                         |      | 100                |      | kΩ   |

## 2.3.3 Master Clock Input (MCLK)

|                                              | MIN                  | NOM | MAX                  | UNIT |

|----------------------------------------------|----------------------|-----|----------------------|------|

| Master clock signal frequency                |                      | 13  |                      | MHz  |

| Master clock duty cycle (sine wave)          | 40                   |     | 60                   | %    |

| Maximum peak-to-peak amplitude               |                      |     | 1.3                  | Vpp  |

| Minimum peak-to-peak amplitude               | 0.5                  |     |                      | Vpp  |

| Common-mode input voltage                    | V <sub>SS</sub> +0.5 |     | V <sub>DD</sub> -0.5 | Vdc  |

| Input resistance at 13 MHz (MCLK to ground)  | 4.1                  | 5   | 6.5                  | kΩ   |

| Input capacitance at 13 MHz (MCLK to ground) | 12.5                 | 15  | 18                   | pF   |

2.3.4 Baseband Uplink Path

| PARAMETER                             | TEST CONDITIONS               | MIN        | TYP                 | MAX | UNIT |

|---------------------------------------|-------------------------------|------------|---------------------|-----|------|

| I and Q DAC resolution                |                               |            | 8                   |     | bit  |

| Dynamic range on each output          | Centered on V <sub>VMID</sub> |            | VVREF               |     | Vpp  |

| Differential output dynamic range†    | BULQP-BULQN or BULIP-BULIN    |            | 2×V <sub>VREF</sub> |     | Vpp  |

| Output load resistance, differential  |                               | 10         |                     |     | kΩ   |

| Output load capacitance, differential |                               | 50         |                     |     | pF   |

| Output common-mode voltage            | Programmable by bit SELVMID   | $V_{VMID}$ |                     | V   |      |

| I and Q output state in power down    |                               |            | HiZ                 |     | _    |

<sup>†</sup> Initial values after reset and at beginning of each burst are BULIP–BULIN=V<sub>REF</sub> and BULQP–BULQN=0 corresponding to a phase angle of 0°.

2.3.5 dc Accuracy – Baseband Uplink Path

| PARAMETER                       | MIN  | TYP | MAX | UNIT |

|---------------------------------|------|-----|-----|------|

| Offset error before calibration | -90  | 0   | 90  | mV   |

| Offset error after calibration  | -5   | 0   | 5   | mV   |

| Offset correction range         | -100 | 0   | 100 | mV   |

2.3.6 Dynamic Parameters – Baseband Uplink Path

| PARAMETER                                                              | TEST CONDITIONS                  | MIN | TYP | MAX  | UNIT |

|------------------------------------------------------------------------|----------------------------------|-----|-----|------|------|

| Absolute gain error relative to VVREF                                  | Measured with 67.7-kHz sine wave | -1  | 0   | 1    | dB   |

| Maximum output random modulation spectrum relative to in-band average  | 100 kHz                          |     |     | -3   | dB   |

|                                                                        | 200 kHz                          |     |     | - 34 | dB   |

| level. Measured by average fast Fourier                                | 250 kHz                          |     |     | - 37 | dB   |

| transforms (FFTs) of random bursts using a flat top window with 30-kHz | 400 kHz                          |     |     | - 65 | dB   |

| bandwidth.                                                             | 600 kHz                          |     |     | -72  | dB   |

|                                                                        | 800 kHz                          |     |     | -72  | dB   |

<sup>‡</sup> Flat top window is defined as:  $Dw(i)=D(i)\times wf0\times (wf1+wf2\times cos\ (2\times i\times \Pi/n)+wf3\times cos\ (4\times i\times \Pi/n))$ . With wf0=2.0660373, wf1=0.2810639, wf2=-0.5208972, wf3=0.1980399.

2.3.7 Smoothing Filters Characteristics – Baseband Uplink Path

| PARAMETER   | TEST CONDITIONS MIN TY |  | TYP | MAX | UNIT |

|-------------|------------------------|--|-----|-----|------|

| Group delay | 0 Hz to 100 kHz        |  | 1.5 |     | μs   |

2.3.8 I and Q Channels Gain and Phase Matching – Baseband Uplink Path

| PARAMETER                       |                | TEST CONDITIONS                                   | MIN   | TYP   | MAX   | UNIT |

|---------------------------------|----------------|---------------------------------------------------|-------|-------|-------|------|

| Gain matching between channels  | 0 Hz to 96 kHz | Measured on 67.7 kHz sine wave before calibration | -1    | 0     | 1     | dB   |

|                                 | 0 HZ 10 90 KHZ | Measured on 67.7 kHz sine wave after calibration  | -0.3  | 0     | 0.3   | αБ   |

| Phase matching between channels | 0 Hz to 96 kHz |                                                   | -0.5° | 0     | 0.5°  |      |

|                                 | -              |                                                   | -0.15 | 0.0   | 0.15  |      |

| I and Q gain imbalance          |                | Programmable with bits IQSEL,                     | -0.42 | -0.27 | -0.12 | dB   |

| rand Q gain imbalance           |                | G1, and G0                                        | -0.68 | -0.53 | -0.38 | ub   |

|                                 |                |                                                   | -0.93 | -0.78 | -0.63 |      |

2.3.9 Baseband Uplink Path Global Characteristics

| PARAMETER                   | MIN | TYP | MAX  | UNIT |

|-----------------------------|-----|-----|------|------|

| GMSK phase trajectory error |     |     | 6°   | peak |

|                             |     |     | 1.5° | rms  |

| Power supply rejection      | 46  |     |      | dB   |

### 2.4 Timing Requirements of Baseband Uplink Path

2.4.1 Programmable Delays – Baseband Uplink Path (See Figure 3–1)

|                                                      |                                    |                                | MIN | NOM  | MAX | UNIT†    |

|------------------------------------------------------|------------------------------------|--------------------------------|-----|------|-----|----------|

| t <sub>su1</sub>                                     | Setup time, BENA↑ before APC↑      | Bits DELU of register BULRUDEL | 0   |      | 15  | 1/4-bit  |

| t <sub>h1</sub>                                      | Hold time, ramp-down from BENA low | Bits DELD of register BULRUDEL | 0   |      | 15  | 1/4-bit  |

|                                                      | Transition time ABC                | Bit APCSPD = 0                 | 0   | 0 04 | 64  | 1/16-bit |

| t <sub>r</sub> , t <sub>f</sub> Transition time, APC | Transition time, APC               | Bit APCSPD = 1                 | U   |      | 04  | 1/8-bit  |

2.4.2 Fixed Delays – Baseband Uplink Path (See Figure 3–1)

|                  |                                          |                                                  | MIN | NOM  | MAX | UNIT†   |

|------------------|------------------------------------------|--------------------------------------------------|-----|------|-----|---------|

| t <sub>su2</sub> | Setup time, BULON↑ to BCAL↑              |                                                  | 15  |      |     | μs      |

| t <sub>w1</sub>  | Pulse duration, BCAL high                |                                                  | 132 |      |     | μs      |

| t <sub>su3</sub> | Setup time, BCAL low before BENA↑        |                                                  | 0   |      |     | μs      |

| t <sub>w2</sub>  | Pulse duration, BENA high                | N effective duration of burst controlled by BENA |     | N-32 |     | 1/4-bit |

| <sup>t</sup> h2  | Hold time, modulation low after BENA low |                                                  |     | 32   |     | bit     |

| t <sub>h3</sub>  | Hold time, BULON↓ after APC low          |                                                  | 1   |      |     | bit     |

| tdd(mod)         | Input-to-output modulator delay          | Digital delay of modulator                       |     | 1.5  |     | bit     |

<sup>†</sup> Bit is relative to GSM bit = 1/270 kHz. Units can be a fractional part of the GSM bit as noted. Values in the above table are given for system information only.

#### 2.4.3 Baseband Downlink Path

| PARAMETER                                                                    | TEST CONDITIONS                                      | MIN | TYP                 | MAX                  | UNIT |

|------------------------------------------------------------------------------|------------------------------------------------------|-----|---------------------|----------------------|------|

| Dynamic range on each input                                                  | Centered on external common mode (VBDLCOM)           |     | V <sub>VREF</sub>   |                      | Vpp  |

| Differential input dynamic range                                             | DLQP-DLQN or DLIP-DLIN                               |     | 2×V <sub>VREF</sub> |                      | Vpp  |

| Differential input resistance at BDLQP-BDLQN or BDLIP-BDLIN                  |                                                      | 130 | 200                 | 270                  | kΩ   |

| Differential input capacitance at BDLQP-BDLQN or BDLIP-BDLIN                 |                                                      | 1.5 | 4                   | 6.5                  | pF   |

| Single-ended input resistance at BDLQP or BDLQN or BDLIP or BDLIN to ground  |                                                      | 90  | 130                 | 180                  | kΩ   |

| Single-ended input capacitance at BDLQP or BDLQN or BDLIP or BDLIN to ground |                                                      | 6   | 8                   | 12                   | pF   |

| External common-mode input voltage: VBDLCOM                                  |                                                      | 0.8 | V <sub>DD</sub> /2  | V <sub>DD</sub> -0.8 | V    |

| Range of digital output data                                                 | Maximum digital code value on 16-bit I and Q samples |     | ± 21060             |                      |      |

2.4.4 dc Accuracy – Baseband Downlink Path

| PARAMETER                                    | TEST CONDITIONS              | MIN | TYP        | MAX | UNIT |

|----------------------------------------------|------------------------------|-----|------------|-----|------|

| Offset error before calibration <sup>†</sup> |                              | -60 | 0          | 60  | LSB  |

| Offset error after calibration               | ±21 on 16-bit I and Q words† | -2  | 0          | 2   | LSB  |

| Offset correction range                      |                              |     | full scale |     |      |

The LSB corresponds to the one of the ADC which is specified with 66-dB dynamic range (±1024), which means 11-bit, but the output data bits are transmitted through the serial interface with 16-bit words. The decimation ratio of 24 (6.5 MHz/270 kHz) makes the maximum code on a 16-bit word 21060 instead of 32767. Therefore, one LSB of the ADC corresponds to a value of 21060/1024 = 20.57 on the 16-bit output serial words on I and Q.

### 2.5 Channel Characteristics

#### 2.5.1 Frequency Response – Baseband Downlink Path

| PARAMETER                                        |          | MIN  | TYP MAX | UNIT |

|--------------------------------------------------|----------|------|---------|------|

| Frequency response of the total path with values | < 0 Hz   | -0.2 | 0.2     |      |

|                                                  | 67.5 kHz | -0.3 | 0.25    | 1    |

|                                                  | 96 kHz   | -4   | 0.3     | dB   |

| referenced to 18 kHz                             | 135 kHz  |      | -40     | l ub |

|                                                  | 200 kHz  |      | -40     | 1    |

|                                                  | 400 kHz  |      | -40     |      |

### 2.5.2 SNR vs Signal Level-baseband Downlink Path

| PARAMETER                       |          | TEST CONDITIONS   | MIN | TYP | MAX | UNIT |

|---------------------------------|----------|-------------------|-----|-----|-----|------|

|                                 | -45 dBm0 | 200-kHz bandwidth | 21  |     |     |      |

|                                 | -40 dBm0 |                   | 26  |     |     |      |

|                                 | -30 dBm0 |                   | 36  |     |     |      |

| Signal level                    | -20 dBm0 |                   | 46  |     |     | dB   |

|                                 | -10 dBm0 |                   | 50  |     |     |      |

|                                 | -3 dBm0  |                   | 57  |     |     |      |

|                                 | 0 dBm0   |                   | 30  |     |     |      |

| Idle channel noise, 0 Hz-200 kH | Z        |                   |     |     | -66 | dBm0 |

#### 2.5.3 Gain Characteristics of the Baseband Downlink Path

| PARAMETER                                                                       |          | TEST CONDITIONS           | MIN   | TYP | MAX  | UNIT |

|---------------------------------------------------------------------------------|----------|---------------------------|-------|-----|------|------|

| Absolute gain error relative to V <sub>VREF</sub>                               |          | at –10 dBm0 and<br>18 kHz | -11   | -10 | -9   | dB   |

|                                                                                 | 3 dBm0   |                           | -0.25 |     | 0.25 |      |

|                                                                                 | 0 dBm0   |                           | -0.25 |     | 0.25 |      |

|                                                                                 | - 5 dBm0 |                           | -0.25 |     | 0.25 |      |

| Gain tracking error over the range 3 dBm0 to – 50 dBm0 at 18 kHz with reference | -10 dBm0 | Reference level           | -0.25 |     | 0.25 | dB   |

| -10 dBm0                                                                        | -20 dBm0 |                           | -0.25 |     | 0.25 | uБ   |

|                                                                                 | -30 dBm0 |                           | -0.25 |     | 0.25 |      |

|                                                                                 | -40 dBm0 |                           | -0.25 |     | 0.25 |      |

|                                                                                 | -50 dBm0 |                           | -0.50 |     | 0.50 |      |

### 2.5.4 Group Delay – Baseband Downlink Path

| PARAMETER   |                 | MIN | TYP | MAX | UNIT |

|-------------|-----------------|-----|-----|-----|------|

| Group delay | 0 Hz to 100 kHz |     | 28  |     | μs   |

2.5.5 I and Q Channels Matching – Baseband Downlink Path

| PARAMETER                       |                | TEST CONDITIONS  | MIN        | TYP | MAX | UNIT |

|---------------------------------|----------------|------------------|------------|-----|-----|------|

| Gain matching between channels  | 0 Hz to 96 kHz | 18-kHz sine wave | -0.5       |     | 0.5 | dB   |

| Delay matching between channels | 0 Hz to 96 kHz | 18-kHz sine wave | <b>-</b> 5 |     | 5   | ns   |

#### 2.5.6 Baseband Downlink Path Global Characteristics

| PARAMETER                                  | MIN | TYP | MAX | UNIT |

|--------------------------------------------|-----|-----|-----|------|

| Power supply rejection, 0 Hz –100 kHz band | 60  |     |     | dB   |

2.6 Timing Requirements of Baseband Downlink Path (See Figure 3–2)

|                  |                                                    |                                                  | MIN  | NOM | MAX | UNIT <sup>†</sup> |

|------------------|----------------------------------------------------|--------------------------------------------------|------|-----|-----|-------------------|

| t <sub>su4</sub> | t <sub>Su4</sub> Setup time, BDLON↑ to BCAL↑       |                                                  | 5    |     |     | μs                |

| t <sub>w3</sub>  | Pulse duration, BCAL                               |                                                  | 60   |     |     | μs                |

| t <sub>su5</sub> | t <sub>Su5</sub> Setup time BCAL low before BENA↑  |                                                  | 0    |     |     | μs                |

| t <sub>W4</sub>  | Pulse duration, BENA high                          | N effective duration of burst controlled by BENA |      | N   |     | 1/4-bit           |

| t <sub>su6</sub> | Setup time, BENA <sup>↑</sup> before DATAOUT valid |                                                  | 24.3 |     | 28  | μs                |

| t <sub>h4</sub>  | Hold time, DATAOUT valid after BENA $\downarrow$   |                                                  |      |     | 3.7 | μs                |

| t <sub>h5</sub>  | Hold time, BDLON low after BENA low                |                                                  | 0    |     |     | μs                |

<sup>†</sup> Value given is for system information only.

## 2.7 Automatic Power Control (APC)

## 2.7.1 APC Level (8-bit DAC)

| PARAMETER                            | TEST CONDITIONS              | MIN | TYP | MAX | UNIT |

|--------------------------------------|------------------------------|-----|-----|-----|------|

| Integral nonlinearity (best fitting) | Shaper at maximum            | -1  |     | 1   | LSB  |

| Differential nonlinearity            | full-scale load 10 kΩ, 50 pF | -1  |     | 1   | LSB  |

| Settling time                        |                              |     |     | 10  | μs   |

#### 2.7.2 APC Shaper (5-bit DAC)

| PARAMETER                            | MIN | TYP | MAX | UNIT |

|--------------------------------------|-----|-----|-----|------|

| Integral nonlinearity (best fitting) | -1  |     | 1   | LSB  |

| Differential nonlinearity            | -1  |     | 1   | LSB  |

| Settling time <sup>†</sup>           |     |     | 1   | μs   |

<sup>†</sup> Value given is for system information only.

2.7.3 APC Output Stage

| PARAMETER                                                                           | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------------------------|---------------------------------|-----|-----|-----|------|

| Output voltage at shape = 3 and level = 255 (AV <sub>DD3</sub> /5 = 3 V)            | Bit APCSWG = 0                  | 2   | 2.2 | 2.4 | V    |

| Output voltage at shape = 31 and level = 255 (AV <sub>DD3/5</sub> = 5 V)            | Bit APCSWG = 1                  | 4   | 4.4 | 4.8 | V    |

| Output voltage at shape = 0 and level = xx (AV <sub>DD3</sub> /5 = 3 V)             | Bit APCSWG = 0, Bit APCMODE = 0 | 0   |     | 15  | mV   |

| Output voltage at shape = 0 and level = xx (AV <sub>DD3/5</sub> = 5 V)              | Bit APCSWG = 1, Bit APCMODE = 0 | 0   |     | 30  | mV   |

| Ouptut voltage at shape = 0 and level = xx (AV <sub>DD3/5</sub> = 3 V) <sup>†</sup> | Bit APCSWG = 0, Bit APCMODE = 1 | 80  | 120 | 160 | mV   |

| Output voltage at shape = 0 and level = xx (AV <sub>DD3/5</sub> = 5 V) <sup>†</sup> | Bit APCSWG = 1, Bit APCMODE = 1 | 160 | 240 | 320 | mV   |

| Output voltage at shape = xx and level = 0                                          |                                 |     | 0   | 5   | mV   |

| Output voltage in power down                                                        |                                 |     | 0   |     | V    |

| DC power supply sensitivity                                                         |                                 |     |     | 1   | %    |

| Output impedance in power down                                                      |                                 |     | 20  |     | Ω    |

| Load resistance                                                                     |                                 | 10  |     |     | kΩ   |

| Load capacitance                                                                    |                                 |     |     | 50  | pF   |

<sup>†</sup> Temperature variations of these voltages are  $\pm 1\%$  from  $-50^{\circ}$ C to  $+100^{\circ}$ C and  $\pm 0.6\%$  from  $0^{\circ}$ C to  $70^{\circ}$ C.

## 2.8 Monitoring ADC

### 2.8.1 10-bit ADC

| 21011 10 511 7150                    |                                 |     |         |      |

|--------------------------------------|---------------------------------|-----|---------|------|

| PARAMETER                            | TEST CONDITIONS                 | MIN | TYP MAX | UNIT |

| Integral nonlinearity (best fitting) | Input signal range < 0.95 VVREF | -4  | 4       | LSB  |

| Differential nonlinearity            | Input signal range < 0.95 VVREF | -2  | 2       | LSB  |

| Conversion time‡                     |                                 |     | 10      | μs   |

| Input range                          |                                 | 0   | VVREF   | V    |

| Input leakage current                |                                 | -10 | 10      | μΑ   |

| Input capacitance                    |                                 |     | 25      | pF   |

<sup>‡</sup> Value given is for system information only.

## 2.9 Automatic Gain Control (AGC)

## 2.9.1 AGC 10-bit DAC

| PARAMETER TEST CONDITIONS |                   | MIN | TYP | MAX | UNIT |

|---------------------------|-------------------|-----|-----|-----|------|

| Integral nonlinearity     | Best fitting line | -1  |     | 1   | LSB  |

| Differential nonlinearity |                   | -1  |     | 1   | LSB  |

| Settling time             | From AUXAGC load  |     |     | 100 | μs   |

2.9.2 AGC Output Stage

| PARAME                       | TER                           | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|------------------------------|-------------------------------|-----------------|------|------|------|------|

| Output voltage with code max | $(AV_{DD3}/5 = 3 V \pm 10\%)$ | Bit AGCSWG = 0  | 2    | 2.2  | 2.4  | V    |

| Offset voltage with code 000 | $(AV_{DD3/5} = 3 V \pm 10\%)$ | Bit AGCSWG = 0  | 0.18 | 0.24 | 0.30 | V    |

| Output swing with code max   | $(AV_{DD3/5} = 5 V \pm 5\%)$  | Bit AGCSWG = 1  | 4    | 4.4  | 4.8  | V    |

| Offset voltage with code 000 | $(AV_{DD3/5} = 5 V \pm 5\%)$  | Bit AGCSWG = 1  | 0.36 | 0.48 | 0.60 | V    |

| Output voltage in power down | l                             |                 |      | 0    |      | V    |

| DC power supply sensitivity  |                               |                 |      |      | 1    | %    |

| Output impedance in power de | own                           |                 |      | 200  |      | kΩ   |

| Load resistance              |                               |                 | 10   |      |      | kΩ   |

| Load capacitance             |                               |                 |      |      | 50   | pF   |

## 2.10 Automatic Frequency Control (AFC)

## 2.10.1 AFC 13-bit DAC

| PARAMETER                                            | PARAMETER TEST CONDITIONS                                                    |  | TYP  | MAX | UNIT |

|------------------------------------------------------|------------------------------------------------------------------------------|--|------|-----|------|

|                                                      | AFCCK1 = 1, AFCCK0 = 1                                                       |  | 2    |     | MHz  |

| Sampling frequency, f <sub>S</sub>                   | AFCCK1 = 1, AFCCK0 = 0                                                       |  | 1    |     | MHz  |

|                                                      | AFCCK1 = 0, AFCCK0 = 1                                                       |  | 0.5  |     | MHz  |

|                                                      | AFCCK1 = 0, AFCCK0 = 0                                                       |  | 0.25 |     | MHz  |

| Integral nonlinearity from 0 to 75% output range     | Best fitting line                                                            |  | ±1   |     | LSB  |

| Differential nonlinearity from 0 to 75% output range |                                                                              |  | ±1   |     | LSB  |

| Settling time                                        |                                                                              |  |      | 1   | μs   |

| DC power-supply sensitivity                          | Over power supply range:<br>at 2.0 V for AFCZ = 0 or<br>at 4.0V for AFCZ = 1 |  |      | 1   | %    |

2.10.2 AFC Output Stage

| PARAMETER                                                 | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------|-------------------------|-----|-----|-----|------|

| Internal output resistance (±30% tolerance)               | Bit AFCZ = 0            |     | 25  |     | kΩ   |

| Internal output resistance (±30% tolerance)               | Bit AFCZ = 1            |     | 50  |     | kΩ   |

| External filtering capacitance                            | Bit AFCZ = 1            |     | 33  |     | nF   |

| Output voltage with code max (AV <sub>DD3/5</sub> = 3 V)  | Bit AFCZ = 0            | 2   | 2.5 | 2.8 | V    |

| Output voltage with code max (AV <sub>DD3/5</sub> = 5 V)  | Bit AFCZ = 1            | 4   | 4.7 | 5.1 | V    |

| Output voltage with code min (AV <sub>DD3/5</sub> = 3 V)  | Bit AFCZ = 0            | 0   | 3   | 6   | mV   |

| Output voltage with code min $(AV_{DD3/5} = 5 \text{ V})$ | Bit AFCZ = 1            | 0   | 5   | 10  | mV   |

| Output voltage in power down                              |                         |     | 0   |     | V    |

| Output impadance in namer dama                            | Bit AFCZ= 0, Bit AFCZ=1 |     | 25  |     | kΩ   |

| Output impedance in power down                            |                         |     | 50  |     | K22  |

## 2.11 Voice Uplink Path

## 2.11.1 Global Characteristics of Voice Uplink Path

| PARAMETER                                     | TEST CONDITIONS                                                                            |        | MIN   | TYP   | MAX   | UNIT  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|

| Maximum input range<br>(MICP – MICN)          | Inputs 3 dBm0 (maximum digital s<br>amplitude) with PGA gain. Set to (<br>(default value). |        |       | 32.5  |       | mVrms |

| Nominal reference level (MICP – MICN)         |                                                                                            |        |       | -10   |       | dBm0  |

| Differential input resistance (MICP – MICN)   |                                                                                            |        | 90    | 140   | 200   | kΩ    |

| Micro amplifier gain                          |                                                                                            |        |       | 27    |       | dB    |

| Maximum input range at AUXI                   | Inputs 3 dBm0 (maximum digital s<br>amplitude) with PGA gain. Set to (<br>(default value). |        |       | 365   |       | mVrms |

| Nominal reference level at AUXI               |                                                                                            |        |       | -10   |       | dBm0  |

| Input resistance at AUXI                      |                                                                                            |        | 140   | 220   | 300   | kΩ    |

| Auxiliary amplifier gain                      |                                                                                            |        |       | 6     |       | dB    |

| PGA absolute gain                             |                                                                                            |        |       | 4.6   |       | dB    |

|                                               | VULPGA code =10000                                                                         | -12 dB | -12.7 | -12.2 | -11.7 |       |

|                                               | VULPGA code = 10111                                                                        | -11 dB | -11.3 | -10.8 | -10.3 |       |

|                                               | VULPGA code = 11000                                                                        | -10 dB | -10.6 | -10.1 | -9.6  |       |

|                                               | VULPGA code = 11001                                                                        | -9 dB  | -9.5  | -9.0  | - 8.5 |       |

|                                               | VULPGA code = 11010                                                                        | – 8 dB | - 8.5 | -8.0  | -7.5  |       |

|                                               | VULPGA code = 11011                                                                        | -7 dB  | -7.5  | -7.0  | - 6.5 |       |

|                                               | VULPGA code = 00000 (default)                                                              | – 6 dB | - 6.7 | -6.2  | - 5.7 |       |

|                                               | VULPGA code = 00001                                                                        | -5 dB  | - 5.6 | - 5.1 | - 4.6 |       |

|                                               | VULPGA code = 00010                                                                        | -4 dB  | - 4.6 | - 4.1 | - 3.6 |       |

|                                               | VULPGA code = 00011                                                                        | -3 dB  | - 3.5 | -3.0  | -2.5  |       |

|                                               | VULPGA code = 00100                                                                        | -2 dB  | -2.4  | -1.9  | -1.4  |       |

|                                               | VULPGA code = 00101                                                                        | -1 dB  | -1.5  | -1.0  | - 0.5 |       |

| PGA gain step                                 | VULPGA code = 00110 (ref)                                                                  | 0 dB   |       | 0     |       | dB    |

|                                               | VULPGA code = 00111                                                                        | 1 dB   | 0.7   | 1.2   | 1.7   |       |

|                                               | VULPGA code = 01000                                                                        | 2 dB   | 1.4   | 1.9   | 2.4   |       |

|                                               | VULPGA code = 01001                                                                        | 3 dB   | 2.6   | 3.1   | 3.6   |       |

|                                               | VULPGA code = 01010                                                                        | 4 dB   | 3.6   | 4.1   | 4.6   |       |

|                                               | VULPGA code = 01011                                                                        | 5 dB   | 4.5   | 5.0   | 5.5   |       |

|                                               | VULPGA code = 01100                                                                        | 6 dB   | 5.3   | 5.8   | 6.3   |       |

|                                               | VULPGA code = 10001                                                                        | 7 dB   | 6.4   | 6.9   | 7.4   |       |

|                                               | VULPGA code = 10010                                                                        | 8 dB   | 7.4   | 7.9   | 8.4   |       |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\       | VULPGA code = 10011                                                                        | 9 dB   | 8.6   | 9.1   | 9.6   |       |

|                                               | VULPGA code = 10100                                                                        | 10 dB  | 9.6   | 10.1  | 10.6  |       |

|                                               | VULPGA code = 10101                                                                        | 11 dB  | 10.5  | 11.0  | 11.5  |       |

|                                               | VULPGA code = 10110                                                                        | 12 dB  | 11.5  | 12.0  | 12.5  |       |

| Power supply rejection,<br>0-Hz –100-kHz band |                                                                                            |        | 52    |       |       | dB    |

2.11.2 Frequency Response of the Voice Band Uplink Path

| PARAMETER                         |           | TEST CONDITIONS            | MIN  | TYP   | MAX | UNIT |

|-----------------------------------|-----------|----------------------------|------|-------|-----|------|

|                                   | 100 Hz    |                            |      | -37.4 | -20 |      |

|                                   | 150 Hz    |                            |      | -25.9 | -15 |      |

|                                   | 200 Hz    |                            |      | -16.5 | -10 |      |

|                                   | 300 Hz    |                            | -2.0 | -1.46 | 1.0 |      |

|                                   | 1000 Hz   | Reference point is 1000 Hz | -1.0 | 0     | 1.0 |      |

| Frequency response (gain relative | 2000 Hz   |                            | -1.0 | -0.58 | 1.0 | dB   |

| to reference gain at 1 kHz)       | 3000 Hz   |                            | -1.0 | -0.77 | 1.0 | uБ   |