## Quad SPST JFET Analog Switch

**SW06**

#### **FEATURES**

Two Normally Open and Two Normally Closed SPST Switches with Disable

Switches Can Be Easily Configured as a Dual SPDT or a DPDT

Highly Resistant to Static Discharge Destruction Higher Resistance to Radiation than Analog Switches Designed with MOS Devices

Guaranteed R<sub>ON</sub> Matching: 10% max Guaranteed Switching Speeds

$T_{ON} = 500 \text{ ns max}$  $T_{OFF} = 400 \text{ ns max}$

Guaranteed Break-Before-Make Switching

Low "ON" Resistance: 80  $\Omega$  max

Low Ron Variation from Analog Input Voltage: 5%

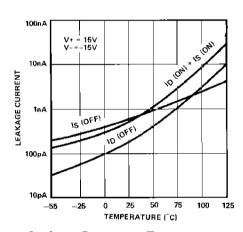

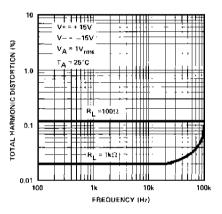

Low Total Harmonic Distortion: 0.01% Low Leakage Currents at High Temperature

$T_A = +125$ °C: 100 n A m ax  $T_A = +85$ °C: 30 n A m ax

Digital Inputs TTL/CM OS Compatible and Independent

Improved Specifications and Pin Compatible to LF-11333/13333

Dual or Single Power Supply Operation

Available in Die Form

#### GENERAL DESCRIPTION

The SW06 is a four channel single-pole, single-throw analog switch that employs both bipolar and ion-implanted FET devices. The SW06 FET switches use bipolar digital logic inputs which are more resistant to static electricity than CMOS devices. Ruggedness and reliability are inherent in the SW06 design and construction technology.

Increased reliability is complemented by excellent electrical specifications. Potential error sources are reduced by minimizing "ON" resistance and controlling leakage currents at high temperatures. The switching FET exhibits minimal  $R_{\rm ON}$  variation over a 20 V analog signal range and with power supply voltage changes. Operation from a single positive power supply voltage is possible. With V+ = 36 V, V- = 0 V, the analog signal range will extend from ground to +32 V.

PNP logic inputs are TTL and CMOS compatible to allow the SW06 to upgrade existing designs. The logic "0" and logic "1" input currents are at microampere levels reducing loading on CMOS and TTL logic.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

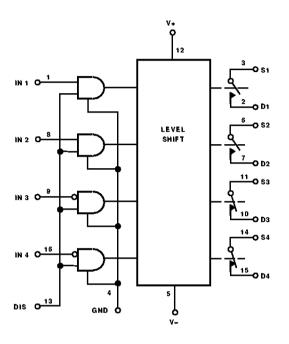

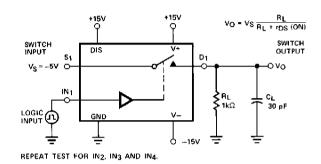

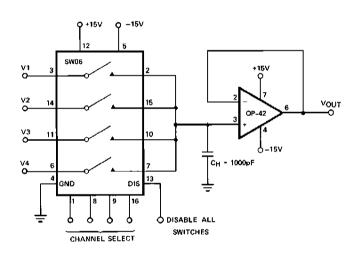

#### FUNCTIONAL BLOCK DIAGRAM

# SW06--SPECIFICATIONS

# ELECTRICAL CHARACTERISTICS (@ V+ = +15 V, V-- = --15 V and $\chi$ = +25 °C, unless otherwise noted)

|                                        |                                           |                                                                                                 |     | SW 06B     |          | SW 06F     |            |            | SW 06G     |            |            |       |

|----------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------|-----|------------|----------|------------|------------|------------|------------|------------|------------|-------|

| Param eter                             | Sym bol                                   | Conditions                                                                                      | Min | Тур        | M ax     | Min        | Тур        | Max        | Min        | Тур        | Max        | Units |

| "ON" RESIST ANCE                       | R <sub>ON</sub>                           | $V_S = 0 \ V, \ l_S = 1 \ mA$<br>$V_S = \pm 10 \ V, \ l_S = 1 \ mA$                             |     | 60<br>65   | 80<br>80 |            | 60<br>65   | 100<br>100 |            | 100<br>100 | 150<br>150 | Ω     |

| R <sub>ON</sub> MATCH BETWEEN SWITCHES | R <sub>ON</sub> Match                     | $V_S=0$ V, $l_S=100~\mu\mathrm{A}^1$                                                            |     | 5          | 10       |            | 5          | 20         |            |            | 20         | %     |

| ANALOG VOLTAGE RANGE                   | V <sub>A</sub>                            | $l_S = 1 mA^2$ $l_S = 1 mA^2$                                                                   |     | +11<br>-15 |          | +10<br>-10 | +11<br>-15 |            | +10<br>-10 |            |            | v     |

| ANALOG CURRENT RANGE                   | l <sub>A</sub>                            | $V_S = \pm 10 \text{ V}$                                                                        | 10  | 15         |          | 7          | 12         |            | 5          | 10         |            | mA    |

| ΔR <sub>ON</sub> VS. APPLIED VOLTAGE   | ΔR <sub>ON</sub>                          | $-10 \text{ V} \le \text{V}_{\text{S}} \le 10 \text{ V},  \text{l}_{\text{S}} = 1.0 \text{ mA}$ |     | 5          | 15       |            | 10         | 20         |            | 10         | 20         | %     |

| SOURCE CURRENT IN "OFF" CONDITION      | l <sub>S(OFF)</sub>                       | $V_S = 10 \text{ V, } V_D = -10 \text{ V}^3$                                                    |     | 0.3        | 2.0      |            | 0.3        | 2.0        |            | 0.3        | 10         | nA    |

| DRAIN CURRENT IN "OFF" CONDITION       | l <sub>D(OFF)</sub>                       | $V_S = 10 \text{ V, } V_D = -10 \text{ V}^3$                                                    |     | 0.3        | 2.0      |            | 0.3        | 2.0        |            | 0.3        | 10         | nA    |

| SOURCE CURRENT IN "ON" CONDITION       | l <sub>S(ON)+</sub><br>l <sub>D(ON)</sub> | $V_S = V_D = \pm 10 \text{ V}^3$                                                                |     | 0.3        | 2.0      |            | 0.3        | 2.0        |            | 0.3        | 10         | nA    |

| LOGICAL "1" INPUT VOLTAGE              | V <sub>INH</sub>                          | Full Temperature Range <sup>2, 4</sup>                                                          | 2.0 |            |          | 2.0        |            |            | 2.0        |            |            | v     |

| LOGICAL "0" INPUT VOLTAGE              | V <sub>INL</sub>                          | Full Temperature Range <sup>2, 4</sup>                                                          |     |            | 0.8      |            |            | 0.8        |            |            | 0.8        | v     |

| LOGICAL "1" INPUT CURRENT              | l <sub>INH</sub>                          | $V_{IN} = 2.0 \text{ V to } 15.0 \text{ V}^5$                                                   |     |            | 5        |            |            | 5          |            |            | 10         | μA    |

| LOGICAL "0" INPUT                      | l <sub>INL</sub>                          | $V_{IN} = 0.8 \text{ V}$                                                                        |     | 1.5        | 5.0      |            | 1.5        | 5.0        |            | 1.5        | 10.0       | μA    |

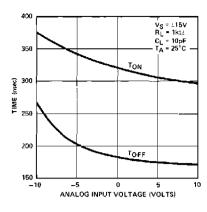

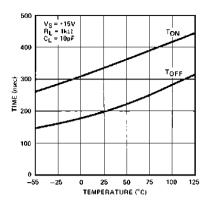

| TURN-ON TIME                           | t <sub>ON</sub>                           | See Switching Time<br>Test Circuit <sup>4, 6</sup>                                              |     | 340        | 500      |            | 340        | 600        |            | 340        | 700        | ns    |

| TURN-OFF TIME                          | t <sub>OFF</sub>                          | See Switching Time<br>Test Circuit <sup>4, 6</sup>                                              |     | 200        | 400      |            | 200        | 400        |            | 200        | 500        | ns    |

| BREAK-BEFORE-MAKE TIME                 | t <sub>ON</sub> -t <sub>OFF</sub>         | Note 7                                                                                          | 50  | 140        |          | 50         | 140        |            | 50         | 140        |            | ns    |

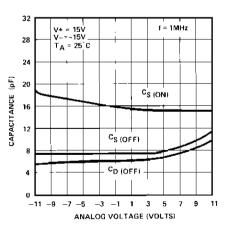

| SOURCE CAPACITANCE                     | C <sub>S(OFF)</sub>                       | $V_S = 0 V^3$                                                                                   |     | 7.0        |          |            | 7.0        |            |            | 7.0        |            | pF    |

| DRAIN CAPACITANCE                      | C <sub>D(OFF)</sub>                       | $V_S = 0\ V^3$                                                                                  |     | 5.5        |          |            | 5.5        |            |            | 5.5        |            | pF    |

| CHANNEL "ON" CAPACITANCE               | C <sub>D(ON)+</sub><br>C <sub>S(ON)</sub> | $V_S = V_D = 0 V^3$                                                                             |     | 15         |          |            | 15         |            |            | 15         |            | pF    |

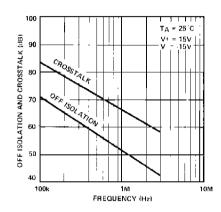

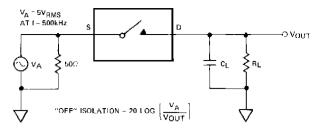

| "OFF" ISOLATION                        | l <sub>SO(OFF)</sub>                      | $V_S = 5 \text{ V rms}, R_L = 680 \Omega,$<br>$C_L = 7 \text{ pF}, f = 500 \text{ kHz}^3$       |     | 58         |          |            | 58         |            |            | 58         |            | dВ    |

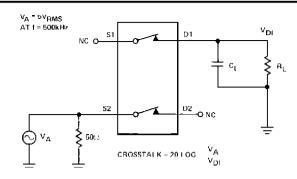

| CROSSTALK                              | Ст                                        | $V_S = 5 \text{ V rms}, R_L = 680 \Omega,$<br>$C_L = 7 \text{ pF}, f = 500 \text{ kHz}^3$       |     | 70         |          |            | 70         |            |            | 70         |            | đВ    |

| POSITIVE SUPPLY CURRENT                | l+                                        | All Channels "OFF", D1S = "0"3                                                                  |     | 5.0        | 6.0      |            | 5.0        | 9.0        |            | 6.0        | 9.0        | mA    |

| NEGATIVE SUPPLY CURRENT                | 1-                                        | All Channels "OFF", D1S = "0"3                                                                  |     | 3.0        | 5.0      |            | 4.0        | 7.0        |            | 4.0        | 7.0        | mA    |

| GROUND CURRENT                         | $l_G$                                     | All Channels "ON" or "OFF" <sup>3</sup>                                                         |     | 3.0        | 4.0      |            | 3.0        | 4.0        |            | 3.0        | 5.0        | mA    |

-2- REV. A

# ELECTRICAL CHARACTERISTICS (@ V+ = +15 V, V-- = --15 V, --5%C $\leq$ T<sub>A</sub> $\leq$ +125 °C for SW06BQ, --40°C $\leq$ T<sub>A</sub> $\leq$ +85 °C for SW06GP/GS, unless otherwise noted)

|                                         |                                           |                                                                                                 |            | SW 06B     |            | SW 06F     |            | F          | SW 06G     |            |            |       |

|-----------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------|

| Param eter                              | Symbol                                    | Conditions                                                                                      | Min        | Тур        | Max        | Min        | Тур        | Max        | Min        | Тур        | Max        | Units |

| TEMPERATURE RANGE                       | T <sub>A</sub>                            | Operating                                                                                       | -55        |            | +125       | -25        |            | +85        | 0          |            | 70         | °C    |

| "ON" RESISTANCE                         | R <sub>ON</sub>                           | $V_S = 0 \text{ V, } l_S = 1.0 \text{ mA}$<br>$V_S = \pm 10 \text{ V, } l_S = 1.0 \text{ mA}$   |            | 75<br>80   | 110<br>110 |            | 75<br>80   | 125<br>125 |            | 75<br>80   | 175<br>175 | Ω     |

| ΔR <sub>ON</sub> MATCH BETWEEN SWITCHES | Ron Match                                 | $V_S = 0$ V, $l_S = 100 \mu A^1$                                                                |            | 6          | 20         |            | 6          | 25         |            | 10         |            | %     |

| ANALOG VOLTAGE RANGE                    | V <sub>A</sub>                            | $\begin{array}{c} l_S = 1.0 \text{ mA}^2 \\ l_S = 1.0 \text{ mA}^2 \end{array}$                 | +10<br>-10 | +11<br>-15 |            | +10<br>-10 | +11<br>-15 |            | +10<br>-10 | +11<br>-15 |            | v     |

| ANALOG CURRENT RANGE                    | l <sub>A</sub>                            | $V_S = \pm 10 \text{ V}$                                                                        | 7          | 12         |            | 5          | 11         |            |            | 11         |            | mA    |

| ΔR <sub>ON</sub> WITH APPLIED VOLTAGE   | ΔR <sub>ON</sub>                          | $-10 \text{ V} \le \text{V}_{\text{S}} \le 10 \text{ V},  \text{l}_{\text{S}} = 1.0 \text{ mA}$ |            | 10         |            |            | 12         |            |            | 15         |            | %     |

| SOURCE CURRENT IN "OFF" CONDITION       | $l_{S(OFF)}$                              | $V_S = 10 \text{ V}, V_D = -10 \text{ V}$ $T_A = \text{Max Operating Temp}^{3, 9}$              |            |            | 60         |            |            | 30         |            |            | 60         | пA    |

| DRAIN CURRENT IN "OFF" CONDITION        | $l_{D(OFF)}$                              | $V_S = 10 \text{ V}, V_D = -10 \text{ V}$ $T_A = \text{Max Operating Temp}^{3, 9}$              |            |            | 60         |            |            | 30         |            |            | 60         | пA    |

| LEAKAGE CURRENT IN "ON" CONDITION       | l <sub>S(ON)+</sub><br>l <sub>D(ON)</sub> | $V_S = V_D = \pm 10 \text{ V}$ $T_A = \text{Max Operating Temp}^{3, 9}$                         |            |            | 100        |            |            | 30         |            |            | 60         | пA    |

| LOGICAL "1" INPUT CURRENT               | l <sub>INH</sub>                          | $V_{IN} = 2.0 \text{ V to } 15.0 \text{ V}^5$                                                   |            |            | 10         |            |            | 10         |            |            | 15         | μA    |

| LOGICAL "0" INPUT CURRENT               | l <sub>INL</sub>                          | $V_{IN} = 0.8 V$                                                                                |            | 4          | 10         |            | 4          | 10         |            | 5          | 15         | μА    |

| TURN-ON TIME                            | t <sub>ON</sub>                           | See Switching Time<br>Test Circuit <sup>4, 8</sup>                                              |            | 440        | 900        |            | 500        | 900        |            |            | 1000       | ns    |

| TURN-OFF TIME                           | t <sub>OFF</sub>                          | See Switching Time<br>Test Circuit <sup>4, 8</sup>                                              |            | 300        | 500        |            | 330        | 500        |            |            | 500        | ns    |

| BREAK-BEFORE-MAKE TIME                  | t <sub>ON</sub> -t <sub>OFF</sub>         | Note 7                                                                                          |            | 70         |            |            | 70         |            |            | 50         |            | ns    |

| POSITIVE SUPPLY CURRENT                 | l+                                        | All Channels "OFF," D1\$ = "0"3                                                                 |            |            | 9.0        |            |            | 13.5       |            |            | 13.5       | m A   |

| NEGATIVE SUPPLY CURRENT                 | 1-                                        | All Channels "OFF," D1S = "0"3                                                                  |            |            | 7.5        |            |            | 10.5       |            |            | 10.5       | mA    |

| GROUND CURRENT                          | $l_G$                                     | All Channels "ON" or "OFF" <sup>3</sup>                                                         |            |            | 6.0        |            |            | 7.5        |            |            | 7.5        | m A   |

#### NOTES

$^{1}V_{S}=0\ V,\ I_{S}=100\ \mu\text{A}.\ Specified as a percentage of }R_{AVERAGE}\ \ \text{where:}\ R_{AVERAGE}=\frac{R_{ON\,1}+R_{ON\,2}+R_{ON\,3}+R_{ON\,4}}{4}.$

Specifications subject to change without notice.

REV. A -3-

$<sup>^2</sup>$ Guaranteed by  $R_{ON}$  and leakage tests. For normal operation maximum analog signal voltages should be restricted to less than (V+) -4 V.

$<sup>^{3}</sup>$ Switch being tested ON or OFF as indicated,  $V_{INH} = 2.0 \text{ V}$  or  $V_{INL} = 0.8 \text{ V}$ , per logic truth table.

<sup>&</sup>lt;sup>4</sup>Also applies to disable pin.

$<sup>^5</sup>$ Current tested at  $V_{\rm IN} = 2.0$  V. This is worst case condition.

<sup>&</sup>lt;sup>6</sup>Sample tested.

<sup>&</sup>lt;sup>7</sup>Switch is guaranteed by design to provide break-before-make operation.

<sup>&</sup>lt;sup>8</sup>Guaranteed by design.

$<sup>^9</sup>$ Parameter tested only at  $T_A = +125$  $^{\circ}$ C for military grade device.

# SW06 WAFER TEST LIMITS (@ V+ = +15 V, V-- = --15 V, $\chi$ = +25 °C, unless otherwise noted)

| Param eter                             | Sym bol                     | Conditions                                                                                      | SW 06N<br>Limit | SW 06G<br>Lim it | Units   |

|----------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|-----------------|------------------|---------|

| "ON" RESIST ANCE                       | R <sub>ON</sub>             | $-10 \text{ V} \le \text{V}_{\text{A}} \le 10 \text{ V}, \text{ I}_{\text{S}} \le 1 \text{ mA}$ | 80              | 100              | Ωmax    |

| R <sub>ON</sub> MATCH BETWEEN SWITCHES | R <sub>ON</sub> Match       | $V_{A} = 0 \ V, \ I_{S} \le 100 \ \mu A$                                                        | 15              | 20               | % max   |

| $\Delta R_{\rm ON}$ VS. $V_{\rm A}$    | $\Delta R_{\mathrm{ON}}$    | $-10 \text{ V} \le \text{V}_{\text{A}} \le 10 \text{ V}, \text{I}_{\text{S}} \le 1 \text{ mA}$  | 10              | 20               | % max   |

| POSITIVE SUPPLY CURRENT                | I+                          | Note 1                                                                                          | 6.0             | 9.0              | m A max |

| NEGATIVE SUPPLY CURRENT                | I–                          | Note 1                                                                                          | 5.0             | 7.0              | mA max  |

| GROUND CURRENT                         | $I_G$                       | Note 1                                                                                          | 4.0             | 4.0              | mA max  |

| ANALOG VOLT AGE RANGE                  | $V_{A}$                     | $I_S = 1 \text{ mA}$                                                                            | ±10.0           | ±10.0            | V min   |

| LOGIC "1" INPUT VOLTAGE                | $V_{\mathrm{INH}}$          | Note 2                                                                                          | 2.0             | 2.0              | V min   |

| LOGIC "0" INPUT VOLTAGE                | $V_{\mathrm{INL}}$          | Note 2                                                                                          | 0.8             | 0.8              | Vmax    |

| LOGIC "0" INPUT CURRENT                | $I_{\mathrm{INL}}$          | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq 0.8 \text{ V}$                                      | 5.0             | 5.0              | μA max  |

| LOGIC "1" INPUT CURRENT                | $I_{\mathrm{IN}\mathrm{H}}$ | $2.0 \text{ V} \le \text{V}_{\text{IN}} \le 15 \text{ V}^3$                                     | 5               | 5                | μA max  |

| ANALOG CURRENT RANGE                   | $I_A$                       | $V_S = \pm 10 \text{ mV}$                                                                       | 10              | 7                | m A min |

#### NOTE

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

## TYPICAL ELECTRICAL CHARACTERISTICS (@ V+ = +15 V, V-- = --15 V, X = +25°C, unless otherwise noted)

| Param eter                       | Sym bol              | Conditions                                                                                     | SW 06N<br>Typical | SW 06G<br>Typical | Units |

|----------------------------------|----------------------|------------------------------------------------------------------------------------------------|-------------------|-------------------|-------|

| "ON" RESIST ANCE                 | R <sub>ON</sub>      | $-10 \text{ V} \le \text{V}_{\text{A}} \le 10 \text{ V}, \text{I}_{\text{S}} \le 1 \text{ mA}$ | 60                | 60                | Ω     |

| TURN-ON TIME                     | t <sub>ON</sub>      |                                                                                                | 340               | 340               | ns    |

| TURN-OFF TIME                    | t <sub>OFF</sub>     |                                                                                                | 200               | 200               | ns    |

| DRAIN CURRENT IN "OFF" CONDITION | I <sub>D(OFF)</sub>  | $V_{S} = 10 \text{ V}, V_{D} = -10 \text{ V}$                                                  | 0.3               | 0.3               | n A   |

| "OFF" ISOLATION                  | I <sub>SO(OFF)</sub> | $f = 500 \text{ kHz}, R_L = 680 \Omega$                                                        | 58                | 58                | dB    |

| CROSSTALK                        | C <sub>T</sub>       | $f = 500 \text{ kHz}, R_L = 680 \Omega$                                                        | 70                | 70                | dB    |

#### NOTES

REV. A

<sup>&</sup>lt;sup>1</sup>Power supply and ground current specified for switch "ON" or "OFF."

<sup>&</sup>lt;sup>2</sup>Guaranteed by R<sub>ON</sub> and leakage tests.

$<sup>{}^{3}</sup>$ Current tested at  $V_{IN} = 2.0 \text{ V}$ . This is worst case condition.

#### ABSOLUTE MAXIMUM RATINGS1

| Operating Temperature Range                   |

|-----------------------------------------------|

| SW06BQ, BRC                                   |

| SW06FQ40°C to +85°C                           |

| SW06GP, GS40°C to +85°C                       |

| Storage Temperature Range65°C to +150°C       |

| Lead Temperature (Soldering, 60 sec) +300°C   |

| Maximum Junction Temperature +150°C           |

| V+ Supply to V- Supply +36 V                  |

| V+ Supply to Ground +36 V                     |

| Logic Input Voltage (-4 V or V-) to V+ Supply |

| Analog Input Voltage Range                    |

| Continuous V – Supply to V+ Supply +20 V      |

| Maximum Current Through                       |

| Any Pin Including Switch                      |

| Package Type            | θ <sub>JA</sub> <sup>2</sup> | θ <sub>JC</sub> | Units |

|-------------------------|------------------------------|-----------------|-------|

| 16-Pin Hermetic DIP (Q) | 100                          | 16              | °C/W  |

| 16-Pin Plastic DIP (P)  | 82                           | 39              | °C/W  |

| 20-Contact LCC (RC)     | 98                           | 38              | °C/W  |

| 16-Pin SOL (S)          | 98                           | 30              | °C/W  |

#### NOTES

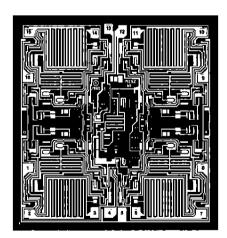

#### DICE CHARACTERISTICS

Die Size  $0.101 \times 0.097$  inch, 9797 sq. mils  $(2.565 \times 2.464 \text{ mm}, 6320 \text{ sq. mm})$

#### ORDERING GUIDE

| M odel  | Tem perature<br>Range | Package<br>Description | Package<br>Option |

|---------|-----------------------|------------------------|-------------------|

| SW06BQ  | −55°C to +125°C       | Cerdip                 | Q-16              |

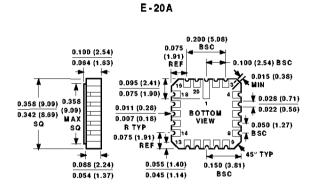

| SW06BRC | −55°C to +125°C       | LCC                    | E-20A             |

| SW06FQ  | -40°C to +85°C        | Cerdip                 | Q-16              |

| SW06GP  | -40°C to +85°C        | Plastic DIP            | N-16              |

| SW06GS  | -40°C to +85°C        | SOL                    | R-16              |

#### TRUTH TABLE

|                  |                | Switch S          | State             |

|------------------|----------------|-------------------|-------------------|

| Disable<br>Input | Logic<br>Input | Channels<br>1 & 2 | Channels<br>3 & 4 |

| 0                | X              | OFF               | OFF               |

| 1 or NC          | 0              | OFF               | $\mathbf{ON}$     |

| 1 or NC          | 1              | ON                | OFF               |

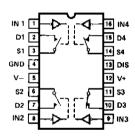

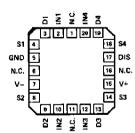

#### PIN CONNECTIONS

16-Pin DIP (Q or P-Suffix) 16-Pin SOL (S-Suffix)

SW 06B R C /883 L C C Package (R C - Suffix)

REV. A -5-

$<sup>^{1}\!</sup>Ab$  solute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for Cerdip, P-DIP, and LCC packages;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SO package.

## SW06--Typical Performance Characteristics

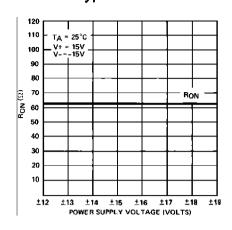

"ON" Resistance vs. Power Supply Voltage

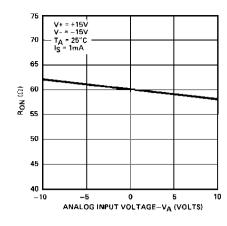

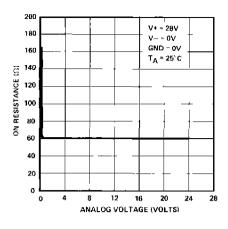

"ON" Resistance vs. Analog Voltage

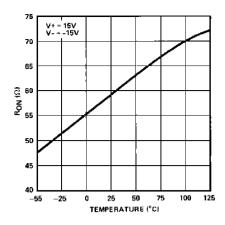

Ron vs. Temperature

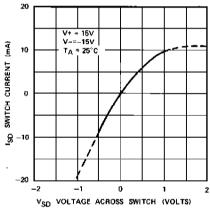

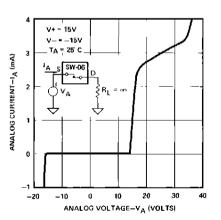

Switch Current vs. Voltage

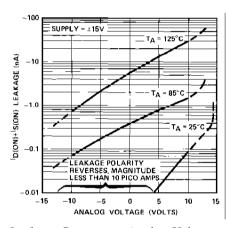

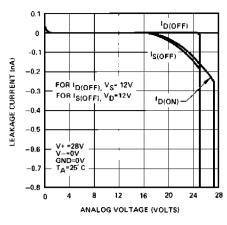

Leakage Current vs. Analog Voltage

Leakage Current vs. Temperature

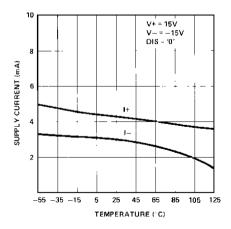

Supply Current vs. Temperature

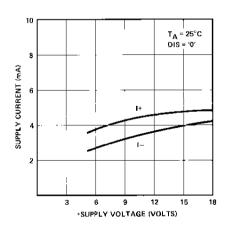

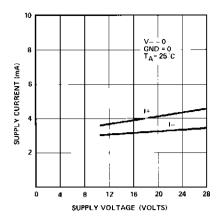

Supply Current vs. Supply Voltage

-6-

Switch Capacitance vs. Analog Voltage

REV. A

**SW06**

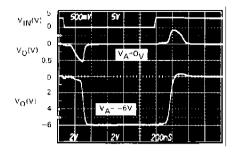

$T_{ON}/T_{OFF}$  Switching Response

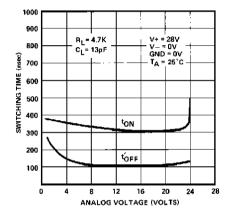

Switching Time vs. Analog Voltage

Switching Time vs. Temperature

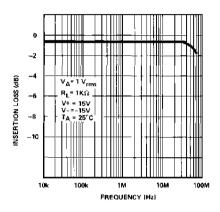

Insertion Loss vs. Frequency

Crosstalk and "OFF" Isolation vs. Frequency

Total Harmonic Distortion

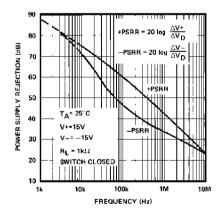

Power Supply Rejection vs. Frequency

Overvoltage Characteristics

REV. A -7-

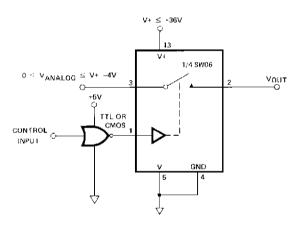

## SW06--Typical Performance Characteristics (Operating and Single Supply)

"On" Resistance vs. Analog Voltage

Leakage Current vs. VANALOG

Supply Current vs. Supply Voltage

#### Switching Time vs. Supply Voltage

#### NOTE

These single-supply-operation characteristic curves are valid when the negative power supply V– is tied to the logic ground reference pin "GND." TTL input compatibility is still maintained when "GND" is the same potential as the TTL ground.  $t_{\rm OFF}$  is measured from 50% of logic input waveform to 0.9  $V_{\rm O}$ . The analog voltage range extends from 0 V to V+ –4 V; the switch will no longer respond to logic control when  $V_{\rm A}$  is within 4 volts of V+.

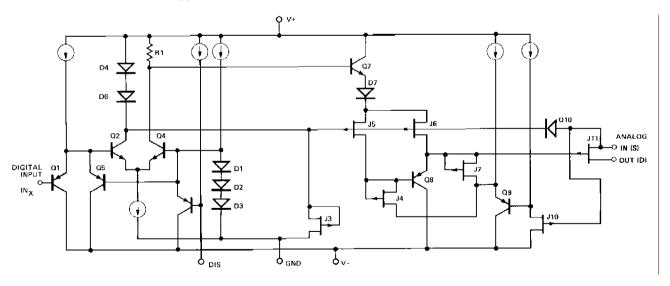

Simplified Schematic Diagram (Typical Switch)

-8- REV. A

**SW06**

"Off" Isolation Test Circuit

Crosstalk Test Circuit

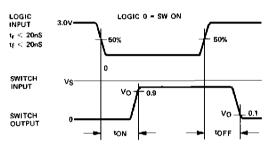

SWITCH OUTPUT WAVEFORM SHOWN FOR  $\rm V_S$  = CONSTANT WITH LOGIC INPUT WAVEFORM AS SHOWN.  $\rm V_O$  IS THE STEADY STATE OUTPUT WITH SWITCH ON. LOGIC INPUT IS INVERTED FOR SWITCH 1 & 2

Switching Time Test Circuit

REV. A -9-

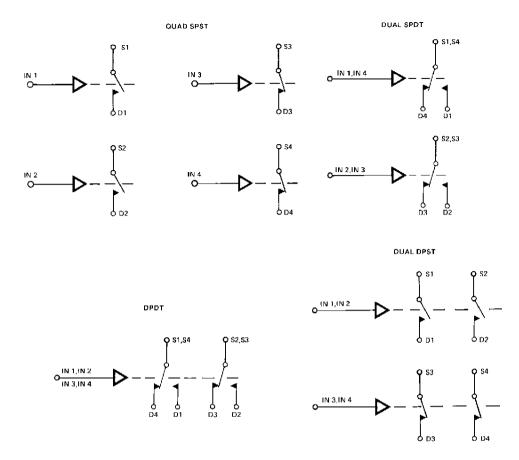

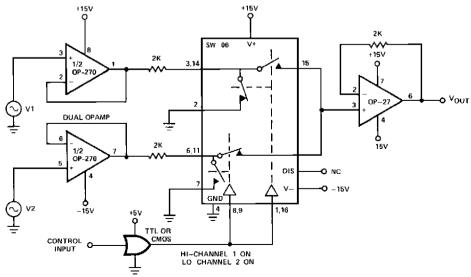

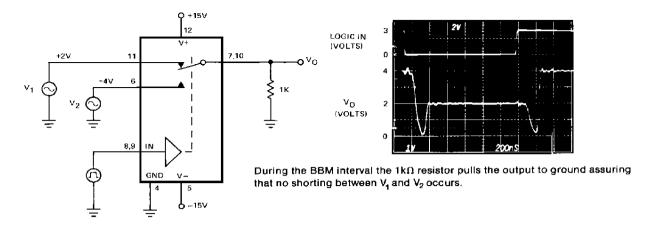

Figure 1. Functional Applications of SW06

#### APPLICATIONS INFORMATION

The single analog switch product configures, by appropriate pin connections, into four switch applications. As shown in Figure 1, the SW06 connects as a QUAD SPST, a DUAL SPDT, a DUAL DPST, or a DPDT analog switch. This versatility increases further when taking advantage of the disable input (DIS) which turns all switches OFF when taken active low.

Ion-implantation of the JFET analog switch achieves low ON resistance and tight channel-to-channel matching. Combining the low ON resistance and low leakage currents results in a worst case voltage error figure  $V_{ERROR} \ @ +125^{\circ}C = I_{D(ON)} \times R_{SD(ON)} = 100 \text{ nA} \times 100 \ \Omega = 11 \text{ microvolts}.$  This amount of error is negligible considering dissimilar-metal thermally-induced offsets will be in the 5 to 15 microvolt range.

#### LOGIC INPUTS

The logic inputs (IN<sub>X</sub>) and disable input (DIS) are referenced to a TTL logic threshold value of two forward diode drops (1.4 V at +25°C) above the GND terminal. These inputs use PNP transistors which draw maximum current at a logic "0" level and drops to a leakage current of a reverse biased diode as the logic input voltage raises above 1.4 volts. Any logic input voltage greater than 2.0 volts becomes logic "1," less than 0.8 volts becomes logic "0" resulting in full TTL noise immunity not available from similar CMOS input analog switches. The PNP transistor inputs require such low input current that the SW06 approaches fan-ins of CMOS input devices. These bipolar logic inputs exceed any CMOS input circuit in resistance to static voltage and radiation susceptibility. No damage will occur to the SW06 if logic high voltages are present when the SW06 power

supplies are OFF. When the V+ and V- supplies are OFF, the logic inputs present a reverse bias diode loading to active logic inputs. Input logic thresholds are independent of V+ and V- supplies making single V+ supply operation possible by simply connecting GND and V- together to the logic ground supply.

## ANALOG VOLTAGE AND CURRENT ANALOG VOLTAGE

These switches have constant ON resistance for analog voltages from the negative power supply (V–) to within 4 volts of the positive power supply. This characteristic shown in the plots results in good total harmonic distortion, especially when compared to CMOS analog switches that have a 20 to 30 percent variation in ON resistance versus analog voltage. Positive analog input voltage should be restricted to 4 volts less than V+ assuring the switch remains open circuit in the OFF state. No increase in switch ON resistance occurs when operating at supply voltages less than  $\pm 15$  volts (see plot). Small signals have a 3 dB down frequency of 70 MHz (see insertion loss versus frequency plot).

#### ANALOG CURRENT

The analog switches in the ON state are JFETs biased in their triode region and act as switches for analog current up to the  $I_A$  specification (see plot of  $I_{\rm DS}$  vs  $V_{\rm DS}$ ). Some applications require pulsed currents exceeding the  $I_A$  spec. For example, an integrator reset switch discharging a shunt capacitor will produce a peak current of  $I_{A(\rm PEAK)} = V_{\rm CAP}/R_{\rm DS(ON)}$ . In this application, it is best to connect the source to the most positive end of the capacitor, thereby achieving the lowest switch resistance and

-10- REV. A

fastest reset times. The switch can easily handle any amount of capacitor discharge current subject only to the maximum heat dissipation of the package and the maximum operating junction temperature from which repetition can be established.

#### SWITCHING

Switching time  $t_{ON}$  and  $t_{OFF}$  characteristics are plotted versus  $V_{ANALOG}$  and temperature. In all cases,  $t_{OFF}$  is designed faster than  $t_{ON}$  to ensure a break-before-make interval for SPDT and DPDT applications. The disable input (DIS) has the same switching times ( $t_{ON}$  and  $t_{OFF}$ ) as the logic inputs (IN $_X$ ).

Switching transients occurring at the source and drain contacts results from ac coupling of the switching FETs gate-to-source and gate-to-drain coupling capacitance. The switch turn ON will cause a negative going spike to occur and the turn OFF will cause a positive spike to occur. These spikes can be reduced by additional capacitance loading, lower values of  $R_{\rm L}$ , or switching an additional switch (with its extra contact floating) to the opposite state connected to the spike sensitive node.

#### **DISABLE NODE**

This TTL compatible node is similar to the logic inputs  $IN_X$  but has an internal 2  $\mu$ A current source pull-up. If disable is left unconnected, it will assume the logic "1" state, then the state of the switches is controlled only by the logic inputs  $IN_X$ .

#### **POWER SUPPLIES**

This product operates with power supply voltages ranging from  $\pm 12$  to  $\pm 18$  volts; however, the specifications only guarantee device parameters with  $\pm 15$  volt  $\pm 5\%$  power supplies. The power supply sensitive parameters have plots to indicate effects of supply voltages other than  $\pm 15$  volts.

### Typical Applications

Operation from Single Positive Power Supply

4-Channel Sample Hold Amplifier

THIS SWITCH ARRANGEMENT IMPROVES OFF ISOLATION BY 30dB

High Off Isolation Selector Switch (Shunt-Series Switch)

Single Pole Double Throw Selector Switch with Break-Before-Make Interval

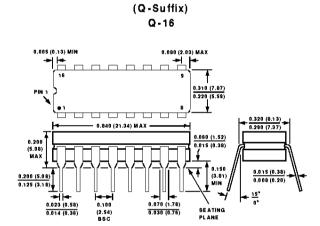

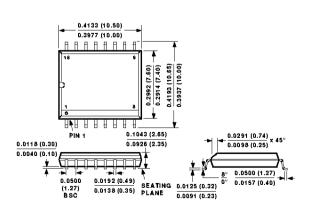

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

20-Terminal Leadless Chip Carrier

(RC-Suffix)

16-Lead Wide Body SOL

(S-Suffix)

R-16/SOL-16

16-Lead Cerdip

N-16 0.840 (21.33) 0.745 (18.93) 0.280 (7.11) 0.240 (6.10) - ₩ 0,325 (8,25) 0.300 (7.62) 0.195 (4.95) 0.060 (1.52) PIN 1 0.115 (2.93) 0.015 (0.38) 0.210 (5.33) 0.130 (3.30) MIN 0.160 (4.06) 0.115 (2.93) 0.015 (0.381) 0.070 (1.77) SEATING 0.045 (1.15) PLANE 0.022 (0.558) 0.100 0.008 (0.204) (2.54) BSC 0.014 (0.356)

16-Lead Plastic DIP

(P-Suffix)

-12- REV. A