# **Two Phase General Purpose PWM Controller**

## **General Description**

The RT8805 is the most compact dual-phase synchronous buck controller in the industry specifically designed for high power density applications. This part is capable of delivering up to 60A output current due to its embedded bootstrapped drivers that support 12V + 12V driving capability.

The phase currents are sensed by innovative time sharing R<sub>DS(ON)</sub> current sensing technique for current balance and over current balance. Using one common GM amplifier to sense two phase currents eliminates offset and nonlinearity of the GM amplifier and yields good current balance. Other features include adjustable operation frequency from 50kHz to 1MHz, adjustable soft-start, PGOOD, external compensation, enable/shutdown for various application and performance consideration.

The RT8805 comes to a tiny footprint package of VQFN-16L 3x3 and VQFN-24L 4x4 packages.

## **Ordering Information**

RT8805 🗆 🗖 └─Package Type QV: VQFN-16L 3x3 (V-Type) QVA: VQFN-24L 4x4 (V-Type) (Exposed Pad-Option 1) Lead Plating System

P: Pb Free

G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- > RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- 12V Power Supply Voltage

- 2 Phase Power Conversion

- Embedded 12V Boot Strapped Driver

- Precise Core Voltage Regulation

- Low Side MOSFET RDS(ON) Current Sensing for **Power Stage Current Balance**

- External Compensation

- Adjustable Soft-Start

- Adjustable Frequency and Typical at 300kHz Per **Phase**

- Power Good Indication

- Adjustable Over Current Protection

- External Reference Voltage Tracking (RT8805xQVA)

- Small 16-Lead and 24-Lead VQFN Packages

- RoHS Compliant and 100% Lead (Pb)-Free

### **Applications**

- Middle-High End GPU Core Power

- High End Desktop PC Memory Core Power

- Low Output Voltage, High Power Density DC-DC Converters

- Voltage Regulator Modules

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

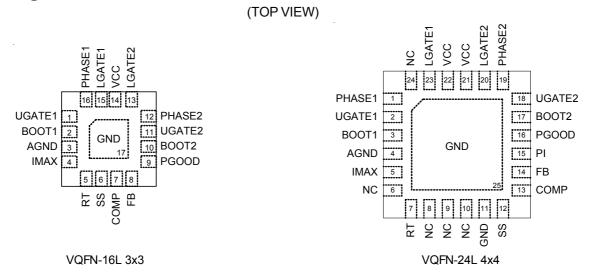

## **Pin Configurations**

#### Note:

NC pins (6, 8, 9, 10, 24) have no internal bonding wire connection. The landing pad of these pins can be tied to GND plane for better thermal relief.

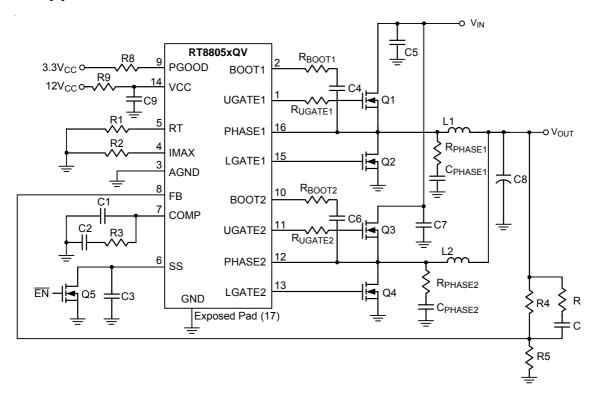

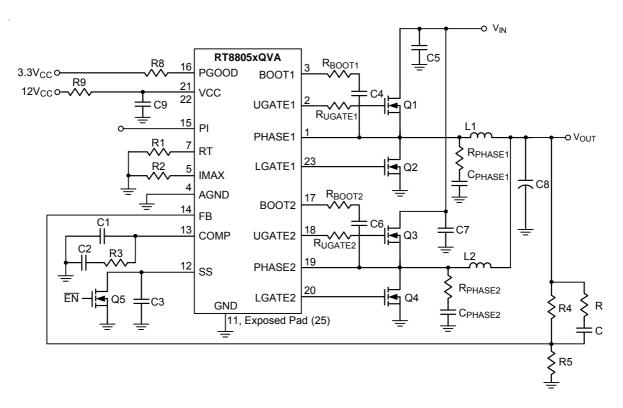

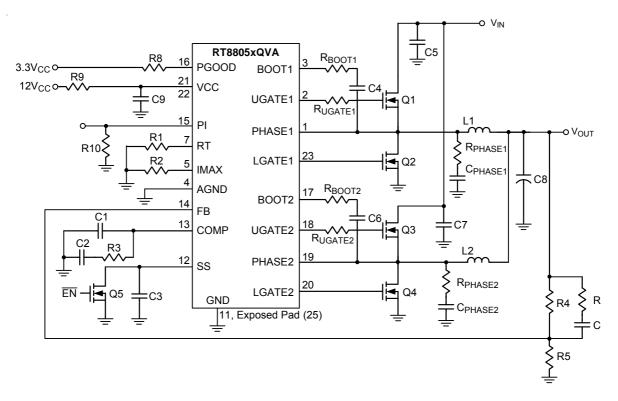

# **Typical Application Circuit**

Figure A. Application Circuit for RT8805xQV (VQFN-16L 3x3)

Figure B. Application Circuit for RT8805xQVA (VQFN-24L 4x4)-Standalone Mode (PI Disabled)

Figure C. Application Circuit for RT8805xQVA (VQFN-24L 4x4)-Tracking Mode (PI Enabled)

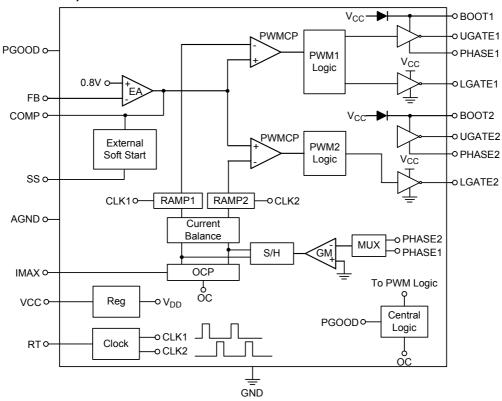

# **Function Block Diagram**

RT8805xQV (VQFN-16L 3x3)

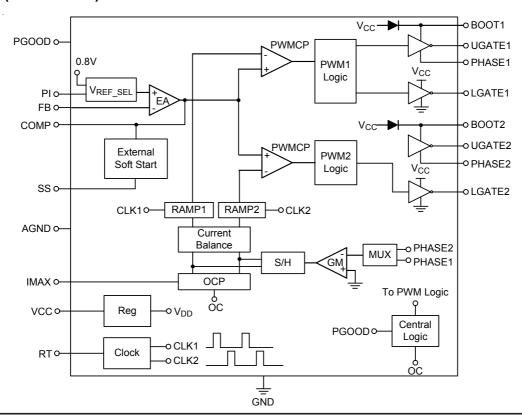

### RT8805xQVA (VQFN-24L 4x4)

# **Functional Pin Description**

| Pin No.          |                         | Pin Name    | Pin Function                                                                                                                                                           |  |  |

|------------------|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VQFN-16L 3x3     | VQFN-24L 4x4            | FIII Naille | Fill Fullction                                                                                                                                                         |  |  |

| 16               | 1                       | PHASE1      | These pins are return nodes of the high-side driver. Connect These pins to high-side MOSFET sources together with the                                                  |  |  |

| 12               | 19                      | PHASE2      | low-side MOSFET drains and the inductors.                                                                                                                              |  |  |

| 1                | 2                       | UGATE1      | Upper Gate Drive. These pins drive the gates of the high side                                                                                                          |  |  |

| 11               | 18                      | UGATE2      | MOSFETs.                                                                                                                                                               |  |  |

| 2                | 3                       | BOOT1       | Bootstrap Power Pin. These pins power the high-side MOSFET drivers. Connect These pins to the junctions of the                                                         |  |  |

| 10               | 17                      | воот2       | bootstrap capacitors.                                                                                                                                                  |  |  |

| 3                | 4                       | AGND        | Chip Analog Ground.                                                                                                                                                    |  |  |

| 4                | 5                       | IMAX        | Maximum Current Setting. This pin sets the current limiting level. Connect this pin with resistor to ground to set the current limit.                                  |  |  |

|                  | 6, 8, 9, 10, 24         | NC          | No Internal Connection. Can be tied to GND for better thermal relief.                                                                                                  |  |  |

| 5                | 7                       | RT          | Timing Resistor. Connect a resistor from RT to AGND to set the clock frequency.                                                                                        |  |  |

| 17 (Exposed Pad) | 11,<br>25 (Exposed Pad) | GND         | The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                    |  |  |

| 6                | 12                      | SS          | Soft-Start Pin. This pin provides soft-start function for controller. The COMP voltage of the converter follows the ramping voltage on the SS pin.                     |  |  |

| 7                | 13                      | COMP        | Compensation Pin. This pin is output node of the error amplifier.                                                                                                      |  |  |

| 8                | 14                      | FB          | Feedback Pin. This pin is negative input pin of the error amplifier.                                                                                                   |  |  |

| 9                | 16                      | PGOOD       | Power Good. PGOOD is an open drain output used to indicate the status of the voltages on SS pin and FB pin. PGOOD will go high impedance when SS > 3.7V and FB > 0.6V. |  |  |

| 15               | 23                      | LGATE1      | Lower Gate Drive. These pins drive the gate of the low side                                                                                                            |  |  |

| 13               | 20                      | LGATE2      | MOSFETs.                                                                                                                                                               |  |  |

| 14               | 21, 22                  | VCC         | The VCC pin is the external 12V power. Internal 5V power $(V_{DD})$ is regulated from this pin. This pin also powers the low side MOSFET drivers.                      |  |  |

|                  | 15                      | PI          | External reference voltage pin. This pin sets the voltage of FB pin when close loop.                                                                                   |  |  |

Copyright © 2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS8805-04 May 2014 www.richtek.com

# Absolute Maximum Ratings (Note 1)

| Supply Voltage, V <sub>CC</sub>                             |                |

|-------------------------------------------------------------|----------------|

| PHASE to GND                                                |                |

| DC                                                          |                |

| < 200ns                                                     |                |

| • BOOT to PHASE                                             | 15V            |

| BOOT to GND                                                 |                |

| DC                                                          |                |

| < 200ns                                                     |                |

| • Input, Output or I/O Voltage                              | GND-0.3V to 7V |

| • Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C |                |

| VQFN-16L 3x3                                                | 1.47W          |

| VQFN-24L 4x4                                                | 1.923W         |

| Package Thermal Resistance (Note 2)                         |                |

| VQFN–16L 3x3, $\theta_{JA}$                                 | 68°C/W         |

| VQFN–24L 4x4, $\theta_{JA}$                                 | 52°C/W         |

| VQFN–16L 3x3, $\theta_{JC}$                                 | 7.5°C/W        |

| VQFN–24L 4x4, $\theta_{JC}$                                 | 7°C/W          |

| Junction Temperature                                        | 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                     | 260°C          |

| • ESD Susceptibility (Note 3)                               |                |

| HBM (Human Body Mode)                                       | 1.5kV          |

| MM (Machine Mode)                                           | 200V           |

|                                                             |                |

|                                                             |                |

#### **Recommended Operating Conditions** (Note 4)

| • | Supply Voltage             | 12V ±10%       |

|---|----------------------------|----------------|

| • | Junction Temperature Range | –40°C to 125°C |

|   | A Livida                   | 40001 0500     |

###

### **Electrical Characteristics**

$(V_{IN} = 12V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                 | Symbol           | Test Conditions      | Min | Тур | Max  | Unit |

|---------------------------|------------------|----------------------|-----|-----|------|------|

| Supply Input              |                  |                      |     |     |      |      |

| Power Supply Voltage      | V <sub>CC</sub>  |                      |     | 12  | 13.2 | V    |

| Power On Reset            | V <sub>POR</sub> |                      | 5.4 | 5.9 | 6.5  | V    |

| Power On Reset Hysteresis |                  |                      |     | 0.3 | _    | V    |

| Power Supply Current      | I <sub>VCC</sub> | V <sub>SS</sub> = 0V |     | 10  | _    | mA   |

| Soft Start                |                  |                      |     |     |      |      |

| Soft Start Current        | I <sub>SS</sub>  |                      | 8   | 10  | 15   | μА   |

| Parameter                     | Symbol                  | Test Conditions                                                         | Min   | Тур  | Max   | Unit |

|-------------------------------|-------------------------|-------------------------------------------------------------------------|-------|------|-------|------|

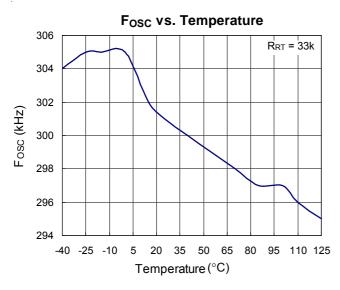

| Oscillator                    |                         |                                                                         |       |      |       |      |

| Free Running Frequency        | f <sub>OSC</sub>        | RT = 33kΩ                                                               | 255   | 300  | 345   | kHz  |

| Frequency Variation           |                         |                                                                         | -15   |      | 15    | %    |

| Frequency Range               |                         | (Note 5)                                                                | 50    | 300  | 1000  | kHz  |

| Maximum Duty Cycle            |                         |                                                                         | 70    | 75   | 80    | %    |

| Ramp Amplitude                |                         |                                                                         |       | 1.6  | _     | V    |

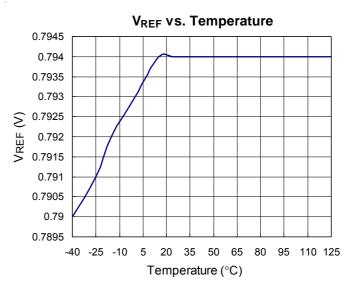

| Reference Voltage             |                         |                                                                         | •     |      |       |      |

| Feedback Voltage              | V <sub>FB</sub>         | Internal reference                                                      | 0.788 | 0.8  | 0.812 | ٧    |

| External Reference Accuracy   |                         | V <sub>Pl</sub> = 0.9V<br>Measure I V <sub>Pl</sub> – V <sub>FB</sub> I | -12   | 0    | 12    | mV   |

| Error Amplifier               |                         |                                                                         | •     |      |       |      |

| DC Gain                       |                         |                                                                         | 60    | 70   | _     | dB   |

| Gain-Bandwidth Product        | GBW                     | C <sub>LOAD</sub> = 5pF                                                 | 6     | 10   | _     | MHz  |

| Trans-conductance             | GM                      | $R_{LOAD} = 20k\Omega$                                                  | 600   | 660  | _     | μΑ/V |

| MAX Current (Source & Sink)   | I <sub>COMP</sub>       | V <sub>COMP</sub> = 2.5V                                                | 300   | 360  | _     | μА   |

| Current Sense GM Amplifier    |                         |                                                                         |       | •    | •     |      |

| OC                            | V <sub>PHASE</sub>      | $R_{IMAX} = 33k\Omega$                                                  |       | -220 | _     | mV   |

| Gate Driver                   | *                       |                                                                         |       |      |       |      |

| Maximum Upper Drive Source    | IUGATE(MAX)             | BOOT – PHASE = 12V                                                      | 1     |      |       | Α    |

| Upper Drive Sink              | RUGATE                  | V <sub>UGATE</sub> = 1V                                                 |       | 3.5  | 7     | Ω    |

| Maximum Lower Drive Source    | I <sub>LGATE(MAX)</sub> | PV <sub>CC</sub> = 12V                                                  | 1     |      |       | Α    |

| Lower Drive Sink              | R <sub>LGATE</sub>      | V <sub>LGATE</sub> = 1V                                                 |       | 2    | 4     | Ω    |

| Protection                    |                         |                                                                         |       |      |       |      |

| Under Voltage Protection      |                         |                                                                         | 0.55  | 0.6  | 0.65  | ٧    |

| Power Sequence                |                         |                                                                         |       |      |       |      |

| Power Good Threshold          |                         | Measure SS Voltage                                                      | 3.4   | 3.8  | 4.2   | V    |

| Power Good Output Low Voltage |                         | I <sub>PGOOD</sub> = 4mA                                                |       | 0.05 | 0.2   | V    |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective four layers thermal conductivity test board of JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Final test guarantees operating from 300kHz to 600kHz. Outside of this range is guaranteed by design.

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8805-04 May 2014 www.richtek.com

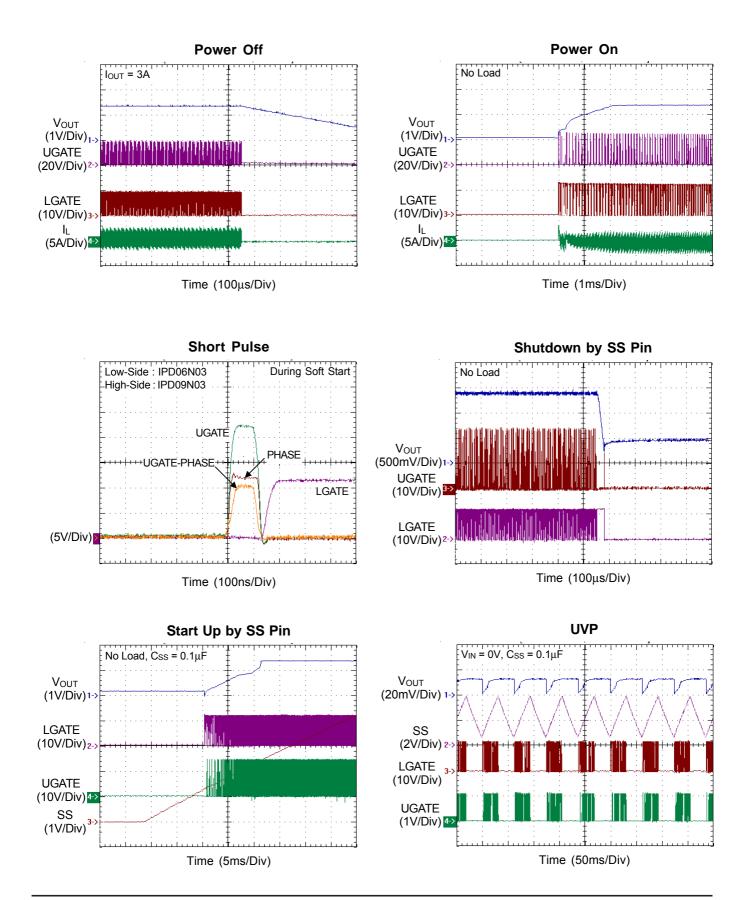

# **Typical Operating Characteristics**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8805-04 May 2014 www.richtek.com

## **Applications Information**

#### **Power On Reset**

RT8805 operates with input voltage at VCC pin ranging from 5.9V to 15V. An internal linear regulator regulates the input voltage to 5V for internal control circuit use. The POR (power on reset) circuitry monitors the supply voltage to make sure the supply voltage is high enough for RT8805 normal work. When the regulated power exceeds 4.2V typically, the RT8805 releases the reset state and works according to the setting. Once the regulated voltage is lower than 4.0V, POR circuitry resets the chip. Hysteresis between the rising and falling thresholds assure that once enabled, the RT8805 will not inadvertently turn off unless the bias voltage drops substantially (see Electrical Specifications).

#### **Enable, Soft Start and Power Good**

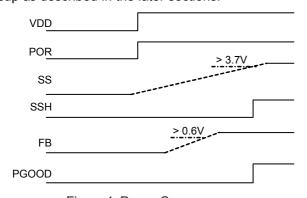

Once POR releases, the RT8805 begins its soft start cycle as shown in Figure 1. A 10µA source current charges the capacitor C<sub>SS</sub> connected to SS to control the soft start behavior of RT8805. During soft start, SS voltage increases linearly and clamps the error amplifier output. Duty cycle and output voltage increase accordingly. The soft start limits inrush current from input capacitors.

The RT8805 regards SS pin voltage higher than 3.7V as the end of soft start cycle. Then RT8805 trip PGOOD to high impedance if no fault occurs indicating power good. The SS pin also act as the timer during OCP and UVP hiccup as described in the later sections.

Figure 1. Power Sequence

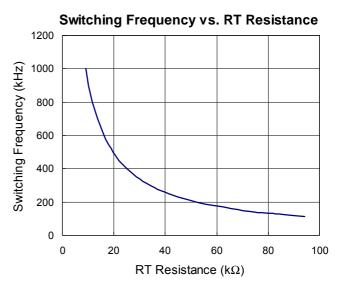

#### Frequency setting

The converter switching frequency is programmed by connecting a resistor from the RT pin to GND. Figure 2 illustrates switching frequency vs. R<sub>RT</sub>.

Figure 2. Switching Frequency vs. RRT

#### **Voltage Control**

The voltage control loop consists of error amplifier, multiphase pulse width modulator, drivers and power components. As conventional voltage mode PWM controller, the output voltage is locked at the positive input of error amplifier and the error signal is used as the control signal of pulse width modulator. The PWM signals of different channels are generated by comparison of EA output and split-phase sawtooth wave. Power stage transforms V<sub>IN</sub> to output by PWM signal on-time ratio.

#### **Current Sensing Setting**

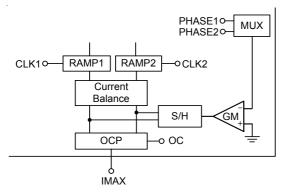

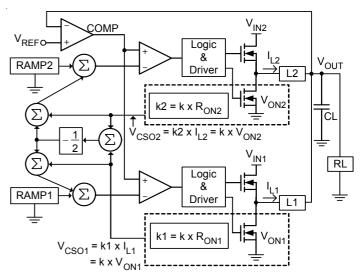

RT8805 senses the current of low side MOSFET in each synchronous rectifier when it is conducting for channel current balance and OCP detecting. The multiplexer and sensing GM amplifier converts the voltage on the sense component (can be a sense resistor or the R<sub>DS(ON)</sub> of the low side MOSFET) to current signal into internal circuit (see Figure 3).

Figure 3. Current Sensing Loop

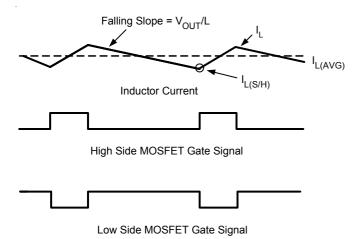

The sensing circuit gets  $I_X = I_{L(S/H)} \times R_{DS(ON)} \times GM$  by local feedback.  $I_X$  is sampled and held just before low side MOSFET turns off (See Figure 4). Therefore,

$$I_{X(S/H)} = I_{L(S/H)} \times R_{DS(ON)} \times GM$$

$$I_{L(S/H)} = I_{L(AVG)} - \frac{V_{OUT}}{L} \times \frac{T_{OFF}}{2},$$

$$T_{OFF} = \left[\frac{V_{IN} - V_{OUT}}{V_{IN}}\right] \times 5 \mu s,$$

$$Fsw = 200kHz$$

$$I_{X(S/H)} = \left[I_{L(AVG)} - \frac{V_{OUT} \times \left(\frac{V_{IN} - V_{OUT}}{V_{IN}}\right) \times 5\mu s}{2L}\right]$$

$$\times R_{DS(ON)} \times GM$$

Figure 4. Inductor Current and Gate signals

#### **Current Balance**

RT8805 senses the voltage drop of the low-side MOS and translates this to control the ramp signal. We can see that the voltage signal finally injected to channel one is proportional to ( $I_{L1}$  -  $I_{L2}$ ). Channel two is proportional to ( $I_{L2}$  -  $I_{L1}$ ). In steady state and current balance situation, there is no sensed signal injected into the ramp.

If  $I_{L1} > I_{L2}$ , the ramp bottom of channel 1 will be lifted up and decreased the duty of UGATE1. On the other hand, the ramp bottom of channel 2 will be pulled low to increase the duty of UGATE2. Finally, the loop will be back to the balance state through above mentioned negative feedback scheme. Figure 5 shows this scheme.

Figure 5. Current Balance

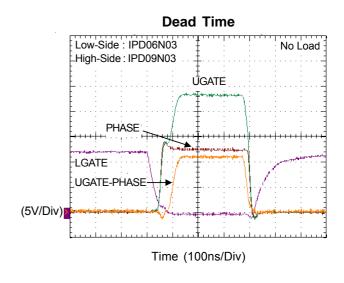

#### **Gate control**

- a. Before SS signal reach the valley of the ramp voltage, UGATE and LGATE will be off.

- b. If SS pin is pulled down 0.4V, UGATE and LGATE will be off.

- c. UV protect function caused by FB < 0.6V and SS > 3.7V, and controller will trigger Always Hiccup Mode.

- d. When OC function occurs and SS > 3.7V, a constant current of  $10\mu A$  starts to discharge the capacitor connected to SS pin right away. When OC occurs, UGATE and LGATE will be off. When the voltage at the capacitor connected to SS pin pass about 0.4V, a constant current of  $10\mu A$  starts to charge the capacitor.

The PWM signal is enable to pass to UGATE and LGATE. OCP function monitors both channels, either one can activate OCP. If the OC protection occurs three times, OCSD (Over Current Shut Down) will be activated and shut down the chip.

e. When fault conditions occur or SS < 0.4V. the current sense function will be disabled.

#### **Power Good**

PGOOD goes high when soft-start voltage > 3.7V, and no fault conditions.

### **Feedback Loop Compensation**

The RT8805 is a voltage mode controller; the control loop is a single voltage feedback path including an error amplifier and PWM comparator. In order to achieve fast transient response and accurate output regulation, an adequate compensator design is necessary. The goal of the compensation network is to provide adequate phase margin (greater than 45 degrees) and the highest 0dB crossing frequency. To manipulate loop frequency response under its gain crosses over 0dB at a slope of -20dB/ decade.

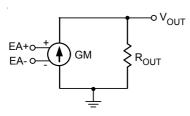

#### 1) Modulator Frequency Equations

RT8805 is a voltage mode buck converter using the high gain error amplifier with transconductance (OTA, Operational Transconductance Amplifier), as Figure 6 shown.

The Transconductance:

$$GM = \frac{\Delta I_{OUT}}{\Delta V_{M}}$$

$\Delta V_M = (EA+) - (EA-)$ ;  $\Delta I_{OUT} = E/A$  output current.

Figure 6. OTA Topology

This transfer function of OTA is dominated by a higher DC gain and the output filter (L<sub>OUT</sub> and C<sub>OUT</sub>) with a double pole frequency at F<sub>LC</sub> and a zero at F<sub>ESR</sub>. The DC gain of the modulator is the input voltage (V<sub>IN</sub>) divided by the peak to peak oscillator voltage V<sub>RAMP</sub>.

The first step is to calculate the complex conjugate poles contributed by the LC output filter.

The output LC filter introduces a double pole, 40dB/decade gain slope above its corner resonant frequency, and a total phase lag of 180 degrees. The resonant frequency of the LC filter expressed as follows:

$$F_{P(LC)} = \frac{1}{2\pi \times \sqrt{L_{OUT} \times C_{OUT}}}$$

The next step of compensation design is to calculate the ESR zero. The ESR zero is contributed by the ESR associated with the output capacitance. Note that this requires that the output capacitor should have enough ESR to satisfy stability requirements. The ESR zero of the output capacitor expressed as follows:

$$F_{Z(ESR)} = \frac{1}{2\pi \times C_{OUT} \times ESR}$$

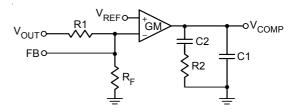

#### 2) Compensation Frequency Equations

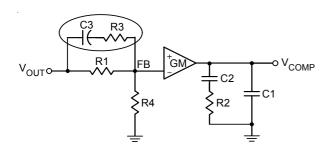

The compensation network consists of the error amplifier and the impedance networks as Figure 7 shown.

Figure 7. Compensation Loop

$$F_{Z1} = \frac{1}{2\pi \times R2 \times C2}$$

$$F_{P1} = 0$$

$$F_{P2} = \frac{1}{2\pi \times R2 \times \left(\frac{C1 \times C2}{C1 + C2}\right)}$$

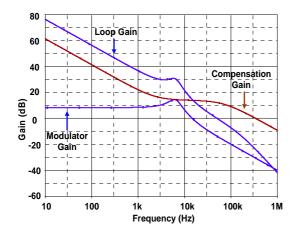

Figure 8 shows the DC-DC converter's gain vs. frequency. The compensation gain uses external impedance networks to provide a stable, high bandwidth loop. High crossover frequency is desirable for fast transient response, but often jeopardize the system stability. In order to cancel one of the LC filter poles, place F<sub>Z1</sub> before the LC filter resonant frequency. In the experience, place F<sub>Z1</sub> at 10% LC filter

www.richtek.com

resonant frequency. Crossover frequency should be higher than the ESR zero but less than 1/5 of the switching frequency. The  $F_{P2}$  should be place at half the switching frequency.

Figure 8. Type 2 Bode Plot

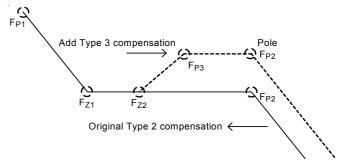

There is another type of compensation called Type 3 compensation that adds a pole-zero pair to the Type 2 network. It's used to compensate output capacitor whose ESR value is much lower (pure MLCC or OSCON Capacitors).

As shown in Figure 9, to insert a network between  $V_{OUT}$  and FB in the original Type 2 compensation network can result in Type 3 compensation. Figure 10 shows the difference of their AC response. Type 3 compensation has an additional pole-zero pair that causes a gain boost at the flat gain region. But the gain boosted is limited by the ratio (R1+R4)/R4; if R3 << R4.

Figure 9. Additional Network of Type 3 Compensation (Add between  $V_{\text{OUT}}$  and FB)

Figure 10. AC Response Curves of Type 2 and 3

Type 3 will induce additional one pole and one zero.

Zeros:

$$F_{Z2} = \frac{1}{2\pi \times (R1 + R3) \times C3}$$

Poles:

$$\mathsf{FP3} = \frac{1}{2\pi \times \mathsf{R3} \times \mathsf{C3}}$$

which is in the origin.

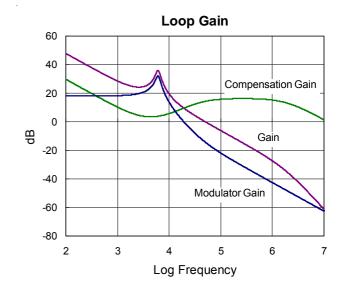

We recommend  $F_{Z1}$  placed in 0.5 x  $F_{P(LC)}$ ;  $F_{Z2}$  placed in  $F_{P(LC)}$ ;  $F_{P3}$  placed in  $F_{ESR}$  and  $F_{P2}$  placed in 0.5 x  $F_{SW}$ . Figure 11 shows Type 3 Bode Plot.

Figure 11. Type 3 Bode Plot

#### **Protection**

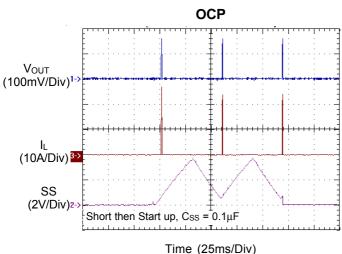

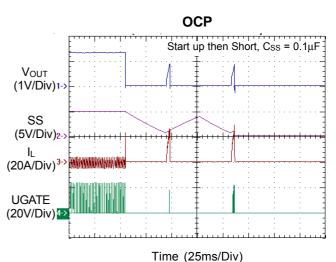

#### **OCP**

The RT8805 uses "Cycle by Cycle" current comparison. The over current level is set by IMAX pin. When OC function occurs and SS > 3.7V, a constant current of  $10\mu A$  starts to discharge the capacitor connected to SS pin right away. When OC occurs, UGATE and LGATE will be off.

When the voltage at the capacitor connected to SS pin pass about 0.4V, a constant current of  $10\mu A$  starts to charge the capacitor. The PWM signal is enabled to pass to the UGATE and LGATE. OCP function monitors both channels, either one can activate OCP. If the OC protection occurs three times, the chip will shut down and the state will only be released by POR.

RT8805 uses an external resistor  $R_{IMAX}$  to set a programmable over current trip point. OCP comparator compares each inductor current with this reference current. RT8805 uses hiccup mode to eliminate fault detection of OCP or reduce output current when output is shorted to ground. The OCP comparator compares the difference between  $I_X$  and  $I_{IMAX}$ .

For example:

From *Electrical Specifications* :  $R_{IMAX} = 33k\Omega$

$$\rightarrow$$

V<sub>PHASE</sub> = -220mV

Assume Low side MOSFET  $R_{DS(ON)} = 3m\Omega$ .

Get the OCP setting current is  $\frac{220\text{mV}}{3\text{m}\Omega}$ =73A per PHASE (the valley of inductor's current).

Change the setting current which you want from 73A per PHASE to 50A per PHASE.

Following below steps:

1. Calculate phase voltage. If Low side MOSFET

$$R_{DS(ON)} = 3m\Omega$$

,  $V_{PHASE new} = -150mV$ .

$$2.\,R_{IMAX\_new} = \frac{-220mV}{R_{DS(ON)}\;x\,Ioc} \times 33k\Omega$$

$R_{IMAX\_new} = 48.4k\Omega$

where loc is the over current value per phase.

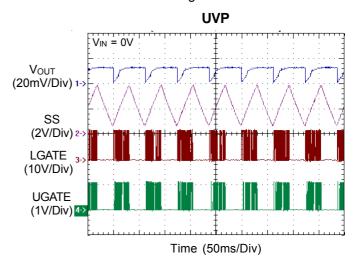

#### **UVP**

By detecting voltage at FB pin when SS > 3.7V. If FB < 0.6V, the chip will trigger the always Hiccup mode and a constant current source  $10\mu$ A starts to charge capacitor at SS pin when SS pass 0.4V and discharge Css when SS > 3.7V. As Figure 12 shown.

Figure 12. UVP (Always Hiccup Mode)

#### **General Design Guide**

This design guide is intended to provide a high-level explanation of the steps necessary to create a multi-phase power converter. It is assumed that the reader is familiar with many of the basic skills and techniques referenced below.

### **Power Stages**

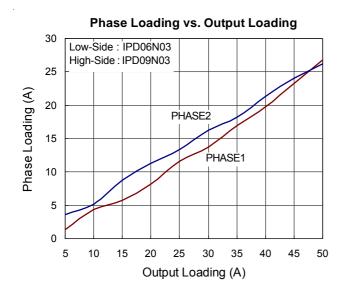

Designing a multi-phase converter is to determine the number of phases. This determination depends heavily on the cost analysis which in turn depends on system constraints that differ from one design to the next. Principally, the designer will be concerned with whether components can be mounted on both sides of the circuit board, whether through-hole components are permitted, the total board space available for power-supply circuitry, and the maximum amount of load current. Generally speaking, the most economical solutions are those in which each phase handles between 20 to 25 A (One Upper and one Lower MOSFET). All surface-mount designs will tend toward the lower end of this current range.

DS8805-04 May 2014

If through-hole MOSFETs and inductors can be used, higher per-phase currents are possible. In cases where board space is the limiting constraint, current can be pushed as high as 40A per phase, but these designs require heat sinks and forced air to cool the MOSFETs, inductors and heat dissipating surfaces.

#### **MOSFETs**

The choice of MOSFETs depends on the current each MOSFET will be required to conduct, the switching frequency, the capability of the MOSFETs to dissipate heat, and the availability and nature of heat sinking and air flow.

#### **Package Power Dissipation**

When choosing MOSFETs it is important to consider the amount of power being dissipated in the integrated drivers located in the controller. Since there are a total of two drivers in the controller package, the total power dissipated by both drivers must be less than the maximum allowable power dissipation for the VQFN package. Calculating the power dissipation in the drivers for a desired application is critical to ensure safe operation. Exceeding the maximum allowable power dissipation level will push the IC beyond the maximum recommended operating junction temperature of 125°C. The maximum allowable IC power dissipation for the 3x3 VQFN package is approximately 1.47W at room temperature.

According below equations at two phases operation, it's clear to describe that the junction temperature of the chip is directly proportional to the total C<sub>ISS</sub> (including C<sub>UGATE</sub> and C<sub>LGATE</sub>) of all external MOSFETs.

$$P_D = (C_{UGATE} \times V_{BOOT-PHASE}^2 \times f) + (C_{LGATE} \times V_{CC}^2 \times f) + \chi$$

$$T_J = T_A + (\theta_{JA} \times P_D)$$

( $\chi$  is the minor factor and could be ignored)

For example, according to the application we evaluated on board, the C<sub>UGATE</sub> = 1nF, C<sub>LGATE</sub> = 5nF (dual MOSFETs in parallel), V<sub>CC</sub> = 12V, V<sub>BOOT-PHASE</sub> = 12V, and operation frequency = 300kHz.

$P_D \approx 1 nF \times 12^2 \times 300 kHz + 2 \times 5 nF \times 12^2 \times 300 kHz =$ 475mW / PHASE

$T_J = 30^{\circ}C + 68^{\circ}C/W \times 0.475W \times 2 = 94.6^{\circ}C$

That means the junction temperature is most likely to be operated under the maximum (~125°C) operation rating.

#### **Layout Considerations**

Layout is very important in high frequency switching converter design. If designed improperly, the PCB could radiate excessive noise and contribute to the converter instability.

First, place the PWM power stage components. Mount all the power components and connections in the top layer with wide copper areas. The MOSFETs of Buck, inductor, and output capacitor should be as close to each other as possible. This can reduce the radiation of EMI due to the high frequency current loop. If the output capacitors are placed in parallel to reduce the ESR of capacitor, equal sharing ripple current should be considered. Place the input capacitor directly to the drain of high-side MOSFET. In multi-layer PCB, use one layer as power ground and have a separate control signal ground as the reference of the all signal. To avoid the signal ground is effect by noise and have best load regulation, it should be connected to the ground terminal of output. Furthermore, follows below guidelines can get better performance of IC:

- 1. A multi-layer printed circuit board is recommended.

- 2. Use a middle layer of the PC board as a ground plane and making all critical component ground connections through vias to this layer.

- 3. Use another solid layer as a power plane and break this plane into smaller islands of common voltage levels.

- 4. Keep the metal running from the PHASE terminal to the output inductor short.

- 5. Use copper filled polygons on the top and bottom circuit layers for the phase node.

- 6. The small signal wiring traces from the LGATE and UGATE pins to the MOSFET gates should be kept short and wide enough to easily handle the several Amperes of drive current.

- 7. The critical small signal components include any bypass capacitors, feedback components, and compensation components. Position those components close to their

- pins with a local GND connection, or via directly to the ground plane.

- 8.  $R_T$  and  $R_{IMAX}$  resistors should be near the  $R_T$  and  $R_{IMAX}$ pin respectively, and their GND return should be short, and kept away from the noisy MOSFET GND.

- 9. Place the compensation components close to the FB and COMP pins.

- 10. The feedback resistors for both regulators should also be located as close as possible to the relevant FB pin with vias tied straight to the ground plane as required.

- 11. Minimize the length of the connections between the input capacitors, C<sub>IN</sub> and the power switches by placing them nearby.

- 12. Position both the ceramic and bulk input capacitors as close to the upper MOSFET drain as possible, and make the GND returns (From the source of lower MOSFET to VIN, CVIN, GND) short.

- 13. Position the output inductor and output capacitors between the upper MOSFET and lower MOSFET and the load.

- 14. AGND should be on the clearer plane, and kept away from the noisy MOSFET GND.

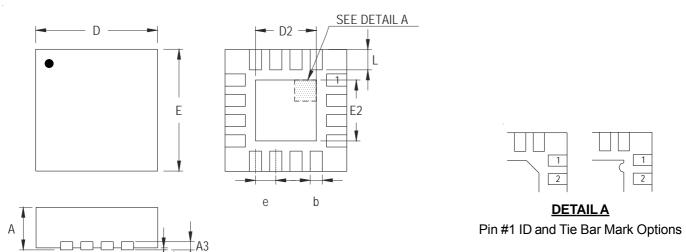

## **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Combal | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 0.800      | 1.000          | 0.031                | 0.039 |  |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300          | 0.007                | 0.012 |  |

| D      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| D2     | 1.300      | 1.750          | 0.051                | 0.069 |  |

| Е      | 2.950      | 3.050          | 0.116                | 0.120 |  |

| E2     | 1.300      | 1.750          | 0.051                | 0.069 |  |

| е      | 0.5        | 500            | 0.020                |       |  |

| L      | 0.350      | 0.450          | 0.014                | 0.018 |  |

V-Type 16L QFN 3x3 Package

**DETAIL A**Pin #1 ID and Tie Bar Mark Options

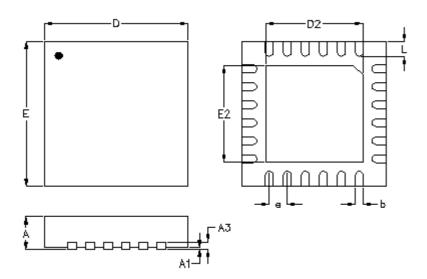

Note: The configuration of the Pin#1 identifier is optional, but must be located within the zone indicated.

| Symbol |          | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|----------|--------------|---------------|----------------------|-------|--|

|        |          | Min.         | Max.          | Min.                 | Max.  |  |

|        | Α        | 0.800        | 1.000         | 0.031                | 0.039 |  |

|        | A1       | 0.000        | 0.050         | 0.000                | 0.002 |  |

|        | A3       | 0.175        | 0.250         | 0.007                | 0.010 |  |

|        | b        | 0.180        | 0.300         | 0.007                | 0.012 |  |

|        | D        | 3.950        | 4.050         | 0.156                | 0.159 |  |

| D2     | Option 1 | 2.400        | 2.500         | 0.094                | 0.098 |  |

| DZ     | Option 2 | 2.650        | 2.750         | 0.104                | 0.108 |  |

|        | E        | 3.950        | 4.050         | 0.156                | 0.159 |  |

| E2     | Option 1 | 2.400        | 2.500         | 0.094                | 0.098 |  |

| L      | Option 2 | 2.650        | 2.750         | 0.104                | 0.108 |  |

|        | е        | 0.500        |               | 0.020                |       |  |

| L      |          | 0.350        | 0.450         | 0.014                | 0.018 |  |

V-Type 24L QFN 4x4 Package

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS8805-04 May 2014