# Tsi308™ HyperTransport to PCI/X User Manual

80D4000\_MA001\_04

September 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

# **Contents**

| Ab | out th | nis Doc   | cument                              | 13 |

|----|--------|-----------|-------------------------------------|----|

|    | Scop   | e         |                                     |    |

|    | Doci   | ıment Co  | onventions                          |    |

|    | Rela   | ted Infor | mation                              | 15 |

|    | Revi   | sion Hist | tory                                |    |

| 1. | Fun    | ctional   | I Description                       | 17 |

|    | 1.1    |           | iew                                 |    |

|    | 1.2    | Feature   | es                                  | 19 |

|    |        | 1.2.1     | General features                    | 19 |

|    | 1.3    | Hyper     | Transport Interface                 | 20 |

|    | 1.4    | PCI-X     | Interface.                          | 21 |

|    |        | 1.4.1     | PCI-X Master                        | 21 |

|    |        | 1.4.2     | PCI-X Slave                         |    |

|    |        | 1.4.3     | PCI-X Arbiter                       |    |

|    | 1.5    | Interru   | ıpt Controller                      |    |

|    | 1.6    | Interfa   | ice Levels                          | 23 |

|    | 1.7    | Clocki    | ing                                 | 24 |

|    | 1.8    | Reset .   |                                     | 24 |

| 2. | Inte   | rface C   | Operation                           |    |

|    | 2.2    | Hyper     | Transport Interface                 | 27 |

|    |        | 2.2.1     | HyperTransport Packet Reception     |    |

|    |        | 2.2.2     | HyperTransport Address Map          |    |

|    |        | 2.2.3     | HyperTransport Address Remap        |    |

|    |        | 2.2.4     | HyperTransport Packet Transmission  |    |

|    | 2.3    | Outbou    | und Transactions                    |    |

|    |        | 2.3.1     | PCI-X Outbound Transactions         |    |

|    | 2.4    | Inboun    | nd Transactions                     |    |

|    |        | 2.4.1     | PCI-X Address Map                   |    |

|    |        | 2.4.2     | PCI-X Posted Write Queue            | 37 |

|    |        | 2.4.3     | PCI-X Delayed/Split Request Buffers | 37 |

|    |        | 2.4.4     | Prefetching (PCI mode only)         |    |

|    |        | 2.4.5     | Memory Read Block (PCI-X mode only) |    |

|    |      | 2.4.6     | SrcTags                                               | 39 |

|----|------|-----------|-------------------------------------------------------|----|

|    |      | 2.4.7     | Sequences                                             | 39 |

|    |      | 2.4.8     | Read Responses                                        | 39 |

|    |      | 2.4.9     | Continuous Prefetching (PCI mode only)                | 40 |

|    |      | 2.4.10    | Transaction Disconnects                               | 40 |

|    |      | 2.4.11    | Outbound Data Buffer                                  | 40 |

|    |      | 2.4.12    | Interrupt Generation                                  | 40 |

|    | 2.5  | PCI-X A   | arbiter                                               | 41 |

|    | 2.6  | Online In | nsertion and Removal (OIR)                            | 42 |

|    | 2.7  | LDTST     | OP# Support                                           | 42 |

|    | 2.8  | Power N   | Management                                            | 43 |

|    | 2.9  | Reset     |                                                       | 43 |

|    |      | 2.9.1     | Cold Reset                                            | 43 |

|    |      | 2.9.2     | Warm Reset                                            | 43 |

|    |      | 2.9.3     | Reset Configuration                                   | 43 |

|    |      | 2.9.4     | HyperTransport Link Initialization                    | 43 |

|    |      | 2.9.5     | HyperTransport Fabric Initialization                  | 44 |

|    |      | 2.9.6     | Secondary Bus Reset                                   | 45 |

|    | 2.10 | Error Ha  | andling                                               | 45 |

|    |      | 2.10.1    | Reporting                                             | 45 |

|    |      | 2.10.2    | HyperTransport Errors                                 | 46 |

|    |      | 2.10.3    | PCI Errors                                            | 49 |

|    | 2.11 | Test Fea  | atures                                                | 52 |

|    |      | 2.11.1    | JTAG                                                  | 52 |

|    |      | 2.11.2    | SCAN and ATPG.                                        | 64 |

| 3. | Cloc | k Frequ   | ency and Mode Selection Hardware Straps               | 67 |

|    | 3.1  | Overviev  | w                                                     | 67 |

|    | 3.2  | Core Clo  | ock Frequency Selection in RevC mode                  | 69 |

|    | 3.3  | PCI Bus   | A Frequency Selection in RevC mode                    | 70 |

|    | 3.4  | PCI Bus   | B Frequency Selection in RevC mode                    | 70 |

|    | 3.5  | PCI Bus   | A and Core Clock Frequency Selection in non-RevC mode | 71 |

|    | 3.6  | PCI Bus   | B Frequency Selection in non-RevC mode                | 72 |

|    | 3.7  | Link Fre  | equency Selection (Tsi301 mode only)                  | 72 |

|    | 3.8  | Miscella  | neous Straps                                          | 74 |

|    |      |           |                                                       |    |

Contents

| 4. | Reg                        | ister D | escriptions                                   | 77  |  |

|----|----------------------------|---------|-----------------------------------------------|-----|--|

|    | 4.1                        | Config  | guration Registers                            | 78  |  |

|    |                            | 4.1.1   | Operating Modes                               | 78  |  |

|    |                            | 4.1.2   | Configuration Mechanism                       | 80  |  |

|    | 4.2                        | Summa   | ary of Configuration Registers                | 81  |  |

|    |                            | 4.2.1   | Register Access Definitions                   | 81  |  |

|    |                            | 4.2.2   | Register Access Rules                         | 81  |  |

|    |                            | 4.2.3   | Mode Encodings                                | 81  |  |

|    |                            | 4.2.4   | CSR Layout                                    | 82  |  |

|    | 4.3                        | 64-bit  | Address Remapping Capability Indices          | 85  |  |

|    |                            | 4.3.1   | ISOC Bit Setting                              | 85  |  |

|    |                            | 4.3.2   | Read Control 2 Register                       | 86  |  |

|    |                            | 4.3.3   | Interrupt Definition Registers                | 87  |  |

|    |                            | 4.3.4   | SRI Indices                                   | 89  |  |

|    |                            | 4.3.5   | Tsi308 Registers                              | 93  |  |

|    |                            | 4.3.6   | CSR Layout for IOAPIC                         | 177 |  |

|    |                            | 4.3.7   | IOAPIC Registers                              | 179 |  |

| 5. | Electrical Characteristics |         |                                               |     |  |

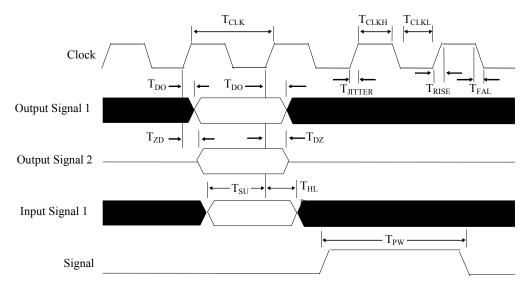

|    | 5.1                        | AC Tir  | ming Definitions                              | 184 |  |

|    |                            | 5.1.1   | AC Timing Values                              | 185 |  |

|    | 5.2                        | Clock   | Parameters                                    | 187 |  |

|    |                            | 5.2.1   | Input Clock                                   | 187 |  |

|    | -                          |         | Transport Output Timing Characteristics       | 188 |  |

|    |                            | 5.3.1   | Differential Output Skew                      | 188 |  |

|    |                            | 5.3.2   | TCADV (TCADValid)                             | 189 |  |

|    | 5.4                        | Hyper   | Transport Input Timing Characteristics        | 190 |  |

|    |                            | 5.4.1   | Input Differential Skew                       | 190 |  |

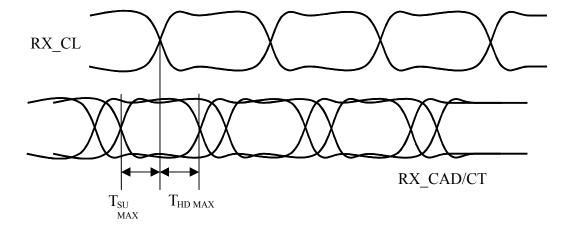

|    |                            | 5.4.2   | TSU and THD                                   | 191 |  |

|    | 5.5                        | Hyper   | Transport Interconnect Timing Characteristics | 192 |  |

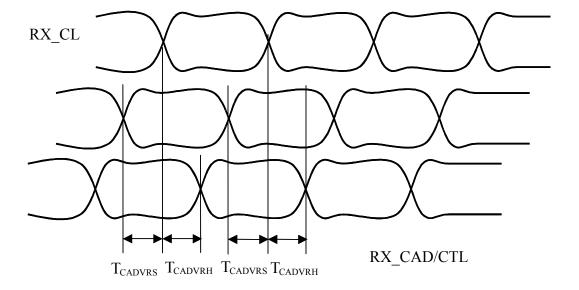

|    |                            | 5.5.1   | TCADVRS/RH                                    | 192 |  |

|    | 5.6                        | Hyper   | Transport Transfer Timing Characteristics     | 193 |  |

|    | 5.7                        | Hyper   | Transport Impedance Requirements              | 195 |  |

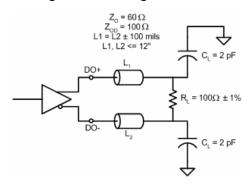

|    | 5.8                        | Hyper   | Transport Signal AC Specifications            | 196 |  |

|    | 5.9                        | Hyper   | Transport DC Electrical Characteristics       | 197 |  |

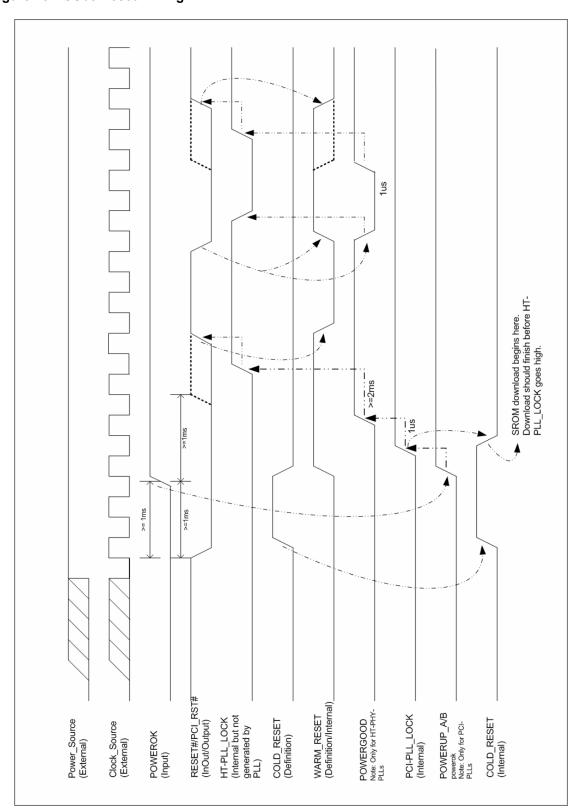

|    | 5.10                       | Reset   | Timing                                        | 198 |  |

|    | 5.11                       | Power   | Consumption                                   | 200 |  |

|    |                            |         |                                               |     |  |

|    | 5.12                 | Therma   | al Data                                           | 200 |  |  |

|----|----------------------|----------|---------------------------------------------------|-----|--|--|

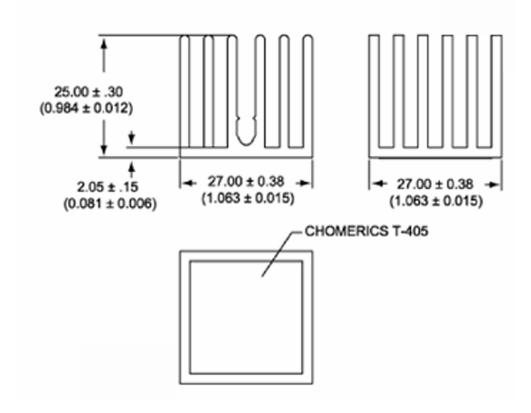

|    | 5.13                 | Therma   | al Recommendations                                | 201 |  |  |

|    | 5.14                 | Power    | Sequencing                                        | 202 |  |  |

|    | 5.15                 | Supply   | Operatiing Ranges                                 | 202 |  |  |

|    | 5.16                 | Absolu   | ite Maximum Ratings                               | 202 |  |  |

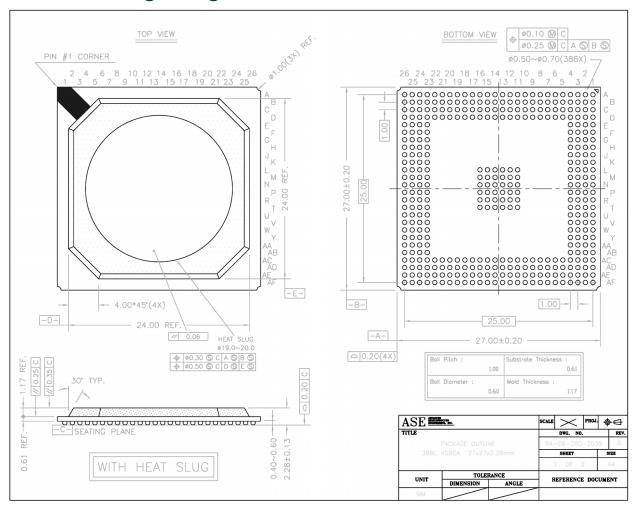

| 6. | Pacl                 | kaging   |                                                   | 203 |  |  |

|    | 6.1                  | Packag   | ge Specification                                  | 204 |  |  |

|    |                      | 6.1.1    | Pins Sorted by Name                               | 204 |  |  |

|    |                      | 6.1.2    | Pins Sorted by Number                             | 215 |  |  |

|    |                      | 6.1.3    | Multiplexed Pins                                  | 226 |  |  |

|    |                      | 6.1.4    | Power Pins                                        | 226 |  |  |

|    |                      | 6.1.5    | Ground Pins                                       | 230 |  |  |

|    | 6.2                  | Packag   | ge Diagram                                        | 232 |  |  |

|    |                      | 6.2.1    | Package Handling Procedures                       | 232 |  |  |

| Α. | Onli                 | ne Inse  | ertion and Removal                                | 233 |  |  |

|    | A.1                  | Overvi   | ew                                                | 233 |  |  |

|    | A.2                  | Insertic | on and Removal Sequence                           | 233 |  |  |

| В. | Typical Applications |          |                                                   |     |  |  |

|    | B.1                  | Recom    | mendations for Use                                | 235 |  |  |

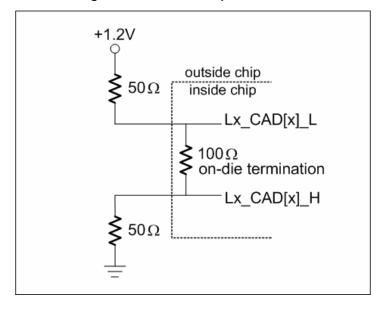

|    |                      | B.1.1    | Unused HyperTransport CAD, CLK, and CTL Inputs    | 235 |  |  |

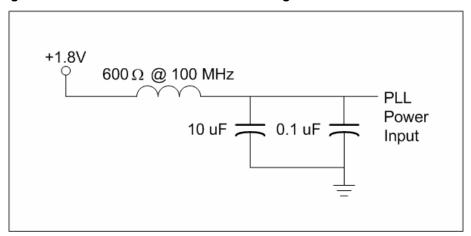

|    |                      | B.1.2    | Analog PLL Power Filtering                        | 236 |  |  |

|    |                      | B.1.3    | Decoupling Capacitor Recommendations              | 237 |  |  |

|    | B.2                  | PCB L    | ayout Guidelines                                  | 237 |  |  |

|    |                      | B.2.1    | Tsi308 HyperTransport Interface Layout Guidelines | 237 |  |  |

|    |                      | B.2.2    | Layout Guidelines                                 | 239 |  |  |

|    |                      | B.2.3    | AS90L10208 Board Trace Electrical Specification   | 239 |  |  |

|    |                      | B.2.4    | Routing Rules for Individual Signal Groups        | 240 |  |  |

|    | B.3                  | Power    | Distribution                                      | 243 |  |  |

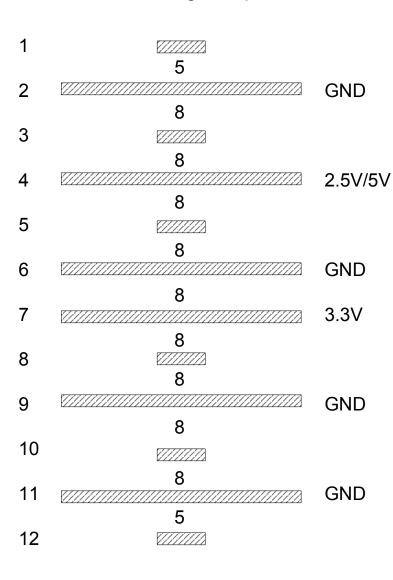

|    |                      | B.3.1    | Number of Layers                                  | 243 |  |  |

|    |                      | B.3.2    | VLDT Layout                                       | 243 |  |  |

|    |                      | B.3.3    | Decoupling                                        | 244 |  |  |

|    |                      | B.3.4    | Bulk Decoupling.                                  | 244 |  |  |

|    |                      | B.3.5    | Multiple HyperTransport Links                     | 244 |  |  |

|    | B.4                  | AS90L    | L10208 Die Pad-to-Ball Trace Length Information   | 245 |  |  |

|    | B.5                  | Examp    | ole PCB Stackup for HyperTransport                | 248 |  |  |

| Contents |  |  |

|----------|--|--|

|          |  |  |

8 Contents

# **List of Tables**

| Table 1:  | HyperTransport PCI-X Bridge Interface Voltages            | 23  |

|-----------|-----------------------------------------------------------|-----|

| Table 2:  | HyperTransport Ordering                                   | 30  |

| Table 3:  | PCI Bus Transaction Ordering                              | 31  |

| Table 4:  | PCI-X Bus Transaction Ordering                            | 31  |

| Table 5:  | HyperTransport Link Error CSR Bits                        | 47  |

| Table 6:  | HyperTransport Forwarding Error CSR Bits                  | 47  |

| Table 7:  | HyperTransport Master Errors CSR Bits                     | 49  |

| Table 8:  | PCI System Error CSR Bits.                                | 50  |

| Table 9:  | PCI Master Errors CSR Bits                                | 50  |

| Table 10: | PCI Parity Errors CSR Bits                                | 52  |

| Table 11: | Boundary Scan Chain Order                                 | 54  |

| Table 12: | Scan Input and Output Pins                                | 64  |

| Table 13: | Core Clock Frequency Selection Straps in RevC mode        | 69  |

| Table 14: | PCI-A Clock Frequency Selection Straps in RevC mode       | 70  |

| Table 15: | PCI-B Clock Frequency Selection Straps                    | 70  |

| Table 16: | P0_CLK and CoreClock Frequency Selection Straps           | 71  |

| Table 17: | P1_CLK Frequency Selection Straps                         | 72  |

| Table 18: | Link Transmit Clock Frequency Selection Straps.           | 72  |

| Table 19: | Miscellaneous Pin Straps.                                 | 74  |

| Table 20: | Tsi308 CSR Header.                                        | 82  |

| Table 21: | 64-bit Address Remap Indexed Registers                    | 85  |

| Table 22: | Interrupt Definition Registers                            | 87  |

| Table 23: | AC Timing Definitions                                     | 184 |

| Table 24: | Typical AC Timing Values                                  | 185 |

| Table 25: | Input Clock Parameters                                    | 187 |

| Table 26: | HyperTransport Link Transfer Timing Specifications        | 193 |

| Table 27: | RTT and RON DC Specifications.                            | 195 |

| Table 28: | HyperTransport Link Differential Signal AC Specifications | 196 |

| Table 29: | HT Link Differential Signal DC Specifications             | 197 |

| Table 30: | Recommended Operating Temperature.                        | 200 |

| Table 31: | Thermal Maximum                                           | 200 |

| Table 32: | Thermal Characteristics.                                  | 200 |

| Table 33: | Supply Operating Ranges                                   | 202 |

10 List of Tables

| Table 34: | Absolute Maximum Ratings                                 | 202 |

|-----------|----------------------------------------------------------|-----|

| Table 35: | Tsi308 Sorted by Name                                    | 204 |

| Table 36: | Tsi308 Sorted by Number                                  | 215 |

| Table 37: | Tsi308 Multiplexed Pins                                  | 226 |

| Table 38: | Tsi308 +1.2V HyperTransport Power                        | 226 |

| Table 39: | Tsi308 +1.8V Core Power                                  |     |

| Table 40: | Tsi308 1.8V Analog PLL Power and Ground                  | 228 |

| Table 41: | Tsi308 +3.3V PCI Core and I/O Power and HT Receive Power | 228 |

| Table 42: | Tsi308 Ground Pins                                       | 230 |

| Table 43: | System Board Design Rules.                               | 240 |

| Table 44: | Pad-to-Ball Trace Length Information                     | 245 |

| Table 45  | Ordering Information                                     | 251 |

# **List of Figures**

| Figure 1:  | Tsi308 Block Diagram                               | 18  |

|------------|----------------------------------------------------|-----|

| Figure 2:  | Block Diagram                                      | 26  |

| Figure 3:  | Single HyperTransport Link Interface Block Diagram | 27  |

| Figure 4:  | Primary clock inputs to Tsi308 PLLs                | 68  |

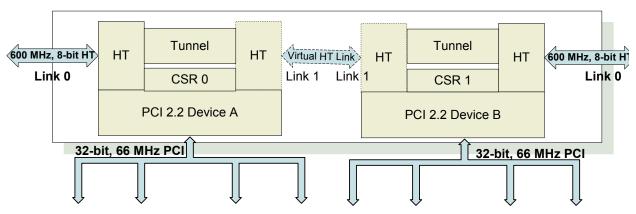

| Figure 5:  | Single Tsi301 Mode                                 | 78  |

| Figure 6:  | Dual Tsi301 Mode                                   | 79  |

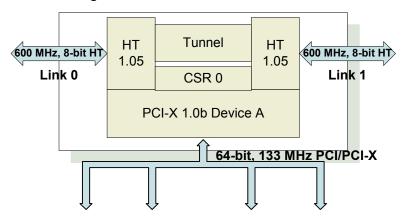

| Figure 7:  | Tsi308 Single PCI-X Mode                           | 80  |

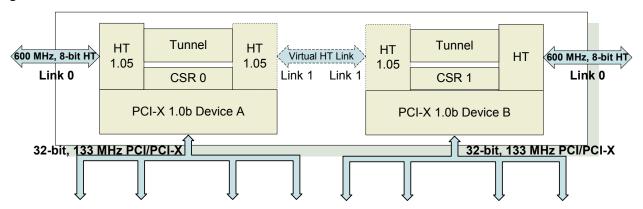

| Figure 8:  | Tsi308 Dual PCI-X Mode                             | 80  |

| Figure 9:  | Timing Definitions Waveform                        | 184 |

| Figure 10: | Input Clock Parameters Waveform                    | 187 |

| Figure 11: | TODIFF                                             | 188 |

| Figure 12: | TCADV                                              | 189 |

| Figure 13: | TIDIFF                                             | 190 |

| Figure 14: | TSU and THD                                        | 191 |

| Figure 15: | TCADVRS / TCADVRH                                  | 192 |

| Figure 16: | Output Loading for AC Timing.                      | 196 |

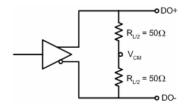

| Figure 17: | Output Reference System Load.                      | 197 |

| Figure 18: | Tsi308 Reset Timing                                | 199 |

| Figure 19: | Recommended Heat Sink for Tsi308                   | 201 |

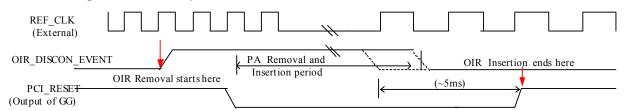

| Figure 20: | OIR Sequence                                       | 234 |

| Figure 21: | Terminating Unused HT CAD Inputs                   | 236 |

| Figure 22: | Recommended PLL Power Filtering.                   | 236 |

| Figure 23: | PCB Stackup for HyperTransport                     | 249 |

12 List of Figures

# **About this Document**

This section discusses general document information about the *Tsi308 HyperTransport to PCI/X User Manual*. The following topics are described:

- "Scope" on page 13

- "Document Conventions" on page 13

- "Related Information" on page 15

- "Revision History" on page 15

# Scope

The *Tsi308 HyperTransport to PCI/X User Manual* discusses the features, capabilities, and configuration requirements for the Tsi308. It is intended for hardware and software engineers who are designing system interconnect applications with these devices.

# **Document Conventions**

This document uses a variety of conventions to establish consistency and to help you quickly locate information of interest. These conventions are briefly discussed in the following sections.

# **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "n". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |  |

|-------------|--------------------|-------------------|--|

| Active low  | NAMEn              | NAMEn[3]          |  |

| Active high | NAME               | NAME[3]           |  |

#### **Object Size Notation**

This document uses the following object size notation:

- A byte is an 8-bit object.

- A word is a 16-bit object.

- A *doubleword* (Dword) is a 32-bit object.

#### **Numeric Notation**

- Hexadecimal numbers are denoted by the prefix 0x. For example, 0x04.

- Binary numbers are denoted by the prefix 0b. For example, 0b010.

- Registers that have multiple iterations are denoted by {x..y} in their names; where x is first register and address, and y is the last register and address. For example, REG{0..3} indicates there are four versions of the register at different addresses: REG0, REG1, REG2, and REG3.

#### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

#### **Document Status Information**

User manuals are classified as Advance, Preliminary, or Final:

- Advance Contains information that is subject to change, and is available once prototypes are released to customers.

- Preliminary Contains information about a product that is near production-ready, and is revised as required.

- Final Contains information about a final, customer-ready product, and is available once the product is released to production.

## **Related Information**

The following documents contain useful reference information for using this manual:

• Tsi308 Device Errata and Design Notes

# **Revision History**

#### 80D4000\_MA001\_04, Formal, September 2009

This document was rebranded as IDT. It does not include any technical changes.

## 80D4000\_MA001\_03, Preliminary, January 2007

This is the current release of the user manual. There have been slight modifications throughout the manual.

16

# 1. Functional Description

This chapter discusses the following topics about the Tsi308:

- "Overview" on page 18

- "Features" on page 19

- "HyperTransport Interface" on page 20

- "PCI-X Interface" on page 21

- "Interrupt Controller" on page 23

- "Interface Levels" on page 23

- "Clocking" on page 24

- "Reset" on page 24

## 1.1 Overview

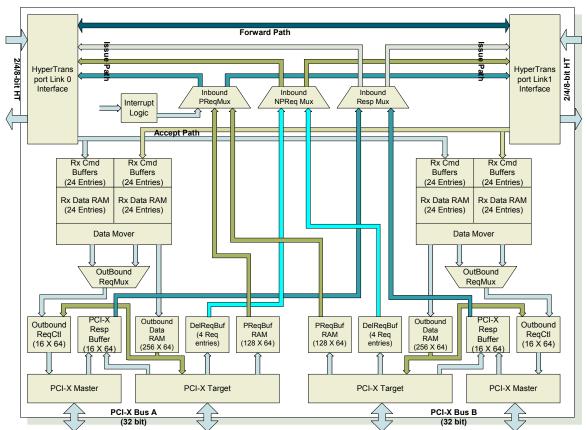

The Tsi308 is HyperTransport<sup>™</sup>-to-PCI-X Bridge that interfaces the new generation of HT based microprocessors and micro controllers to PCI or PCI-X based peripherals. It also connects HT based hosts to HT based peripherals.

The Tsi308 can be configured to support either single 64-bit PCI-X bus or two 32-bit PCI-X buses. The Tsi308 implements two bi-directional 8-bit HyperTransport™ interfaces that provide 1200 MByte per second of bandwidth in each direction. Up to 31 devices can be daisy-chained to build higher capacity systems with multiple PCI-X busses and HT based peripherals. A fairness algorithm allocates bandwidth among devices, thereby eliminating starvation of bridges at the end of the chain.

The Tsi308 breathes new life into systems that are encumbered by the limits of traditional PCI or PCI-X based fabrics. It reduces the time to market, design complexity and system costs of PCI-X and HT based systems.

The block diagram for Tsi308 is shown Figure 1 on page 18.

Figure 1: Tsi308 Block Diagram

1. Functional Description

## 1.2 Features

The following sections describe the features of Tsi308.

#### 1.2.1 General features

- Two Bidirectional 8-bit HyperTransport™ interfaces

- Up to 600MHz DDR (Double Data Rate) for peak bandwidth of 1200 MB/s simultaneously in each direction

- Complies with Revision 1.05 of HyperTransport™ I/O Link Specification

- Maximum link width supported is only 8-bits

- Supports asymmetric link widths and frequencies

- Tunnels between the two HyperTransport<sup>™</sup> interfaces

- Can be configured as single-ended cave device with only one link active

- The HT interfaces support double hosted chain (Host CPU on each port)

- Single 64-bit PCI-X bus or two 32-bit PCI-X buses

- Device emulates two HT link devices (with virtual internal tunnel in dual PCI-X mode)

- Implements two independent sets of CSRs in dual PCI-X mode

- PCI-X bus can also operate in traditional PCI mode

- Operating frequencies and mode of the two PCI-X buses are independently selectable

- Supports 50, 66, 100 and 133 MHZ in PCI-X mode

- Supports 25, 33, 50 and 66 MHZ in PCI mode

- PCI-X mode complies to Revision 1.0b of PCI-X Addendum to the PCI Local Bus Specification

- PCI mode complies to Revision 2.2 of PCI Local Bus Specification

- Supports Tsi301 software backward compatibility mode through hardware strap setting

- Supports daisy-chaining up to 31 devices. The bandwidth is shared among the devices using a fairness algorithm

- Programmable interrupt controller with up to 10 interrupts per PCI-X port

- Built-in 2-level PCI-X arbiter with support for up to 6 devices

- Also supports external arbiter

- Transaction forwarding for the following commands

- All I/O and memory commands

- Type 1 to Type 1 configuration commands (downstream only)

- o Type 1 to Type 0 configuration commands (downstream only)

- Internal buffers to support high-speed operation, including:

- 1536-bytes HT forwarding (512 bytes each for posted, non-posted and response)

- Following buffers are supported for each PCI-X port

- 1024-bytes upstream write (posted)

- 2048-bytes upstream read (non-posted), among up to four outstanding requests

- 512-bytes downstream write (posted)

- 512-bytes downstream read (non-posted)

- 64-bit memory mapped space and 25-bit I/O space

- 64-bit Address Remapping (downstream) and one DMA Window (upstream)

- Full UnitID Clumping support

- Supports 64-bit Address Extension

- Evaluation board available with firmware and software drivers

- 6 Watt max, 1.8V core, 1.2V HT I/O, 3.3V PCI I/O

- Optional 5V tolerant PCI I/O in standard PCI mode while operating at 25 or 33 MHZ

- 388-pin HSBGA package

- Compatible with x86 systems

- Supports Online Insertion and Removal

- Supports Boundary scan

- Software and Hardware compatibility Revision A & Revision B

# 1.3 HyperTransport Interface

The Tsi308 HyperTransport-to-PCI-X bridge primary interface is a HyperTransport tunnel. The primary interface is compliant with HyperTransport™ I/O Link Specification, Revision 1.05. The interface contains two HyperTransport links, which allow the connection of multiple bridge, chips in a daisy-chain configuration. As shown in the figure above Tsi308 can be configured to behave as two independent tunnel devices that are connected through a virtual internal tunnel. In this mode each tunnel device can host a 32-bit PCI-X bus. The programming in this mode is pretty much transparent to software in a way that software treats them as if they are independent devices or chips.

Each HyperTransport link has an 8-bit DDR transmit and an 8-bit DDR receive port running at clock speeds up to 600 MHz, allowing for raw bandwidth of 1200 MB/s simultaneously in each direction.

1. Functional Description

- For testing or connection to slower devices, the Tsi308 may be programmed to operate at slower link clock rates

- The Tsi308 supports both the synchronous and asynchronous modes of link initialization

#### 1.4 PCI-X Interface

The Tsi308 secondary interface is a 64-bit, 133 MHz capable PCI-X bus that can be configured to have two completely independent 32-bit buses in split bus mode including buffer space and transaction handling. The two PCI-X ports are identical in split bus mode and the subsequent description applies to each port. The PCI-X interface can operate at 50, 66, 100 and 133 MHz, which can also operate at 25, 33, 50 and 66 MHz while operating in traditional PCI mode. Additionally PCI-X bus can be configured for compatibility with 3.3V or 5.0V operation while operating at up to 33 MHz in traditional PCI mode. At higher frequencies of PCI or while in PCI-X mode only 3.3V is supported.

The Tsi308 supports the full 64-bit memory-mapped space and 25-bit I/O space described in HyperTransport<sup>TM</sup> I/O Link Specification, Revision 1.05. In addition device supports 64-bit address remapping capability and a single upstream DMA window. PCI dual address cycle (DAC) support is provided both inbound and outbound to support memory-mapped space.

- The Tsi308 supports configuration accesses to devices 0-15, using Address/Data bits 16-31 for IDSEL#.

- The Tsi308 implements all parity and error checking features described in *PCI Local Bus Specification, Revision 2.2*.

#### 1.4.1 PCI-X Master

As a PCI-X master, the Tsi308 chip can generate MemRd, MemWr, ConfigRd and ConfigWr cycles.

- The Tsi308 does not implement a cacheline size register and does not prefetch to PCI, so it never generates MemRdLine, MemRdMult or MemWrInv cycles.

- The Tsi308 does generate *Memory Read Block* but does not generate *Memory Write Block* cycles in PCI-X mode

- The Tsi308 does not support a Southbridge connection to PCI bus, so it never generates INTA cycles.

- The Tsi308 does not support burst I/O and burst Configuration cycles initiated from Host. These transactions are target aborted inside the chip and does not appear on the PCI-X bus.

PCI-X master cycles that are retried or disconnected on the PCI-X bus are reissued locally by the Tsi308 until they complete. The Tsi308 can track up to two outstanding requests in the Outbound Request Controller, of which one is reserved for posted requests. The other one is used for either posted or non-posted. The reserved posted buffer allows the passage of posted requests in case of blockage of non-posted requests.

In addition to two request-tracking buffers, Tsi308's PCI-X port has 512 byte buffer spaces each for posted and non-posted requests.

#### 1.4.2 PCI-X Slave

As a PCI-X slave, the Tsi308 can respond to all types of memory and I/O cycles. However, the Tsi308 never responds to PCI-X configuration cycles.

- The Tsi308 employs medium DEVSEL# timing.

- All PCI-X slave writes are posted excluding I/O writes which is non-posted.

- A total of 1024 bytes of buffering is provided on chip for posted requests

- All PCI-X slave reads are implemented as delayed requests (PCI) or split (PCI-X), with up to four requests outstanding at once and a maximum of 512 byte buffering is provided for each outstanding request to store the response data received from HT.

- Fast back to back transactions are supported.

Prefetching is supported for all flavors of memory read cycle while operating in standard PCI mode, which separate prefetch controls for each cycle type and a maximum prefetch per read of 512 bytes. Prefetching may be done once at the beginning of each read, or it may be enabled to continuously issue requests as data is drained to PCI. All prefetch data is discarded when the read disconnects on the PCI bus. The bridge chip provides buffer space for a total of 2048 bytes of read prefetch data per PCI-X port.

While operating in PCI-X mode, Tsi308 fetches only enough bytes to satisfy the byte count field that appears in the attribute phase of all PCI-X burst transactions. The Tsi308 can support any sized request up to 4096 bytes as specified in [2]. However since Tsi308 has only 512-byte buffer to store the read data per request, it will continue to fetch data from HyperTransport as the buffer is drained on to PCI-X in chunks of single ADB.

#### 1.4.3 PCI-X Arbiter

The Tsi308 implements an on-chip PCI Arbiter with 6 request/grant pairs. The request/grant pairs include a high-priority set for the on-chip PCI master, and five symmetrical sets for external device use.

All connections to the arbiter are through external pins, to use internal arbiter user has to route request/grant outputs back into chip connecting to any of the six request/grant pairs. So Tsi308 can automatically be configured to interface to external arbiter.

# 1. Functional Description

# 1.5 Interrupt Controller

The Tsi308 implements a HyperTransport interrupt controller. It supports 10 external interrupt sources per PCI port. To program interrupts Tsi308 implements *Interrupt Discovery and Configuration Capability Block* and associated *Interrupt Definition Registers* for each interrupt source. Each interrupt can independently be enabled and programmed to be level or edge-triggered and active high or low. In order for to be software compatible to previous generation Tsi301 chip, Tsi308 also implements an alternate register map to program the interrupts in a non-standard way. However these registers are visible to software only when Tsi308 is operating in Tsi301 software compatible mode by hardware strap settings and this is the only means to program interrupts in Tsi301 mode.

#### 1.6 Interface Levels

A complete pinout of the Tsi308 is provided in the *Signals Chapter*. The grouping of signal types is shown in Table 1.

Table 1: HyperTransport PCI-X Bridge Interface Voltages

| Interface      | Group | Voltages                                                                                        |

|----------------|-------|-------------------------------------------------------------------------------------------------|

| PCI/PCI-X      | PCI   | 3.3 V, 5.0 V tolerant (while operating in standard PCI mode at or below 33 MHz clock frequency) |

| HyperTransport | HT    | Differential, 600 mV swing, centered on 600 mV                                                  |

| Interrupts     | MISC  | 1.8 V                                                                                           |

| Miscellaneous  | MISC  | 1.8 V                                                                                           |

# 1.7 Clocking

During functional operation, the Tsi308's reference clocks (P0 CLK and P1 CLK) come from respective PCI-X bus clocks. These clocks are received from same sources that drive clocks to devices on the bridge's PCI-X buses and are nominally in phase with them; although they may be delayed relative to other PCI-X bus clocks. The P1 CLK is only used to clock the PCI-X interface logic of second PCI-X port (PCI B) while the device is operating in split bus mode. The reference clock frequencies and bus mode (traditional PCI or PCI-X) are indicated by Px M66EN, Px PCIX N and Px 133 N input pins where x denotes PCI-X bus (0 for PCI A and 1 for PCI B). The Px PCIX N and Px 133 N are normal TTL level signals derived from standard 3-state add-in card connector pin PCIXCAP. Since Tsi308 does not decode PCIXCAP, user has to implement an external three-level Comparator circuitry to generate Px PCIX N and Px 133 N. A reference circuit can be found in [3]. Though three pins above indicate operating mode (PCI or PCI-X) and frequency group (33MHz or 66 MHz or 133 MHz), Tsi308 needs exact operating frequency of a given bus to generate internal clocks as well as to generate PCI-X Initialization Pattern for devices on PCI-X bus as specified in [3]. This is done through hardware straps. These straps are sampled using combinational logic while warm/cold reset is in progress and used to combinationally generate PCI-X initialization pattern that is sampled by devices on PCI-X bus at the rising edge of PCI reset. Refer Chapter 4 for more details on Clocking and Hardware strap settings.

#### 1.8 Reset

All the internal resets of Tsi308 and resets for secondary PCI-X ports are derived from HyperTransport PWROK and RESET# signals. The combination of these two signals defines ColdReset and WarmReset windows on HyperTransport chain. While PWROK is implemented as input-only, RESET# is implemented as in-out in Tsi308. The asserted state of RESET# is stretched by Tsi308 and released after internal PLLs are locked. The PCI-X and CORE PLLs are only reset upon ColdReset but WarmReset resets HyperTransport PLLs. This way software could re-program link frequencies and issue WarmReset for new frequencies to take effect.

# 2. Interface Operation

This chapter discusses the following topics about the Tsi308:

- "Overview" on page 25

- "HyperTransport Interface" on page 27

- "Outbound Transactions" on page 34

- "Inbound Transactions" on page 36

- "PCI-X Arbiter" on page 41

- "Online Insertion and Removal (OIR)" on page 42

- "LDTSTOP# Support" on page 42

- "Power Management" on page 43

- "Reset" on page 43

- "Error Handling" on page 45

- "Test Features" on page 52

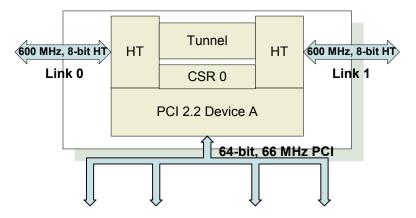

# 2.1 Overview

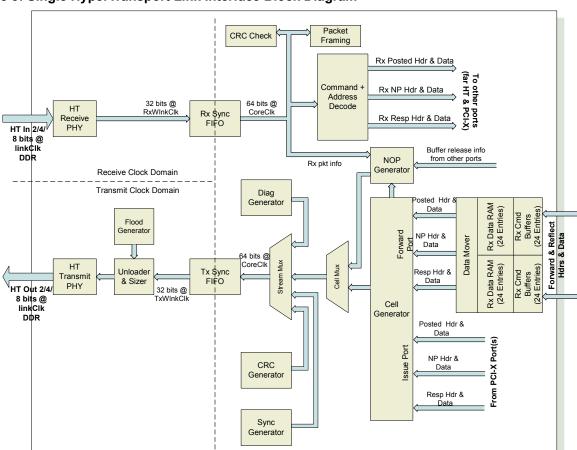

This chapter details the operation of the HyperTransport-to- PCI-X Bridge chip.

26 2. Interface Operation

Figure 2: Block Diagram

2. Interface Operation

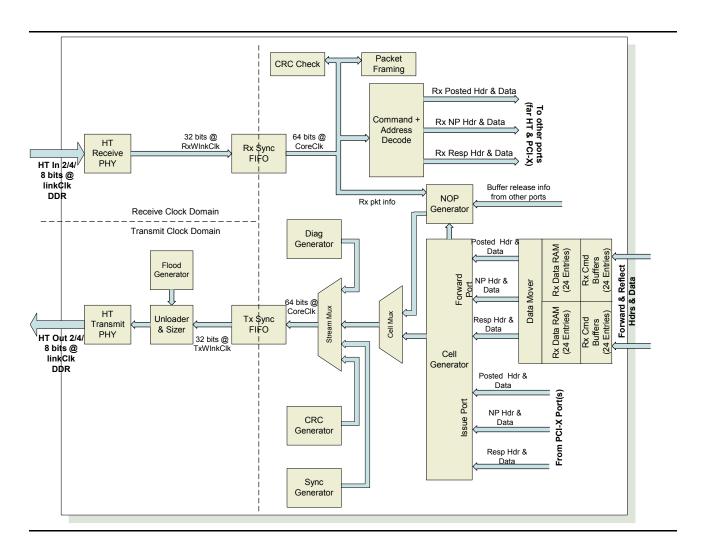

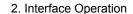

# 2.2 HyperTransport Interface

The Tsi308 HyperTransport interface consists of two identical link interfaces, each with a HyperTransport transmitter and receiver. Some central reset and error-handling logic is shared between the two links.

In the HyperTransport protocol, all logical packet transfer is between HyperTransport slaves and the host. Direct peer-to-peer communication is not allowed. To support peer-to-peer operations, packets are reflected through the host. Packets issued from the host to a HyperTransport slave are defined to travel downstream on the HyperTransport chain. Packets issued from a HyperTransport slave to the host are defined to travel upstream. Intermediate nodes in the daisy chain forward packets from link to link until they reach their final destination, which accepts the packet.

Link interfaces in the Tsi308 are symmetrical, which allows connection to either bridge link toward a host. The Tsi308 also supports being placed in a double-hosted chain with hosts on both ends.

Figure 3: Single HyperTransport Link Interface Block Diagram

28 2. Interface Operation

# 2.2.1 HyperTransport Packet Reception

Packets received from a HyperTransport link are decoded and routed to appropriate destination port where they are stored in Receive (Rx) buffers for subsequent transmission. HyperTransport flow control algorithm guarantees that no packet is received without buffer space to store it. Packet contents are divided into command information (including address) and data, with separate buffers for each.

For packets arriving from HT Links, each destination port (forward HT Link, PCI\_A and PCI\_B) has dedicated command and data buffers for two possible source ports (Both HT links could source data to any of the two PCI-X ports and each of the two HT Link Ports can receive forwarded data from other HT Link Port and reflected traffic) statically partitioned among the three virtual channels (posted, non-posted and response), with each channel allocated space to hold eight commands and eight data packets. However packets originated on PCI-X bus is locally buffered in respective PCI-X Ports and delivered directly to the appropriate HT Link.

2. Interface Operation

#### 2.2.1.1 Packet Decode

As packets arrive from a HT link, the associated commands and addresses are decoded to determine if the Tsi308 is the packet target on HyperTransport chain and routed to the appropriate port where they are locally stored. Packets are checked in the destination port for ordering collisions against other packets resident in the buffers. The decode and collision results are stored in the buffers with the packets. The packet routing is as follows:

- Packets received on the HyperTransport interface may be routed to internal logic (CSRs), including PCI-X interfaces. This is "accepting" a packet.

- Packets may also be routed to the other HyperTransport link interface for transmission to the next device in the chain. This is "forwarding" a packet.

- A particular packet may be accepted, forwarded, or both.

The Tsi308 HyperTransport packet decode first determines whether the incoming packet is traveling upstream or downstream. This determination is based on the packet source information contained in the packet itself, not on which link is the upstream or downstream link.

- Upstream packets are always forwarded toward the host and are never accepted by the Tsi308 chip.

- Downstream RdSized and WrSized request packet addresses are decoded according to the HyperTransport Address Map described in Section 3.3 and are accepted if they match any Tsi308 address ranges of any PCI-X ports or internal CSRs.

- Downstream WrSized and RdSized that do not match any of the Tsi308 address ranges are forwarded to the next device in the chain.

- Broadcast request addresses are also decoded and accepted if they match a Tsi308 address range. However, these packets are also always forwarded.

- Fence and Flush requests are never accepted by Tsi308 and are always forwarded.

- Downstream response packets are accepted if their UnitID field matches the value in the BaseUnitID field of any of the Tsi308 LdtCmd register; otherwise, they are forwarded.

#### 2.2.1.2 Collision Checking and Ordering

Collision checking is performed according to the HyperTransport protocol to determine if incoming packets are required to stay ordered behind packets already in the Rx buffers. Only packets headed to the same accept or forward destination may have ordering requirements. If a packet has an ordering collision, it may not be issued from the Rx buffers until the packet with which it collided has both been issued and reached an appropriate commit point to guarantee ordering. This ordering point varies by destination.

30 2. Interface Operation

Because the Outbound Request Controller (ORC) can reorder requests, requests accepted by the Tsi308 may not be committed until they are retired by ORC. For accesses to PCI-X bus, this means that the request reached the PCI-X bus and all data was transferred. Packets forwarded from one link to the other are either streamed – meaning that the transmission may start before the whole packet is received or a complete packet is first stored and then forwarded, avoiding possible "holes" on transmitting link if transmitting link bandwidth (link frequency \* link width) is an order faster than that of receiving link. Since there is no specification defined way to determine the bandwidth of receiving link, Tsi308 implements a proprietary control bit (StoreForward) per link in its CSR which system software can program that tells the Tsi308 whether to stream (low latency) or not. It is the Rx Command Buffer's responsibility to ensure that required packet ordering is maintained so packets can be committed as soon as they are passed to the link controller.

Packets that do not have any ordering requirements may leave the Rx buffers in a different order than they reached them, both among and within virtual channels. In general, Rx buffers select a packet choosing the oldest non-blocked packet in each channel to a given destination.

#### HyperTransport Ordering

The Table 2 lists ordering implemented in Tsi308 for packets issued from PCI/PCI-X to HyperTransport link and for packets forwarded from one HT link to other HT link.

Table 2: HyperTransport Ordering

| Row Pass Column    | Posted Request | Non-posted Request | Response |

|--------------------|----------------|--------------------|----------|

| Posted Request     | No             | Yes                | Yes      |

| Non-posted Request | No             | No                 | No       |

| Response           | No             | Yes                | No       |

2. Interface Operation

#### **PCI Ordering**

The Table 3 lists the ordering implemented in Tsi308 for packets traveling to PCI from HT interface.

**Table 3: PCI Bus Transaction Ordering**

| Row Pass<br>Column? | Posted Memory<br>Write (PMW) | Delayed Read<br>Request (DRR) | Delayed Write<br>Request (DWR) | Delayed Read<br>Completion<br>(DRC) | Delayed Write<br>Completion<br>(DWC) |

|---------------------|------------------------------|-------------------------------|--------------------------------|-------------------------------------|--------------------------------------|

| PMW                 | No                           | Yes                           | Yes                            | Yes                                 | Yes                                  |

| DRR                 | No                           | No                            | No                             | No                                  | No                                   |

| DWR                 | No                           | No                            | No                             | No                                  | No                                   |

| DRC                 | No                           | Yes                           | Yes                            | No                                  | No                                   |

| DWC                 | No                           | Yes                           | Yes                            | No                                  | No                                   |

#### **PCI-X Ordering**

The Table 3 lists the ordering implemented in Tsi308 for packets traveling to PCI-X from HT interface.

**Table 4: PCI-X Bus Transaction Ordering**

| Row Pass<br>Column? | Posted Memory<br>Write (PMW) | Split Read<br>Request (SRR) | Split Write<br>Request (SWR) | Split Read<br>Completion<br>(SRC) | Split Write<br>Completion<br>(SWC) |

|---------------------|------------------------------|-----------------------------|------------------------------|-----------------------------------|------------------------------------|

| PMW                 | No                           | Yes                         | Yes                          | Yes                               | Yes                                |

| SRR                 | No                           | No                          | No                           | No                                | No                                 |

| SWR                 | No                           | No                          | No                           | No                                | No                                 |

| SRC                 | No                           | Yes                         | Yes                          | No                                | No                                 |

| SWC                 | No                           | Yes                         | Yes                          | No                                | No                                 |

# 2.2.2 HyperTransport Address Map

The Tsi308 implements a single flat 64-bit address space for all accesses. All address spaces that can be reached from HyperTransport are mapped into this space. The Tsi308 checks addresses on incoming packets in each space for ranges that it accepts.

#### 2.2.2.1 Memory Mapped Space

The HyperTransport specification places Memory Mapped Space in the address range of 0000\_0000\_0000\_0000h to 0000\_00FC\_FFFF\_FFFh. The Tsi308 accepts two ranges within this space, as enabled by MemSpaceEn in the Command (Cmd) CSR, consisting of the following:

- Memory Space, defined by the MemBase and MemLimit CSRs.

- Prefetchable Memory Space, defined by the PrefMemBaseUpper/PrefMemBase and PrefMemLimitUpper/PrefMemLimit CSRs.

Setting the VgaEn bit in the Bridge Control CSR creates an additional window of 00\_000A\_0000h to 00\_000B\_FFFFh, which is also accepted. The Tsi308 never does prefetching to PCI, so the prefetchable/nonprefetchable attribute of these ranges does not matter. RdSized requests to these ranges result in MemRd requests on PCI-X bus. WrSized requests to these ranges result in MemWr requests on the PCI-X bus. If above 4GB, addresses are passed straight through as a Dual Address Cycle (DAC).

#### 2.2.2.2 I/O Space

The HyperTransport specification places PCI-X I/O space in the address range of 0000\_00FD\_FC00\_0000h to 0000\_00FD\_FDFF\_FFFFh. The Tsi308 strips the top 39 bits off of the addresses in this range.

- If enabled by I/OspaceEn in the Cmd CSR, the Tsi308 accepts requests that fall in the range defined by the I/O Base and I/O Range Base Upper, and I/O Limit and I/O Range Limit Upper CSRs.

- If set, the IsaEn bit in Bridge Control CSR creates a series of holes (the top 768 bytes of each 1 KB block in the low 64 KB) in this space that the Tsi308 does not accept.

- Setting the VgaEn bit in the Bridge Control CSR creates an additional set of windows (all addresses in the low 64 KB where the bottom 10 bits are in the ranges 3B0h 3BBh or 3C0h 3DFh), which the Tsi308 accepts. Accepted RdSized requests result in IoRd requests on PCI-X bus, and WrSized requests result in IoWr requests, with the bottom 25 bits of the HyperTransport address passed through. Bits 31:26 are 0.

#### 2.2.2.3 Configuration Space

The HyperTransport specification places PCI-X configuration space in the address range of 0000\_00FD\_FE00\_0000h to 0000\_00FD\_FFFF\_FFFh. Address bit 24 identifies requests as Type 0 or Type 1 configuration requests.

Type 0 requests are accepted and routed to the Tsi308 internal configuration registers if their device number (bits 15:11) matches the value of BaseUnitID in the HyperTransport Command CSR.

• Type 1 requests are accepted if their bus number (bits 23:16) falls within the range defined by the Secondary Bus Number and Subordinate Bus Number CSRs, inclusive. Type 1 requests are routed to PCI-X, as ConfigRd or ConfigWr cycles.

A Type 1 request with a bus number that exactly matches the Secondary Bus Number CSR becomes a PCI-X Type 0 configuration request, with AD[deviceNumber + 16] set.

• Type 1 requests with a bus number greater than Secondary Bus Number but less than or equal to Subordinate Bus number are passed on to PCI-X as Type 1 configuration cycles. Bits 23:2 of the address are left unchanged. The Tsi308 does not support the Type 1 configuration to Special cycle mapping.

#### 2.2.2.4 Interrupt Space

The HyperTransport specification places interrupt space in the address range of 0000\_00FD\_F800\_0000h to 0000\_00FD\_F8FF\_FFFFh. The Tsi308 only accepts End of Interrupt (EOI) requests in this range, which should always be broadcasts. These EOI requests are routed to the interrupt controller.

## 2.2.3 HyperTransport Address Remap

Since HyperTransport technology is meant to provide a high-bandwidth backbone for I/O systems, which are likely to contain a variety of other buses with varying addressing capabilities, the HyperTransport specification defines mechanism to remap the HyperTransport addresses to locally defined addresses of other buses allowing mapping of the smaller address spaces of individual buses into different locations within the HyperTransport technology address map.

To support this, Tsi308 implements 64-bit Address Remapping Capability as specified in [1] with single upstream DMA window. This DMA window can also be used to set specific attributes in packets that originate on PCI-X and also fall inside the address ranges defined by the DMA window. An example of this attribute is that the user can program Tsi308 to set Isoc bit for all the packets that pass through the DMA window.

Address Remapping is enabled through CSRs and is only applicable to packets traveling from/to PCI-X. It is not applicable to forward packets

# 2.2.4 HyperTransport Packet Transmission

The HyperTransport packet generator logic is essentially a large arbiter/multiplexer that formats and combines packets from each of the three virtual channels issued from within the Tsi308. The output stream is combined with the stream of packets forwarded through the Tsi308 from the far HyperTransport link. This later multiplexing is also used to insert NOP/buffer release messages to the transmitter on the link's other end.

Packet transmission is paced by the transmit buffer counters maintained in each virtual channel for both command/address and data, as the HyperTransport specification describes. These counters are decremented as packets are transmitted and incremented as buffer release messages are received from the transmitter at the link's other end. Transmit buffer counters can be throttled using the Transmit Buffer Counter Maximum CSRs (C8h and CCh).

#### 2.2.4.1 Packet Insertion

To prevent devices close to the host bridge from starving devices further out in the chain of bandwidth, the Tsi308 implements the packet insertion fairness algorithm described in [1]. This algorithm throttles the insertion rate of packets from Tsi308 relative to packets being forwarded and attempts to balance the packet insertion rates of all devices on the chain.

When Tsi308 is operating in Dual Device Mode(Split PCI-X Bus), fairness is implemented on cumulative basis wherein insert rate is computed for a single device in standard way and then actual insertion rate is doubled to account for two devices in single node/chip.

Insertion of buffer release messages is forced, even when the outgoing transmission stream is busy. Forcing allows traffic to flow through the Tsi308 continuously while maintaining a relatively small number of Rx buffers. The Tsi308 forces a buffer release message as soon as possible when an Rx buffer is freed, subject to the requirements of the HyperTransport protocol. The frequency of buffer release messages is limited under HyperTransport Transmit Control CSR (6Eh) to prevent them from occupying too much bandwidth in a busy stream. Throttling buffer releases clumps the released messages together and raises their efficiency.

In a single-hosted HyperTransport chain, the Tsi308 may be at the end of the chain furthest from the host and therefore have no downstream link connection. In this case, packets are routed to the End of Chain (EOC) logic in the unconnected link interface. The EOC logic drops responses and posted requests and generates Non-Existent Access (NXA) Error responses back into the receiver for non-posted requests. These error responses then get forwarded back to the other HyperTransport link interface's reflect path Rx buffers and back to the requesting device. Error logging for the dropped packets occurs in the Link Control Registers CSRs (44h and 48h) in Tsi301 mode or in the Link Error Register (4Dh and 51h) in standard HyperTransport mode.

# 2.3 Outbound Transactions

Outbound transactions to the Tsi308 are those accepted from the HyperTransport chain. All outbound requests go first from the HyperTransport link interface on which they are received to the Outbound Request Controller (ORC). This controller is responsible for issuing the request to the appropriate destination functional unit and for tracking the request state while it is outstanding.

The controller has two buffers, which allow state tracking for two outstanding requests. If both requests are outstanding in the controller at once, it rotates them in round-robin fashion to issue or reissue them. When the ORC filo fills, subsequent requests back up to the HyperTransport Rx buffers. Since the ORC doesn't guarantee ordering, the HyperTransport Rx buffers must not issue the second in an ordered pair of transactions until the first has completed.

The ORC is also responsible for managing space in the PCI response data buffer. All outbound non-posted requests, regardless of destination, must be allocated space in the response data buffer before they can be accepted from the Rx buffers through Data Mover (DM) by the ORC. Even though PCI response data buffer can hold two responses, ORC uses only request buffer for receiving non-posted requests from Rx command buffers, reserving the other buffer always for posted requests which in turn, provides the deadlock-avoidance guarantee required by [2] and [3] (non-posted requests are never allowed to block posted requests).

As requests complete at their destinations that fact is signaled back to the ORC (Normally PCI-X Master but PCI-X Target if request was non-posted and Tsi308 is operating in PCI-X mode), which allows the request buffer to be retired. If the request was non-posted, the transaction will require generation of a response to the host. ORC considers posted transactions as complete when the request completes at its destination and the buffer is retired. Non-posted transactions are complete when the response packet is issued to the HyperTransport transmit interface from which the request was received.

#### 2.3.1 PCI-X Outbound Transactions

Outbound requests to PCI-X are handed to the PCI-X interface to be driven out to the bus. Write data comes from the Rx data buffers, Read data is returned from the bus and placed in the PCI Response Data Buffer.

When PCI-X bus A is configured as 64 bit at reset (P0\_AD[14]), the interface automatically asserts P0\_REQ64\_N on all transactions for which it is legal. The PCI-X bus B can only be 32 bit.

The PCI-X interface supports Type 0 PCI configuration cycles to device numbers 0 through 15. Px\_AD[31:16] (x = 0 for PCI-X A, 1 for PCI-X B) are driven with a one-hot encoding during these configuration cycles, with bit 16 asserted for accesses to device number 0. This logic assumes that one Px\_AD bit is connected to the IDSEL# pin on each PCI slot through a series resister on the board.

If a request is retried or disconnected on the PCI, that fact is reported back to the ORC. The controller finishes any data movement associated with the disconnected transaction and then reissues the request from the point of disconnection. It continues to reissue a request until it completes or until the retry timer for the request expires. Because the ORC can handle two outstanding requests at a time, transactions repeatedly retried or disconnected may be reordered or interleaved.

#### 2.3.1.1 PCI-X Response Data Buffer

The PCI response data buffer contains read data returned from outbound reads to the PCI interface. This data buffer can hold a total of 64 bytes for one HyperTransport read requests.

Once the response is issued, the buffer is retired. Non-posted write requests still occupy space in the response data buffer, even though they have no read data.

#### 2.3.1.2 End of Interrupt

When an interrupt is configured as level sensitive, upstream interrupt logic must respond to an interrupt request packet with an end of interrupt (EOI) packet. Until the EOI packet is received by the Tsi308, no new interrupt request packets will be generated by that interrupt pin.

#### 2.4 Inbound Transactions

Inbound transactions are requests from the PCI-X bus or internal interrupt controller across HyperTransport to the host bridge. From there, they are routed to destinations behind the host bridge or reflected peer-to-peer back onto the HyperTransport chain. If the request is non-posted, the transaction also includes the response from the host bridge back to the original requesting unit.

The Tsi308 operates as a PCI-X target for requests from external PCI-X devices. All accepted requests are forwarded to the HyperTransport link interface leading to the host. Reads go through the delayed request buffers and are handled on the PCI-X bus as delayed requests when in standard PCI mode or as split requests when in PCI-X mode. All writes, except IO writes are posted into the posted request queue and allowed to immediately complete on the PCI-X bus.

# 2.4.1 PCI-X Address Map

Accesses on PCI-X bus are checked against the following ranges to determine whether the Tsi308 is the target of the access and should assert Px\_DEVSEL\_N to accept the request. The Tsi308 makes this determination with medium DEVSEL# timing. When PCI-X A bus is configured as 64-bit target at power up, the Tsi308 asserts P0\_ACK64\_N in response to P0\_REQ64\_N for requests it accepts.

• **Memory Mapped Cycles**. The Tsi308 implements a 64-bit space for memory mapped accesses and decodes DAC accesses for addresses above 4 GB. While operating in Tsi301 compatible mode address bits above 39 are ignored and result in the 40-bit space aliasing through PCI's 64-bit memory mapped space.

Memory mapped addresses are compared to the range defined by the Memory Range Base Addr and Memory Range Limit Addr CSRs; and the range defined by the Prefetchable Memory Range Base Upper and Prefetchable Memory Range Base Addr, and Prefetchable Memory Range Limit Upper and Prefetchable Memory Range Limit Addr CSRs. Addresses that don't fall into any of these ranges are accepted for forwarding to HyperTransport as long as the MasterEn bit in Command CSR is set and bits [39:32] <= FCh.

• I/O Cycles. The Tsi308 implements a 64-bit space for I/O accesses. While operating in Tsi301 compatible mode, address bits above bit 24 are ignored and result in 25-bit space aliasing through PCI's 32-bit I/O space.

I/O addresses are compared to the range defined by I/O Range Base Upper and I/O Base, and I/O Range Limit Upper and I/O Limit CSRs. Accesses that miss the range are accepted for forwarding to HyperTransport, as long as MasterEn bit in the Command CSR is set.

• Configuration and Special Cycles. The Tsi308 never acts as a target for configuration or special cycles on PCI-X bus.

#### 2.4.2 PCI-X Posted Write Queue

The Tsi308 responds as a PCI-X write target to PCI-X Memory Write, Memory Write Invalidate, and I/O Write commands. All of these writes are posted to the HyperTransport chain except I/O writes which is non-posted. The Tsi308 never responds to Configuration Writes. A total of 1024 bytes of buffering for posted data is provided per PCI-X bus.

Memory Write and Memory Write Invalidate commands stream data into the chip, disconnecting either on 4-KB boundaries or when all of the internal buffer space is filled. The Tsi308 generates the largest HyperTransport write operations possible, issuing them continuously as the data for each write is received from PCI-X.

As the bandwidth of HyperTransport exceeds the bandwidth of PCI-X, it is expected that the internal buffers will not fill and memory writes will proceed continuously at the full bandwidth of PCI-X bus.

## 2.4.3 PCI-X Delayed/Split Request Buffers

The Tsi308 acts as a PCI-X target for PCI-X Memory Read, Memory Read Line (PCI), Memory Read Multiple (PCI), Memory Read Block (PCI-X), I/O Write and I/O Read commands. The Tsi308 never responds to configuration read or interrupt acknowledge accesses. All supported read transactions are implemented as delayed requests (PCI) or split requests (PCI-X).

Incoming requests are assigned to a delayed request buffer. There are four delayed request buffers, enabled under CSR control, allowing up to four PCI-X read requests to be in progress at one time. If no delayed request buffers are free, incoming requests are retried until one is available. Once the request is assigned to a buffer, the interface continues to retry it on the PCI bus while read requests are issued to the HyperTransport interface.

I/O writes are not allowed to stream and always disconnect after a single data beat on the PCI-X (32-bits). Each I/O write is issued to HyperTransport as an independent request.

## 2.4.4 Prefetching (PCI mode only)

While operating in standard PCI mode, the Tsi308 supports a variety of prefetching options configured under CSR control using two Read Control CSRs, Read Control 1 at 62h:60h and Read Control 2 at 5Eh:5Ch. Read Control 2 is applied for requests passing through DMA window and is reserved in Tsi301 compatible mode. However:

- I/O reads are never prefetchable.

- MemRdLines and MemRdMult may have prefetching individually configured.

- For systems in which MemRds are known to be side-effect free, MemReadPrefEn can be set to enable prefetching behavior for MemReads using the same parameters as MemRdLines.

- PrefEn can be used to globally enable or disable all prefetching.

- Nonprefetchable reads always request only the bytes required to satisfy the initial data beat

of four or eight bytes on the PCI bus, which may result in either one or two HyperTransport

requests.

Transactions for which prefetching is enabled issue a HyperTransport read for the remainder of the 64-byte aligned block containing the original request. These transactions also issue HyperTransport reads for the zero to seven complete 64-byte blocks following, as determined by the Read Control CSRs. The total number of reads that may be outstanding to HyperTransport at one time is limited by the Outbound Data Buffers.

When multiple reads to HyperTransport are issued for a single PCI read request due to prefetching or due to clear byte enables in a 64-bit nonprefetchable read on a 64-bit bus, each HyperTransport request is referred to as a subrequest of the PCI request. Each Delayed Request Buffer can track up to 8 subrequests at once. The total number of configured subrequests (number of enabled delayed request buffers \* (the maximum number of subrequests each, rounded up to the next power of 2)) must not exceed the number of entries in the Outbound Data Buffers.

## 2.4.5 Memory Read Block (PCI-X mode only)

MemRdBlk command of PCI-X is analogous to MemRdLine or MemRdMultiple of PCI.

Since PCI-X request provides the byte count to be satisfied during the attribute phase of a PCI-X read transaction, read data for PCI-X requests are never prefetched, instead data is read just enough to satisfy the byte count of the original request.

Similar to in PCI mode, Tsi308 can handle up to four PCI-X read requests and they are assigned to Delayed Request Buffers as usual, however a single PCI-X read request can request up to 4K bytes. The Tsi308 implements a maximum of 512 byte buffering per request. For reads requesting greater than 512 bytes, Tsi308 throttles the requests issued on HyperTransport by issuing a subrequest on HyperTransport if at least 64 bytes of buffer space is available in Outbound Data Buffer allotted for that particular request until the byte count is satisfied. As the data arrives from HyperTransport into Outbound Data Buffer, PCI-X Master behaving as Split Completer connects on PCI-X bus and transfers the data to the original requester in chunks of 128 bytes disconnecting at naturally aligned 128-byte boundary or Allowable Disconnect Boundary (ADB).

## 2.4.6 SrcTags

The SrcTag for each HyperTransport read request is formed by concatenating the delayed request buffer number with the number of the HyperTransport subrequest being issued by that buffer.

#### 2.4.7 Sequences

HyperTransport subrequests that are part of the same PCI-X request must be tagged with a matching nonzero SeqID to guarantee ordering at the target. This 4-bit SeqID is formed by concatenating a leading 1 (guaranteeing a nonzero result) with the 2-bit delayed request buffer number and one bit that toggles for each occupation of the delayed request buffer. The concatenation prevents consecutive PCI-X reads from being issued with the same SeqID and appearing to have HyperTransport ordering requirements.

## 2.4.8 Read Responses

As the read responses return from HyperTransport, the data is stored in the Outbound Data Buffers. Even though sequenced requests are guaranteed to reach the target in order, responses may be received from the target out of order. When all the data from the first HyperTransport requests is received (the amount required is controlled by the InitCount fields of the Read Control CSRs), the PCI interface ceases retrying the request. Read data is supplied from the buffers when the request is next reissued. Data streams to the PCI bus until the transaction is disconnected by the PCI master or until the next data required is not present in the Outbound Data Buffers.

The difference in operation while operating in PCI-X mode is that:

- Original read request is split first time while latching request and requestor information.

- Tsi308 connects itself with original requester on PCI-X as Split Completer as opposed to waiting for the request to be reissued.

- Data is transferred in ADBs as PCI-X master is not allowed to disconnect arbitrarily.

• Tsi308 generates one or more split completion transactions until the byte count of the original request is satisfied.

## 2.4.9 Continuous Prefetching (PCI mode only)

If continuous prefetching is enabled in the Read Control CSR, the Tsi308 issues further ascending read requests to fill buffers as they drain (up to a 4-KB page boundary) in an effort to make sure required data is always available. Otherwise, the transaction is disconnected as soon as all data from the initial reads is returned to the PCI bus.

#### 2.4.10 Transaction Disconnects

Read transactions may be disconnected by the bridge when required data is not available in time. The Delayed Request buffer remains in use until all outstanding HyperTransport prefetch requests receive their responses; then it is retired and any leftover data is discarded (PCI mode only). Each delayed request buffer also has an associated discard timer loaded with one of the two values determined by the Secondary Discard Timer bit (9) of the Bridge Control CSR (3Eh) when the data is received from HyperTransport. If this timer expires before the data is called for by the PCI master, the data is discarded and the buffer is retired.

#### 2.4.11 Outbound Data Buffer

The Tsi308 contains a central data buffer (four 512-byte entries) for the accumulation of read response data to return to the PCI-X bus. These four buffers correspond to four read requests in Delayed Request Buffers. Data returning from HyperTransport is loaded into the buffer based on the comparison between request information stored in the corresponding delayed request number and information contained in response header, and drained out to the PCI-X bus when the delayed request reconnects (PCI) or when the Tsi308's split completer connects.

## 2.4.12 Interrupt Generation

The Tsi308 interrupt controller supports 10 interrupts per PCI-X port. Each of these interrupts are enabled and configured independently through its Interrupt Definition Register CSR. However Tsi308 while operating in Tsi301 compatible mode, these interrupts are partitioned into different groups, each group consists of four interrupts or less and interrupts are configured in groups. The interrupt configuration options include: edge versus level sensitivity, polarity, and vector ID.

An incoming interrupt is first synchronized to the core clock domain and masked with its CSR enable bit to set the interrupt's bid in the Interrupt Request Register (IRR). A round-robin arbiter will then examine each IRR bit and forward requests to the primary bus logic, setting its In Service Register (ISR) bit. New interrupts from that pin will not be accepted as long as the ISR register is set.

• For edge sensitive interrupts, the ISR bit is cleared as soon as the primary interface logic accepts the inbound interrupt request

- For level interrupts, the ISR bit is not cleared until an End of Interrupt (EOI) packet is received with a vector ID matching the ISR. Software may also write a 1 to 63<sup>rd</sup> bit of Interrupt Definition Register to clear the interrupt without an EOI.

- All interrupts and interrupt blocks are disabled at reset and must be enabled by software

- The ISR can also be monitored via the CSRs

#### 2.4.12.1 Interrupt Diagnostic Mode

To simplify debugging interrupt software and hardware, each interrupt may be stimulated and monitored via CSR reads and writes (see the Interrupt Diagnostic Register for details). Writing a 1 to the Initiate field of the CSR will generate an interrupt on the interrupt line in the Pin Number field. The ISR bit may be observed by monitoring the Active field of the same CSR.

The Active field is always for the CSR indicated by the Pin Number field

#### 2.5 PCI-X Arbiter

The Tsi308 includes a PCI-X arbiter for each PCI-X port. The arbiter is an independent unit. The Tsi308's internal PCI-X request and PCI-X grant signals are connected to pins as  $Px_REQ_OUT_N$  and  $Px_GNT_IN_N$  (x = 0 for PCI A and x = 1 for PCI B). It is possible to either use this arbiter or to bypass it and use an external arbiter.

The Tsi308's internal arbiter contains two round-robin arbitration groups: Px\_REQ0\_N and Px\_REQ1\_N through Px\_REQ5\_N. Within each group, arbitration is shared equally between the requests. Generally Px\_REQ\_OUT\_N would be attached to Px\_REQ0\_N and Px\_GNT\_IN\_N attached to Px\_GNT0\_N.

When there are no requests present, the arbiter either parks the bus at the last grant or (based on a CSR bit) at Px GNT0 N, which is presumed to be the Tsi308's internal requester.

The PCI Control CSR ParkMaster bit allows the configuration of the internal PCI-X Arbiter parking.

## 2.6 Online Insertion and Removal (OIR)

The Tsi308 device provides a hook to help users implement their own proprietary hot plugging outside of the device. The device implements an input pin (Px\_OIR\_DISCON\_EVENT) in each of the two PCI-X interface logic which is asserted by the user when an attached PCI-X card is about to be removed. When asserted, Tsi308's PCI-X master finishes its current transfer if any progress at the time on PCI-X and stops generating any further traffic. Tsi308 starts sending dummy responses to HyperTransport for all the pending read requests (that are within the chip queue yet to be executed on PCI-X as well as the ones that have been already presented on PCI-X and are pending on PCI-X), and silently drops all the posted requests from HyperTransport meant for the affected PCI-X port.

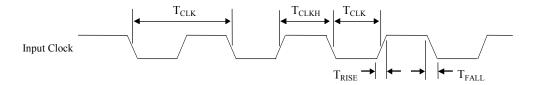

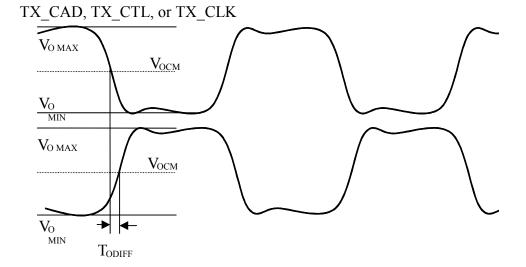

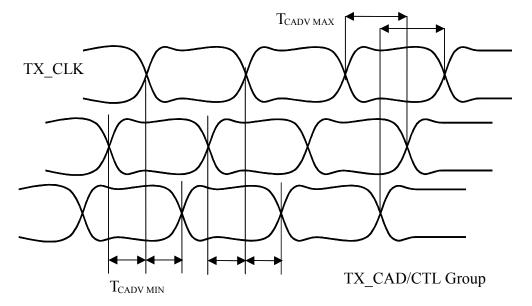

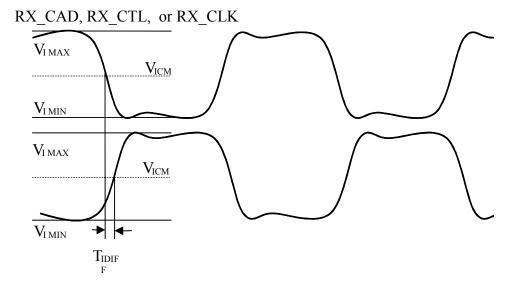

This condition persists until software resets the PCI-X by writing a 1 to SecBusReset (bit 6) of Bridge Control Register.