# PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES SEPTEMBER 7, 2016

DATASHEET

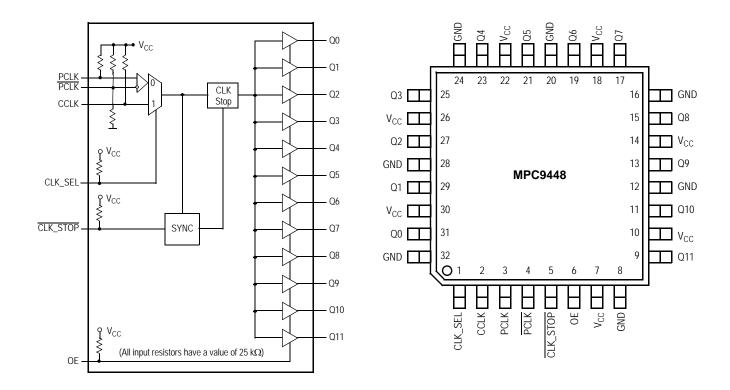

The Freescale Semiconductor, Inc. MPC9448 is a 3.3 V or 2.5 V compatible, 1:12 clock fanout buffer targeted for high performance clock tree applications. With output frequencies up to 350 MHz and output skews less than 150 ps, the device meets the needs of most demanding clock applications.

#### **Features**

- 12 LVCMOS compatible clock outputs

- Selectable LVCMOS and differential LVPECL compatible clock inputs

- Maximum clock frequency of 350 MHz

- Maximum clock skew of 150 ps

- Synchronous output stop in logic low state eliminates output runt pulses

- · High-impedance output control

- 3.3 V or 2.5 V power supply

- · Drives up to 24 series terminated clock lines

- Ambient temperature range -40°C to +85°C

- 32-Lead LQFP packaging, Pb-free

- Supports clock distribution in networking, telecommunication and computing applications

- Pin and function compatible to MPC948

- For drop in replacement part use 83948AYI-147

## **Functional Description**

The MPC9448 is specifically designed to distribute LVCMOS compatible clock signals up to a frequency of 350 MHz. Each output provides a precise copy of the input signal with a near zero skew. The outputs buffers support driving of 50  $\Omega$  terminated transmission lines on the incident edge.

Each output is capable of driving either one parallel terminated or two series terminated transmission lines.

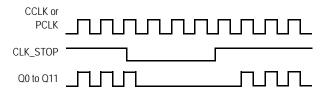

Two selectable, independent clock inputs are available, providing support of LVCMOS and differential LVPECL clock distribution systems. The MPC9448 CLK\_STOP control is synchronous to the falling edge of the input clock. It allows the start and stop of the output clock signal only in a logic low state, thus eliminating potential output runt pulses. Applying the OE control will force the outputs into high-impedance mode.

All inputs have an internal pull-up or pull-down resistor preventing unused and open inputs from floating. The device supports a 2.5 V or 3.3 V power supply and an ambient temperature range of -40°C to +85°C. The MPC9448 is pin and function compatible but performance-enhanced to the MPC948.

LOW VOLTAGE 3.3 V/2.5 V LVCMOS 1:12 CLOCK FANOUT BUFFER

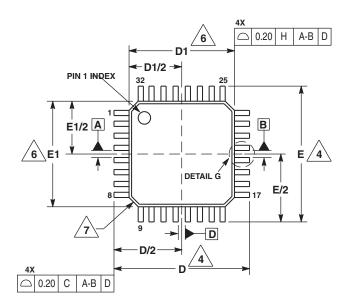

AC SUFFIX 32-LEAD LQFP PACKAGE Pb-FREE PACKAGE CASE 873A-03

Figure 1. Logic Diagram

Figure 2. 32-Lead Pinout (Top View)

Table 1. Function Table

| Control  | Default | 0                                                      | 1                   |

|----------|---------|--------------------------------------------------------|---------------------|

| CLK_SEL  | 1       | PECL differential input selected                       | CCLK input selected |

| OE       | 1       | Outputs disabled (high-impedance state) <sup>(1)</sup> | Outputs enabled     |

| CLK_STOP | 1       | Outputs synchronously stopped in logic low state       | Outputs active      |

<sup>1.</sup> OE = 0 will high-impedance tristate all outputs independent on  $\overline{\text{CLK\_STOP}}$ .

# **Table 2. Pin Configurations**

| Pin             | I/O    | Туре            | Function                                                                                                                              |

|-----------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| PCLK, PCLK      | Input  | LVPECL          | Clock signal input                                                                                                                    |

| CCLK            | Input  | LVCMOS          | Alternative clock signal input                                                                                                        |

| CLK_SEL         | Input  | LVCMOS          | Clock input select                                                                                                                    |

| CLK_STOP        | Input  | LVCMOS          | Clock output enable/disable                                                                                                           |

| OE              | Input  | LVCMOS          | Output enable/disable (high-impedance tristate)                                                                                       |

| Q0-11           | Output | LVCMOS          | Clock outputs                                                                                                                         |

| GND             | Supply | Ground          | Negative power supply (GND)                                                                                                           |

| V <sub>CC</sub> | Supply | V <sub>CC</sub> | Positive power supply for I/O and core. All V <sub>CC</sub> pins must be connected to the positive power supply for correct operation |

Table 3. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Characteristics     | Min  | Max                   | Unit |

|-------------------|---------------------|------|-----------------------|------|

| V <sub>CC</sub>   | Supply Voltage      | -0.3 | 3.9                   | V    |

| V <sub>IN</sub>   | DC Input Voltage    | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OUT</sub>  | DC Output Voltage   | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| I <sub>IN</sub>   | DC Input Current    |      | ±20                   | mA   |

| I <sub>OUT</sub>  | DC Output Current   |      | ±50                   | mA   |

| T <sub>Stor</sub> | Storage temperature | -65  | 125                   | °C   |

Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these

conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated

conditions is not implied.

# **Table 4. General Specifications**

| Symbol          | Characteristics                   | Min  | Тур                 | Max | Unit | Condition  |

|-----------------|-----------------------------------|------|---------------------|-----|------|------------|

| V <sub>TT</sub> | Output Termination Voltage        |      | V <sub>CC</sub> ÷ 2 |     | V    |            |

| MM              | ESD Protection (Machine model)    | 200  |                     |     | V    |            |

| НВМ             | ESD Protection (Human body model) | 2000 |                     |     | V    |            |

| LU              | Latch-up Immunity                 | 200  |                     |     | mA   |            |

| C <sub>PD</sub> | Power Dissipation Capacitance     |      | 10                  |     | pF   | Per output |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0                 |     | pF   | Inputs     |

Table 5. DC Characteristics ( $V_{CC} = 3.3 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to +85°C)

| Symbol                          | Characteristics                  |      | Min  | Тур | Max                   | Unit   | Condition                                                         |

|---------------------------------|----------------------------------|------|------|-----|-----------------------|--------|-------------------------------------------------------------------|

| V <sub>IH</sub>                 | Input HIGH Voltage               |      | 2.0  |     | V <sub>CC</sub> + 0.3 | V      | LVCMOS                                                            |

| V <sub>IL</sub>                 | Input LOW Voltage                |      | -0.3 |     | 0.8                   | V      | LVCMOS                                                            |

| V <sub>PP</sub>                 | Peak-to-Peak Input Voltage       | PCLK | 250  |     |                       | mV     | LVPECL                                                            |

| V <sub>CMR</sub> <sup>(1)</sup> | Common Mode Range                | PCLK | 1.1  |     | V <sub>CC</sub> - 0.6 | V      | LVPECL                                                            |

| I <sub>IN</sub>                 | Input Current <sup>(2)</sup>     |      |      |     | 300                   | μА     | V <sub>IN</sub> = V <sub>CC</sub> or GND                          |

| V <sub>OH</sub>                 | Output HIGH Voltage              |      | 2.4  |     |                       | V      | $I_{OH} = -24 \text{ mA}^{(3)}$                                   |

| V <sub>OL</sub>                 | Output LOW Voltage               |      |      |     | 0.55<br>0.30          | V<br>V | I <sub>OL</sub> = 24 mA <sup>(3)</sup><br>I <sub>OL</sub> = 12 mA |

| Z <sub>OUT</sub>                | Output Impedance                 |      |      | 17  |                       | Ω      |                                                                   |

| I <sub>CCQ</sub> <sup>(4)</sup> | Maximum Quiescent Supply Current |      |      |     | 2.0                   | mA     | All V <sub>CC</sub> Pins                                          |

V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (DC) specification.

<sup>2.</sup> Input pull-up / pull-down resistors influence input current.

<sup>3.</sup> The MPC9448 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50  $\Omega$  series terminated transmission lines (for V<sub>CC</sub> = 3.3 V) or one 50  $\Omega$  series terminated transmission line (for V<sub>CC</sub> = 2.5 V).

<sup>4.</sup> I<sub>CCQ</sub> is the DC current consumption of the device with all outputs open and the input in its default state or open.

Table 6. AC Characteristics ( $V_{CC} = 3.3 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ )<sup>(1)</sup>

| Symbol                                     | Characteristics                                        | Min        | Тур | Max                   | Unit     | Condition               |

|--------------------------------------------|--------------------------------------------------------|------------|-----|-----------------------|----------|-------------------------|

| f <sub>ref</sub>                           | Input Frequency                                        | 0          |     | 350                   | MHz      |                         |

| f <sub>MAX</sub>                           | Maximum Output Frequency                               | 0          |     | 350                   | MHz      |                         |

| V <sub>PP</sub>                            | Peak-to-Peak Input Voltage PCLK                        | 400        |     | 1000                  | mV       | LVPECL                  |

| V <sub>CMR</sub> <sup>(2)</sup>            | Common Mode Range PCLK                                 | 1.3        |     | V <sub>CC</sub> - 0.8 | V        | LVPECL                  |

| t <sub>P, REF</sub>                        | Reference Input Pulse Width                            | 1.4        |     |                       | ns       |                         |

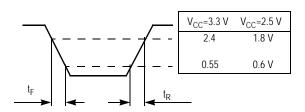

| t <sub>r</sub> , t <sub>f</sub>            | CCLK Input Rise/Fall Time                              |            |     | 1.0 <sup>(3)</sup>    | ns       | 0.8 to 2.0 V            |

| t <sub>PLH/HL</sub><br>t <sub>PLH/HL</sub> | Propagation Delay PCLK to any Q CCLK to any Q          | 1.6<br>1.3 |     | 3.6<br>3.3            | ns<br>ns |                         |

| t <sub>PLZ, HZ</sub>                       | Output Disable Time                                    |            |     | 11                    | ns       |                         |

| t <sub>PZL, LZ</sub>                       | Output Enable Time                                     |            |     | 11                    | ns       |                         |

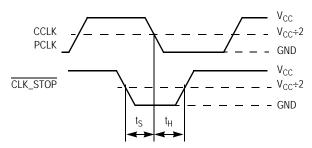

| t <sub>S</sub>                             | Setup Time CCLK to CLK_STOP PCLK to CLK_STOP           | 0.0<br>0.0 |     |                       | ns<br>ns |                         |

| t <sub>H</sub>                             | Hold Time CCLK to CLK_STOP PCLK to CLK_STOP            | 1.0<br>1.5 |     |                       | ns<br>ns |                         |

| t <sub>sk(O)</sub>                         | Output-to-Output Skew                                  |            |     | 150                   | ps       |                         |

| t <sub>sk(PP)</sub>                        | Device-to-Device Skew PCLK or CCLK to any Q            |            |     | 2.0                   | ns       |                         |

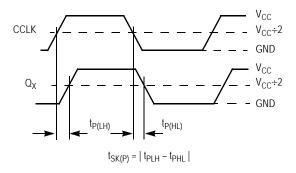

| t <sub>SK(P)</sub>                         | Output Pulse skew <sup>(4)</sup> Using CCLK Using PCLK |            |     | 300<br>400            | ps<br>ps |                         |

| $DC_Q$                                     | Output Duty Cycle f <sub>Q</sub> <170 MHz              | 45         | 50  | 55                    | %        | DC <sub>REF</sub> = 50% |

| t <sub>r</sub> , t <sub>f</sub>            | Output Rise/Fall Time                                  | 0.1        |     | 1.0                   | ns       | 0.55 to 2.4 V           |

- 1. AC characteristics apply for parallel output termination of 50  $\Omega$  to  $V_{TT}.$

- V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> or V<sub>PP</sub> impacts t<sub>PLH/HL</sub> and t<sub>SK(PP)</sub>.

- 3. Violation of the 1.0 ns maximum input rise and fall time limit will affect the device propagation delay, device-to-device skew, reference input pulse width, output duty cycle and maximum frequency specifications.

- 4. Output pulse skew is the absolute difference of the propagation delay times:  $|t_{pLH} t_{pHL}|$ .

Table 7. DC Characteristics ( $V_{CC}$  = 2.5 V ± 5%,  $T_A$  = -40°C to +85°C)

| Symbol                          | Characteristics                  |      | Min  | Тур | Max                   | Unit | Condition                                  |

|---------------------------------|----------------------------------|------|------|-----|-----------------------|------|--------------------------------------------|

| V <sub>IH</sub>                 | Input high voltage               |      | 1.7  |     | V <sub>CC</sub> + 0.3 | V    | LVCMOS                                     |

| V <sub>IL</sub>                 | Input low voltage                |      | -0.3 |     | 0.7                   | V    | LVCMOS                                     |

| V <sub>PP</sub>                 | Peak-to-peak input voltage       | PCLK | 250  |     |                       | mV   | LVPECL                                     |

| V <sub>CMR</sub> <sup>(1)</sup> | Common Mode Range                | PCLK | 1.0  |     | V <sub>CC</sub> - 0.7 | V    | LVPECL                                     |

| I <sub>IN</sub>                 | Input current <sup>(2)</sup>     |      |      |     | 300                   |      | $V_{IN} = GND \text{ or } V_{IN} = V_{CC}$ |

| V <sub>OH</sub>                 | Output High Voltage              |      | 1.8  |     |                       | V    | $I_{OH} = -15 \text{ mA}^{(3)}$            |

| V <sub>OL</sub>                 | Output Low Voltage               |      |      |     | 0.6                   | V    | I <sub>OL</sub> = 15 mA <sup>(3)</sup>     |

| Z <sub>OUT</sub>                | Output impedance                 |      |      | 19  |                       | Ω    |                                            |

| I <sub>CCQ</sub> <sup>(4)</sup> | Maximum Quiescent Supply Current |      |      |     | 2.0                   | mA   | All V <sub>CC</sub> Pins                   |

- V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (DC) specification.

- 2. Input pull-up / pull-down resistors influence input current.

- 3. The MPC9448 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives one 50  $\Omega$  series terminated transmission lines at V<sub>CC</sub> = 2.5 V.

- 4. I<sub>CCQ</sub> is the DC current consumption of the device with all outputs open and the input in its default state or open.

Table 8. AC Characteristics ( $V_{CC}$  = 2.5 V ± 5%,  $T_A$  = -40°C to +85°C)<sup>(1)</sup>

| Symbol                                     | Characteristics                                                                | Min        | Тур      | Max                   | Unit     | Condition               |

|--------------------------------------------|--------------------------------------------------------------------------------|------------|----------|-----------------------|----------|-------------------------|

| f <sub>ref</sub>                           | Input Frequency                                                                | 0          |          | 350                   | MHz      |                         |

| f <sub>MAX</sub>                           | Maximum Output Frequency                                                       | 0          |          | 350                   | MHz      |                         |

| V <sub>PP</sub>                            | Peak-to-peak input voltage PCLK                                                | 400        |          | 1000                  | mV       | LVPECL                  |

| V <sub>CMR</sub> <sup>(2)</sup>            | Common Mode Range PCLK                                                         | 1.2        |          | V <sub>CC</sub> - 0.8 | V        | LVPECL                  |

| t <sub>P, REF</sub>                        | Reference Input Pulse Width                                                    | 1.4        |          |                       | ns       |                         |

| t <sub>r</sub> , t <sub>f</sub>            | CCLK Input Rise/Fall Time                                                      |            |          | 1.0 <sup>(3)</sup>    | ns       | 0.8 to 2.0 V            |

| t <sub>PLH/HL</sub><br>t <sub>PLH/HL</sub> | Propagation delay PCLK to any Q CCLK to any Q                                  | 1.5<br>1.7 |          | 4.2<br>4.4            | ns<br>ns |                         |

| t <sub>PLZ, HZ</sub>                       | Output Disable Time                                                            |            |          | 11                    | ns       |                         |

| t <sub>PZL, LZ</sub>                       | Output Enable Time                                                             |            |          | 11                    | ns       |                         |

| t <sub>S</sub>                             | Setup time CCLK to CLK_STOP PCLK to CLK_STOP                                   | 0.0<br>0.0 |          |                       | ns<br>ns |                         |

| t <sub>H</sub>                             | Hold time CCLK to CLK_STOP PCLK to CLK_STOP                                    | 1.0<br>1.5 |          |                       | ns<br>ns |                         |

| t <sub>sk(O)</sub>                         | Output-to-output Skew                                                          |            |          | 150                   | ps       |                         |

| t <sub>sk(PP)</sub>                        | Device-to-device Skew PCLK or CCLK to any Q                                    |            |          | 2.7                   | ns       |                         |

| t <sub>SK(p)</sub>                         | Output pulse skew <sup>(4)</sup> Using CCLK Using PCLK                         |            |          | 200<br>300            | ps<br>ps | DC 500/                 |

| DC <sub>Q</sub>                            | Output Duty Cycle $f_Q$ < 350 MHz and using CCLK $f_Q$ <200 MHz and using PCLK | 45<br>45   | 50<br>50 | 55<br>55              | %<br>%   | DC <sub>REF</sub> = 50% |

| t <sub>r</sub> , t <sub>f</sub>            | Output Rise/Fall Time                                                          | 0.1        |          | 1.0                   | ns       | 0.6 to 1.8 V            |

<sup>1.</sup> AC characteristics apply for parallel output termination of 50  $\Omega$  to V  $_{TT}.$

<sup>2.</sup>  $V_{CMR}$  (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the  $V_{CMR}$  range and the input swing lies within the  $V_{PP}$  (AC) specification. Violation of  $V_{CMR}$  or  $V_{PP}$  impacts  $t_{PLH/HL}$  and  $t_{SK(PP)}$ .

<sup>3.</sup> Violation of the 1.0 ns maximum input rise and fall time limit will affect the device propagation delay, device-to-device skew, reference input pulse width, output duty cycle and maximum frequency specifications.

<sup>4.</sup> Output pulse skew is the absolute difference of the propagation delay times: |  $t_{pLH}$  -  $t_{pHL}$  |.

#### APPLICATION INFORMATION

Figure 3. Output Clock Stop (CLK\_STOP)

Timing Diagram

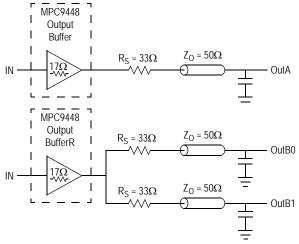

## **Driving Transmission Lines**

The MPC9448 clock driver was designed to drive high-speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user, the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of 17  $\Omega$  (V $_{\rm CC}$  = 3.3 V), the outputs can drive either parallel or series terminated transmission lines. For more information on transmission lines, the reader is referred to Freescale application note AN1091. In most high performance clock networks, point-to-point distribution of signals is the method of choice. In a point-to-point scheme, either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a 50  $\Omega$  resistance to  $V_{\rm CC}\div2$ .

Figure 4. Single versus Dual Transmission Lines

This technique draws a fairly high level of DC current ,and thus, only a single terminated line can be driven by each output of the MPC9448 clock driver. For the series terminated case, however, there is no DC current draw; thus, the outputs can drive multiple series terminated lines. Figure 4 illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme, the fanout of the MPC9448 clock driver is effectively doubled due to its capability to drive multiple lines at  $V_{\rm CC}=3.3~\rm V.$

Figure 5. Single versus Dual Line Termination Waveforms

The waveform plots in Figure 5 show the simulation results of an output driving a single line versus two lines. In both cases, the drive capability of the MPC9448 output buffer is more than sufficient to drive 50  $\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations, a delta of only 43 ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the MPC9448. The output waveform in Figure 5 shows a step in the waveform. This step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the 33  $\Omega$  series resistor plus the output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$$\begin{aligned} &V_L = V_S \left( Z_0 \div (R_S + R_0 + Z_0) \right) \\ &Z_0 = 50 \ \Omega \ || \ 50 \ \Omega \\ &R_S = 33 \ \Omega \ || \ 33 \ \Omega \\ &R_0 = 17 \ \Omega \\ &V_L = 3.0 \ (25 \div (16.5 + 17 + 25)) \\ &= 1.28 \ V \end{aligned}$$

At the load end, the voltage will double, due to the near unity reflection coefficient, to 2.5 V. It will then increment towards the quiescent 3.0 V in steps separated by one round trip delay (in this case 4.0 ns).

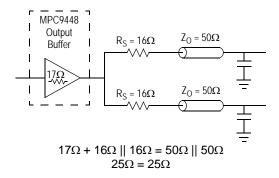

Since this step is well above the threshold region, it will not cause any false clock triggering; however, designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines, the situation in Figure 6 should be used. In this case, the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance, the line impedance is perfectly matched.

Figure 6. Optimized Dual Line Termination

# Power Consumption of the MPC9448 and Thermal Management

The MPC9448 AC specification is guaranteed for the entire operating frequency range up to 350 MHz. The MPC9448 power consumption, and the associated long-term reliability, may decrease the maximum frequency limit, depending on operating conditions such as clock frequency, supply voltage, output loading, ambient temperature, vertical convection and thermal conductivity of package and board. This section describes the impact of these parameters on the junction temperature and gives a guideline to estimate the MPC9448 die junction temperature and the associated device reliability. For a complete analysis of power consumption as a function of operating conditions and associated long term device reliability, please refer to the Freescale application note AN1545. According the AN1545, the long-term device reliability is a function of the die junction temperature:

**Table 9. Die Junction Temperature and MTFB**

| Junction Temperature (°C) | MTBF (Years) |

|---------------------------|--------------|

| 100                       | 20.4         |

| 110                       | 9.1          |

| 120                       | 4.2          |

| 130                       | 2.0          |

Increased power consumption will increase the die junction temperature and impact the device reliability (MTBF). According to the system-defined tolerable MTBF, the die junction temperature of the MPC9448 needs to be controlled, and the thermal impedance of the board/package should be optimized. The power dissipated in the MPC9448 is represented in equation 1.

Where  $I_{CCQ}$  is the static current consumption of the MPC9448,  $C_{PD}$  is the power dissipation capacitance per output.  $(M)\Sigma C_L$  represents the external capacitive output load, and N is the number of active outputs (N is always 12 in case of the MPC9448). The MPC9448 supports driving transmission lines to maintain high signal integrity and tight timing parameters. Any transmission line will hide the lumped capacitive load at the end of the board trace, therefore,  $\Sigma C_L$  is zero for controlled transmission line systems and can be eliminated from equation 1. Using parallel termination output, termination results in equation 2 for power dissipation.

In equation 2, P stands for the number of outputs with a parallel or thevenin termination.  $V_{OL},\,I_{OL},\,V_{OH}$  and  $I_{OH}$  are a function of the output termination technique, and  $DC_Q$  is the clock signal duty cycle. If transmission lines are used,  $\Sigma C_L$  is zero in equation 2 and can be eliminated. In general, the use of controlled transmission line techniques eliminates the impact of the lumped capacitive loads at the end lines and greatly reduces the power dissipation of the device. Equation 3 describes the die junction temperature  $T_J$  as a function of the power consumption.

Where  $R_{thja}$  is the thermal impedance of the package (junction to ambient), and  $T_A$  is the ambient temperature. According to Figure 9, the junction temperature can be used to estimate the long-term device reliability. Further, combining equation 1 and equation 2 results in a maximum operating frequency for the MPC9448 in a series terminated transmission line system, equation 4.

$$P_{TOT} = \left[ \ I_{CCQ} + V_{CC} \cdot f_{CLOCK} \cdot \left( \ N \cdot C_{PD} + \sum_{M} C_{L} \right) \ \right] \cdot V_{CC}$$

Equation 1

$$P_{TOT} = V_{CC} \cdot \left[ \ I_{CCQ} + V_{CC} \cdot f_{CLOCK} \cdot \left( \ N \cdot C_{PD} + \sum_{M} C_{L} \right) \ \right] + \sum_{P} \left[ \ DC_{Q} \cdot I_{OH} \cdot \left( V_{CC} - V_{OH} \right) + \left( 1 - DC_{Q} \right) \cdot I_{OL} \cdot V_{OL} \ \right]$$

Equation 2

$$T_{J} = T_{A} + P_{TOT} \cdot R_{thja}$$

Equation 3

$$f_{CLOCK,MAX} = \frac{1}{C_{PD} \cdot N \cdot V_{CC}^{2}} \cdot \left[ \frac{T_{j,MAX} - T_{A}}{R_{thja}} - \left( I_{CCQ} \cdot V_{CC} \right) \right]$$

Equation 4

$T_{J,MAX}$  should be selected according to the MTBF system requirements, and Figure 9  $R_{thja}$  can be derived from Figure 10. The  $R_{thja}$  represent data based on 1S2P boards. Using 2S2P boards will result in a lower thermal impedance than indicated below.

Table 10. Thermal Package Impedance of the 32ld LQFP

| Convection, LFPM | R <sub>thja</sub> (1P2S board),<br>°C/W | R <sub>thja</sub> (2P2S board),<br>°C/W |  |  |  |  |  |

|------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Still air        | 86                                      | 61                                      |  |  |  |  |  |

| 100 lfpm         | 76                                      | 56                                      |  |  |  |  |  |

| 200 lfpm         | 71                                      | 54                                      |  |  |  |  |  |

| 300 lfpm         | 68                                      | 53                                      |  |  |  |  |  |

| 400 lfpm         | 66                                      | 52                                      |  |  |  |  |  |

| 500 lfpm         | 60                                      | 49                                      |  |  |  |  |  |

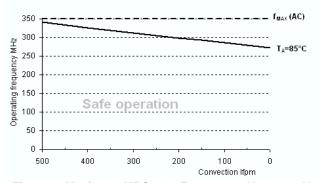

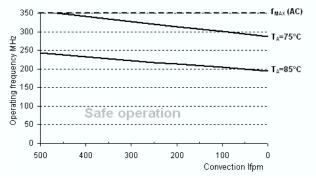

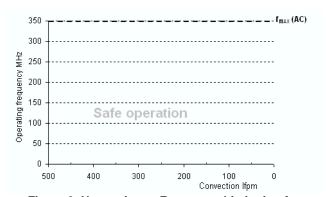

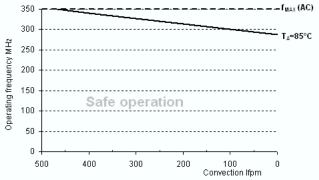

If the calculated maximum frequency is below 350 MHz, it becomes the upper clock speed limit for the given application conditions. The following eight derating charts describe the safe frequency operation range for the MPC9448. The charts were calculated for a maximum tolerable die junction temperature of 110°C (120°C), corresponding to an estimated MTBF of 9.1 years (4 years), a supply voltage of 3.3 V and series terminated transmission line or capacitive loading. Depending on a given set of these operating conditions and the available device convection, a decision on the maximum operating frequency can be made.

Figure 7. Maximum MPC9448 Frequency, V<sub>CC</sub> = 3.3 V, MTBF 9.1 Years, Driving Series Terminated transmission lines, 2s2p board

Figure 8. Maximum MPC9448 frequency, V<sub>CC</sub> = 3.3 V, MTBF 9.1 Years, 4 pF Load per Line, 2s2p Board

Figure 9. No maximum Frequency Limitation for V<sub>CC</sub> = 3.3 V, MTBF 4 Years, Driving Series Terminated Transmission Lines, 2s2p Board

Figure 10. Maximum MPC9448 Frequency, V<sub>CC</sub> = 3.3 V, MTBF 4 Years, 4 pF Load per Line, 2s2p Board

# The Following Figures Illustrate the Measurement Reference for the MPC9448 Clock Driver Circuit

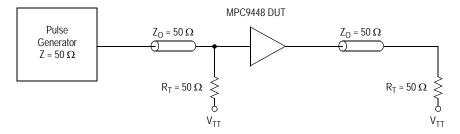

Figure 11. CCLK MPC9448 AC Test Reference for  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 2.5 V

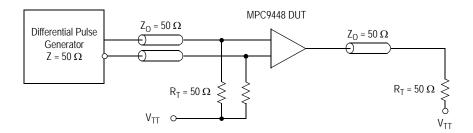

Figure 12. PCLK MPC9448 AC Test Reference

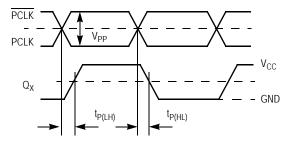

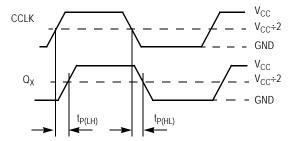

Figure 13. Propagation Delay (tPD) Test Reference

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device.

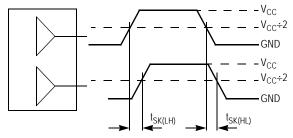

Figure 15. Output-to-Output Skew t<sub>SK(LH, HL)</sub>

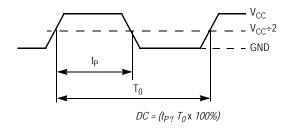

The time from the output controlled edge to the noncontrolled edge, divided by the time between output controlled edges, expressed as a percentage.

Figure 17. Output Duty Cycle (DC)

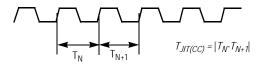

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs.

Figure 19. Cycle-to-Cycle Jitter

Figure 14. Propagation Delay (tPD) Test Reference

Figure 16. Output Pulse Skew (t<sub>SK(P)</sub>) Test Reference

Figure 18. Output Transition Time Test Reference

Figure 20. Setup and Hold Time (t<sub>S</sub>, t<sub>H</sub>) Test Reference

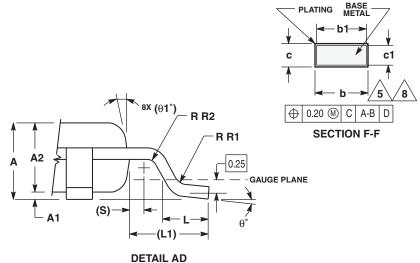

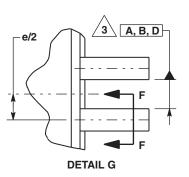

#### PACKAGE DIMENSIONS

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DATUMS A, B, AND D TO BE DETERMINED AT DATUM PLANE H.

4. DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE C.

5. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. AND SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM b DIMENSION BY MORE THAN 0.08-mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND DAJACENT LEAD OR PROTRUSION: 0.07-mm.

6. DIMENSIONS DI AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25-mm PER SIDE. DI AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

2. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

8. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1-mm AND 0.25-mm FROM THE LEAD TIP.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 1.40        | 1.60 |  |  |  |

| A1  | 0.05        | 0.15 |  |  |  |

| A2  | 1.35        | 1.45 |  |  |  |

| b   | 0.30        | 0.45 |  |  |  |

| b1  | 0.30        | 0.40 |  |  |  |

| С   | 0.09        | 0.20 |  |  |  |

| c1  | 0.09        | 0.16 |  |  |  |

| D   | 9.00        | BSC  |  |  |  |

| D1  | 7.00        | BSC  |  |  |  |

| е   | 0.80        | BSC  |  |  |  |

| Е   | 9.00        | BSC  |  |  |  |

| E1  | 7.00        | BSC  |  |  |  |

| L   | 0.50        | 0.70 |  |  |  |

| L1  |             | REF  |  |  |  |

| q   | 0°          | 7°   |  |  |  |

| q1  | 12          | REF  |  |  |  |

| R1  | 0.08        | 0.20 |  |  |  |

| R2  | 0.08        |      |  |  |  |

| S   | 0.20        | REF  |  |  |  |

**CASE 873A-03 ISSUE B** 32-LEAD LQFP PACKAGE

# **Revision History Sheet**

| Rev | Table | Page | Description of Change                                                                 | Date     |

|-----|-------|------|---------------------------------------------------------------------------------------|----------|

| 7   |       | 1    | NRND – Not Recommend for New Designs                                                  | 12/21/12 |

| 7   |       | 1    | Removed NRND - Not Recommended for New Designs                                        | 2/13/15  |

| 7   |       | 1    | Product Discontinuation Notice - Last time buy expires September 7, 2016. PDN N-16-02 | 3/15/16  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

# **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/