# Quad Digital Potentiometer (POT) with 256 Taps and I<sup>2</sup>C Interface

# Description

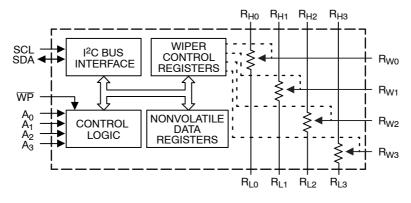

The CAT5259 is four digital POTs integrated with control logic and 16 bytes of NVRAM memory. Each digital POT consists of a series of resistive elements connected between two externally accessible end points. The tap points between each resistive element are connected to the wiper outputs with CMOS switches. A separate 8-bit control register (WCR) independently controls the wiper tap switches for each digital POT. Associated with each wiper control register are four 8-bit non-volatile memory data registers (DR) used for storing up to four wiper settings. Writing to the wiper control register or any of the non-volatile data registers is via a 1<sup>2</sup>C serial bus. On power-up, the contents of the first data register (DR0) for each of the four potentiometers is automatically loaded into its respective wiper control registers.

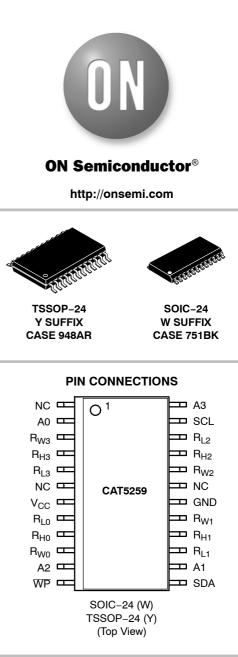

The CAT5259 can be used as a potentiometer or as a two terminal, variable resistor. It is intended for circuit level or system level adjustments in a wide variety of applications. It is available in the 0°C to 70°C commercial and -40°C to 85°C industrial operating temperature ranges and offered in a 24-lead SOIC and TSSOP package.

# Features

- Four Linear Taper Digital Potentiometers

- 256 Resistor Taps per Potentiometer

- End to End Resistance 50 k $\Omega$  or 100 k $\Omega$

- Potentiometer Control and Memory Access via I<sup>2</sup>C Interface

- Low Wiper Resistance, Typically 100  $\Omega$

- Nonvolatile Memory Storage for up to Four Wiper Settings for Each Potentiometer

- · Automatic Recall of Saved Wiper Settings at Power Up

- 2.5 to 6.0 V Operation

- Standby Current less than 1 µA

- 1,000,000 Nonvolatile WRITE Cycles

- 100 Year Nonvolatile Memory Data Retention

- 24-lead SOIC and 24-lead TSSOP Packages

- Industrial Temperature Range

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

1

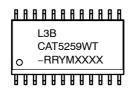

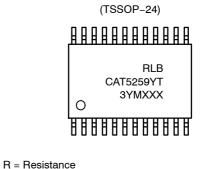

# MARKING DIAGRAMS

$\begin{array}{l} {\sf L} = {\sf Assembly \ Location} \\ {\sf 3} = {\sf Lead \ Finish - Matte-Tin} \\ {\sf B} = {\sf Product \ Revision \ (Fixed \ as "B")} \\ {\sf CAT5259W} = {\sf Device \ Code} \\ {\sf T} = {\sf Temperature \ Range \ (I = {\sf Industrial})} \\ {\sf -} = {\sf Dash} \\ {\sf RR} = {\sf Resistance} \\ {\sf 50} = {\sf 50 \ K\Omega} \\ {\sf 00} = {\sf 100 \ K\Omega} \\ {\sf Y} = {\sf Production \ Year \ (Last \ Digit)} \\ {\sf M} = {\sf Production \ Month \ (1-9, \ O, \ N, \ D)} \\ {\sf XXXX} = {\sf Last \ Four \ Digits \ of \ Assembly \ Lot \ Number} \end{array}$

$\begin{array}{l} 4 = 50 \ \text{K}\Omega \\ 5 = 100 \ \text{K}\Omega \\ \text{L} = \text{Assembly Location} \\ \text{B} = \text{Product Revision (Fixed as "B")} \\ \text{CAT5259Y} = \text{Device Code} \\ \text{T} = \text{Temperature Range (I = Industrial)} \\ \text{3} = \text{Lead Finish} - \text{Matte-Tin} \\ \text{Y} = \text{Production Year (Last Digit)} \\ \text{M} = \text{Production Month (1-9, O, N, D)} \\ \text{XXX} = \text{Last Three Digits of Assembly Lot Number} \end{array}$

# **PIN DESCRIPTIONS**

# Table 1. PIN DESCRIPTIONS

| Pin # | Name            | Function                                       |

|-------|-----------------|------------------------------------------------|

| 1     | NC              | No Connect                                     |

| 2     | A0              | Device Address, LSB                            |

| 3     | R <sub>W3</sub> | Wiper Terminal for Potentiometer 3             |

| 4     | R <sub>H3</sub> | High Reference Terminal for<br>Potentiometer 3 |

| 5     | R <sub>L3</sub> | Low Reference Terminal for Potentiometer 3     |

| 6     | NC              | No Connect                                     |

| 7     | V <sub>CC</sub> | Supply Voltage                                 |

| 8     | R <sub>L0</sub> | Low Reference Terminal for Potentiometer 0     |

| 9     | R <sub>H0</sub> | High Reference Terminal for<br>Potentiometer 0 |

| 10    | R <sub>W0</sub> | Wiper Terminal for Potentiometer 0             |

| 11    | A2              | Device Address                                 |

| 12    | WP              | Write Protection                               |

| 13    | SDA             | Serial Data Input/Output                       |

| 14    | A1              | Device Address                                 |

| 15    | R <sub>L1</sub> | Low Reference Terminal for Potentiometer 1     |

| 16    | R <sub>H1</sub> | High Reference Terminal for<br>Potentiometer 1 |

| 17    | R <sub>W1</sub> | Wiper Terminal for Potentiometer 1             |

| 18    | GND             | Ground                                         |

| 19    | NC              | No Connect                                     |

| 20    | R <sub>W2</sub> | Wiper Terminal for Potentiometer 2             |

| 21    | R <sub>H2</sub> | High Reference Terminal for<br>Potentiometer 2 |

| 22    | R <sub>L2</sub> | Low Reference Terminal for Potentiometer 2     |

| 23    | SCL             | Bus Serial Clock                               |

| 24    | A3              | Device Address                                 |

# **SCL: Serial Clock**

The CAT5259 serial clock input pin is used to clock all data transfers into or out of the device.

# **SDA: Serial Data**

The CAT5259 bidirectional serial data pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wire-Ored with the other open drain or open collector I/Os.

# A0, A1, A2, A3: Device Address Inputs

These inputs set the device address when addressing multiple devices. A total of sixteen devices can be addressed on a single bus. A match in the slave address must be made with the address input in order to initiate communication with the CAT5259.

# **R<sub>H</sub>**, **R<sub>L</sub>**: Resistor End Points

The four sets of  $R_H$  and  $R_L$  pins are equivalent to the terminal connections on a mechanical potentiometer.

#### **R<sub>W</sub>: Wiper**

The four  $R_W$  pins are equivalent to the wiper terminal of a mechanical potentiometer.

# **WP**: Write Protect Input

The  $\overline{WP}$  pin when tied low prevents non-volatile writes to the device (change of wiper control register is allowed) and when tied high or left floating normal read/write operations are allowed. See Write Protection on page 7 for more details.

# **DEVICE OPERATION**

The CAT5259 is four resistor arrays integrated with a  $I^2C$  serial interface logic, four 8-bit wiper control registers and sixteen 8-bit, non-volatile memory data registers. Each resistor array contains 255 separate resistive elements connected in series. The physical ends of each array are equivalent to the fixed terminals of a mechanical potentiometer ( $R_H$  and  $R_L$ ). The tap positions between and at the ends of the series resistors are connected to the output wiper terminals ( $R_W$ ) by a CMOS transistor switch. Only

one tap point for each potentiometer is connected to its wiper terminal at a time and is determined by the value of the wiper control register. Data can be read or written to the wiper control registers or the non-volatile memory data registers via the  $I^2C$  bus. Additional instructions allow data to be transferred between the wiper control registers and each respective potentiometer's non-volatile data registers. Also, the device can be instructed to operate in an "increment/ decrement" mode.

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Parameters                                                      | Ratings                        | Units |

|-----------------------------------------------------------------|--------------------------------|-------|

| Temperature Under Bias                                          | -55 to +125                    | °C    |

| Storage Temperature                                             | -65 to +150                    | °C    |

| Voltage on Any Pin with Respect to V <sub>SS</sub> (Notes 1, 2) | -2.0 to +V <sub>CC</sub> + 2.0 | V     |

| V <sub>CC</sub> with Respect to Ground                          | -2.0 to +7.0                   | V     |

| Package Power Dissipation Capability (T <sub>A</sub> = 25°C)    | 1.0                            | W     |

| Lead Soldering Temperature (10 s)                               | 300                            | °C    |

| Wiper Current                                                   | ±6                             | mA    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

The minimum DC input voltage is -0.5 V. During transitions, inputs may undershoot to -2.0 V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5 V, which may overshoot to V<sub>CC</sub> +2.0 V for periods of less than 20 ns.

Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1 V to V<sub>CC</sub> +1 V.

#### **Table 3. RECOMMENDED OPERATING CONDITIONS**

| Parameters             | Ratings    | Units |

|------------------------|------------|-------|

| V <sub>CC</sub>        | +2.5 to +6 | V     |

| Industrial Temperature | -40 to +85 | °C    |

#### Table 4. POTENTIOMETER CHARACTERISTICS (Over recommended operating conditions unless otherwise stated.)

|                     |                                                     |                                                           |                 | Limits   |                 |                 |

|---------------------|-----------------------------------------------------|-----------------------------------------------------------|-----------------|----------|-----------------|-----------------|

| Symbol              | Parameter                                           | Test Conditions                                           | Min             | Тур      | Max             | Units           |

| R <sub>POT</sub>    | Potentiometer Resistance (100 k $\Omega$ )          |                                                           |                 | 100      |                 | kΩ              |

| R <sub>POT</sub>    | Potentiometer Resistance (50 k $\Omega$ )           |                                                           |                 | 50       |                 | kΩ              |

|                     | Potentiometer Resistance Tolerance                  |                                                           |                 |          | ±20             | %               |

|                     | R <sub>POT</sub> Matching                           |                                                           |                 |          | 1               | %               |

|                     | Power Rating                                        | 25°C, each pot                                            |                 |          | 50              | mW              |

| I <sub>W</sub>      | Wiper Current                                       |                                                           |                 |          | +3              | mA              |

| R <sub>W</sub>      | Wiper Resistance                                    | $I_{W} = \pm 3 \text{ mA} @ V_{CC} = 3 \text{ V}$         |                 | 200      | 300             | Ω               |

| R <sub>W</sub>      | Wiper Resistance                                    | $I_{W} = \pm 3 \text{ mA} @ V_{CC} = 5 \text{ V}$         |                 | 100      | 150             | Ω               |

| V <sub>TERM</sub>   | Voltage on any R <sub>H</sub> or R <sub>L</sub> Pin | V <sub>SS</sub> = 0 V                                     | V <sub>SS</sub> |          | V <sub>CC</sub> | V               |

| V <sub>N</sub>      | Noise                                               | (Note 3)                                                  |                 |          |                 | nV√Hz           |

|                     | Resolution                                          |                                                           |                 | 0.4      |                 | %               |

|                     | Absolute Linearity (Note 4)                         | $R_{W(n)(actual)} - R_{(n)(expected)}$<br>(Note 7)        |                 |          | ±1              | LSB<br>(Note 6) |

|                     | Relative Linearity (Note 5)                         | R <sub>W(n+1)</sub> -[R <sub>W(n)+LSB</sub> ]<br>(Note 7) |                 |          | ±0.2            | LSB<br>(Note 6) |

| TC <sub>RPOT</sub>  | Temperature Coefficient of R <sub>POT</sub>         | (Note 3)                                                  |                 | ±300     |                 | ppm/°C          |

| TC <sub>RATIO</sub> | Ratiometric Temp. Coefficient                       | (Note 3)                                                  |                 |          | 20              | ppm/°C          |

| $C_H/C_L/C_W$       | Potentiometer Capacitances                          | (Note 3)                                                  |                 | 10/10/25 |                 | pF              |

| fc                  | Frequency Response                                  | $R_{POT}$ = 50 k $\Omega$ (Note 3)                        |                 | 0.4      |                 | MHz             |

3. This parameter is tested initially and after a design or process change that affects the parameter.

4. Absolute linearity is utilized to determine actual wiper voltage versus expected voltage as determined by wiper position when used as a

Absolute intearity is utilized to determine data. https://www.absolute.intearity is utilized to determine the actual change in voltage between two successive tap positions when used as a potentiometer. It is a measure of the error in step size.

6. LSB =  $R_{TOT}$  / 255 or ( $R_H - R_L$ ) / 255, single pot 7. n = 0, 1, 2, ..., 255

| Table 5. D.C. OPERATING CHARACTERISTICS | $V_{CC} = +2.5 \text{ V to } +6.0 \text{ V}$ , unless otherwise specified.) |

|-----------------------------------------|-----------------------------------------------------------------------------|

|-----------------------------------------|-----------------------------------------------------------------------------|

| Symbol           | Parameter                                  | Test Conditions                                                               | Min                   | Max                   | Units |

|------------------|--------------------------------------------|-------------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| I <sub>CC1</sub> | Power Supply Current                       | f <sub>SCL</sub> = 400 kHz, SDA = Open<br>V <sub>CC</sub> = 6 V, Inputs = GND |                       | 1                     | mA    |

| I <sub>CC2</sub> | Power Supply Current<br>Non-volatile WRITE | f <sub>SCK</sub> = 400 kHz, SDA Open<br>V <sub>CC</sub> = 6 V, Input = GND    |                       | 5                     | mA    |

| I <sub>SB</sub>  | Standby Current (V <sub>CC</sub> = 5 V)    | $V_{IN} = GND \text{ or } V_{CC}, \text{ SDA} = Open$                         |                       | 5                     | μA    |

| Ι <sub>LI</sub>  | Input Leakage Current                      | $V_{IN} = GND$ to $V_{CC}$                                                    |                       | 10                    | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current                     | $V_{OUT} = GND$ to $V_{CC}$                                                   |                       | 10                    | μΑ    |

| V <sub>IL</sub>  | Input Low Voltage                          |                                                                               | -1                    | V <sub>CC</sub> x 0.3 | V     |

| VIH              | Input High Voltage                         |                                                                               | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 1.0 | V     |

| V <sub>OL1</sub> | Output Low Voltage (V <sub>CC</sub> = 3 V) | I <sub>OL</sub> = 3 mA                                                        |                       | 0.4                   | V     |

# Table 6. CAPACITANCE (T<sub>A</sub> = 25°C, f = 1.0 MHz, V<sub>CC</sub> = 5 V)

| Symbol                    | Test                                        | Conditions            | Max | Units |

|---------------------------|---------------------------------------------|-----------------------|-----|-------|

| C <sub>I/O</sub> (Note 8) | Input/Output Capacitance (SDA)              | $V_{I/O} = 0 V$       | 8   | pF    |

| C <sub>IN</sub> (Note 8)  | Input Capacitance (A0, A1, A2, A3, SCL, WP) | V <sub>IN</sub> = 0 V | 6   | pF    |

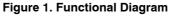

# Table 7. A.C. CHARACTERISTICS

|                           |                                                               | 2.5 V – 6.0 V |     |       |  |

|---------------------------|---------------------------------------------------------------|---------------|-----|-------|--|

| Symbol                    | Parameter                                                     | Min           | Max | Units |  |

| f <sub>SCL</sub>          | Clock Frequency                                               |               | 400 | kHz   |  |

| T <sub>I</sub> (Note 8)   | Noise Suppression Time Constant at SCL, SDA Inputs            |               | 200 | ns    |  |

| t <sub>AA</sub>           | SLC Low to SDA Data Out and ACK Out                           |               | 1   | μs    |  |

| t <sub>BUF</sub> (Note 8) | Time the bus must be free before a new transmission can start | 1.2           |     | μs    |  |

| t <sub>HD:STA</sub>       | Start Condition Hold Time                                     | 0.6           |     | μs    |  |

| t <sub>LOW</sub>          | Clock Low Period                                              | 1.2           |     | μs    |  |

| t <sub>HIGH</sub>         | Clock High Period                                             | 0.6           |     | μs    |  |

| t <sub>SU:STA</sub>       | Start Condition SetupTime (for a Repeated Start Condition)    | 0.6           |     | μs    |  |

| t <sub>HD:DAT</sub>       | Data in Hold Time                                             | 0             |     | ns    |  |

| t <sub>SU:DAT</sub>       | Data in Setup Time                                            | 50            |     | ns    |  |

| t <sub>R</sub> (Note 8)   | SDA and SCL Rise Time                                         |               | 0.3 | μs    |  |

| t <sub>F</sub> (Note 8)   | SDA and SCL Fall Time                                         |               | 300 | ns    |  |

| t <sub>SU:STO</sub>       | Stop Condition Setup Time                                     | 0.6           |     | μs    |  |

| t <sub>DH</sub>           | Data Out Hold Time                                            | 100           |     | ns    |  |

# Table 8. POWER UP TIMING (Notes 8, 9)

| Symbol           | Parameter                   | Max | Units |

|------------------|-----------------------------|-----|-------|

| t <sub>PUR</sub> | Power-up to Read Operation  | 1   | ms    |

| t <sub>PUW</sub> | Power-up to Write Operation | 1   | ms    |

8. This parameter is tested initially and after a design or process change that affects the parameter.

9. t<sub>PUR</sub> and t<sub>PUW</sub> are delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated.

# Table 9. WIPER TIMING

| Symbol            | Parameter                                     | Min | Min Max |    |

|-------------------|-----------------------------------------------|-----|---------|----|

| t <sub>WRPO</sub> | Wiper Response Time After Power Supply Stable | 5   | 10      | μs |

| twRL              | Wiper Response Time After Instruction Issued  | 5   | 10      | μs |

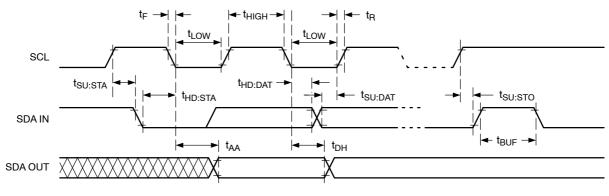

#### Table 10. WRITE CYCLE LIMITS (Note 10)

| Symbol          | Parameter        | Max | Units |

|-----------------|------------------|-----|-------|

| t <sub>WR</sub> | Write Cycle Time | 5   | ms    |

#### Table 11. RELIABILITY CHARACTERISTICS

| Symbol                     | Parameter          | Reference Test Method         | Min       | Max | Units       |

|----------------------------|--------------------|-------------------------------|-----------|-----|-------------|

| N <sub>END</sub> (Note 11) | Endurance          | MIL-STD-883, Test Method 1033 | 1,000,000 |     | Cycles/Byte |

| T <sub>DR</sub> (Note 11)  | Data Retention     | MIL-STD-883, Test Method 1008 | 100       |     | Years       |

| V <sub>ZAP</sub> (Note 11) | ESD Susceptibility | MIL-STD-883, Test Method 3015 | 2000      |     | V           |

| I <sub>LTH</sub> (Note 11) | Latch-up           | JEDEC Standard 17             | 100       |     | mA          |

10. The write cycle is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.

11. This parameter is tested initially and after a design or process change that affects the parameter.

# Figure 2. Bus Timing

# SERIAL BUS PROTOCOL

The following defines the features of the I<sup>2</sup>C bus protocol:

- 1. Data transfer may be initiated only when the bus is not busy.

- 2. During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock is high will be interpreted as a START or STOP condition.

The device controlling the transfer is a master, typically a processor or controller, and the device being controlled is the slave. The master will always initiate data transfers and provide the clock for both transmit and receive operations. Therefore, the CAT5259 will be considered a slave device in all applications.

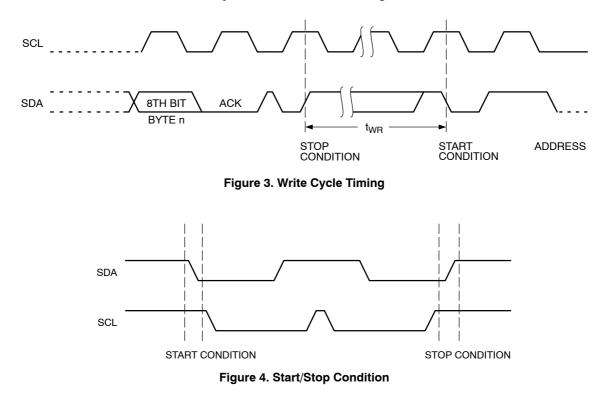

# **START Condition**

The START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The CAT5259 monitors the SDA and SCL lines and will not respond until this condition is met.

#### **STOP Condition**

A LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.

# **DEVICE ADDRESSING**

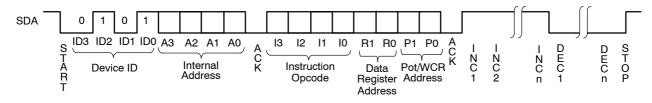

The bus Master begins a transmission by sending a START condition. The Master then sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 0101 for the CAT5259 (see Figure 6). The next four significant bits (A3, A2, A1, A0) are the device address bits and define which device the Master is accessing. Up to sixteen devices

may be individually addressed by the system. Typically, +5 V and ground are hard-wired to these pins to establish the device's address.

After the Master sends a START condition and the slave address byte, the CAT5259 monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slave address.

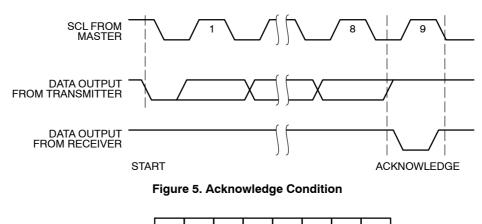

#### Acknowledge

After a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledging device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.

The CAT5259 responds with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it

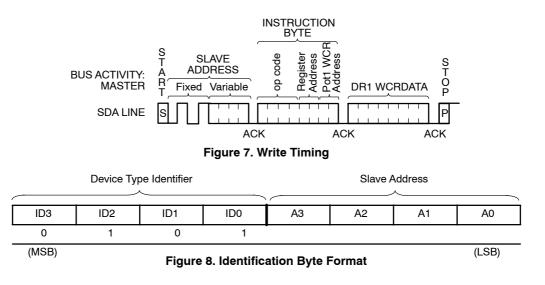

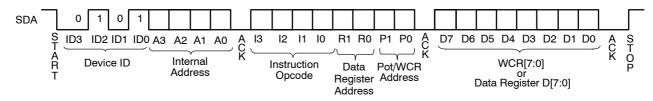

In the Write mode, the Master device sends the START condition and the slave address information to the Slave device. After the Slave generates an acknowledge, the Master sends the instruction byte that defines the requested operation of CAT5259. The instruction byte consist of a four-bit opcode followed by two register selection bits and two pot selection bits. After receiving another acknowledge from the Slave, the Master device transmits the data to be written into the selected register. The CAT5259 acknowledges once more and the Master generates the STOP condition, at which time if a non-volatile data register is being selected, the device begins an internal programming cycle to non-volatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.

#### Acknowledge Polling

The disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host's write operation, the responds with an acknowledge after receiving each 8-bit byte.

When the CAT5259 is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the CAT5259 will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.

# WRITE OPERATIONS

CAT5259 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address. If the CAT5259 is still busy with the write operation, no ACK will be returned. If the CAT5259 has completed the write operation, an ACK will be returned and the host can then proceed with the next instruction operation.

#### Write Protection

The Write Protection feature allows the user to protect against inadvertent programming of the non-volatile data registers. If the  $\overline{WP}$  pin is tied to LOW, the data registers are protected and become read only. Similarly, the  $\overline{WP}$  pin is going low after start will interrupt non-volatile write to data registers, while  $\overline{WP}$  pin going low after an internal write cycle has started will have no effect on any write operation. The CAT5259 will accept both slave addresses and instructions, but the data registers are protected from programming by the device's failure to send an acknowledge after data is received.

**CAT5259** 0 1 0 1 A3 A2 A1 A0

\* A0, A1, A2 and A3 correspond to pin A0, A1, A2 and A3 of the device. \*\* A0, A1, A2 and A3 must compare to its corresponding hard wired input pins.

Figure 6. Slave Address Bits

# INSTRUCTION AND REGISTER DESCRIPTION

#### **Slave Address Byte**

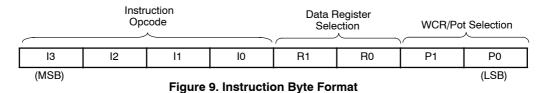

The first byte sent to the CAT5259 from the master/processor is called the Slave Address Byte. The most significant four bits of the slave address are a device type identifier. These bits for the CAT5259 are fixed at 0101[B] (refer to Figure 8).

The next four bits, A3 – A0, are the internal slave address and must match the physical device address which is defined by the state of the A3 – A0 input pins for the CAT5259 to successfully continue the command sequence. Only the device which slave address matches the incoming device address sent by the master executes the instruction. The A3 – A0 inputs can be actively driven by CMOS input signals or tied to V<sub>CC</sub> or V<sub>SS</sub>.

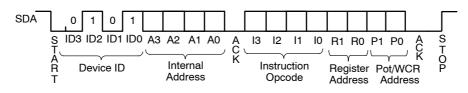

#### Instruction Byte

The next byte sent to the CAT5259 contains the instruction and register pointer information. The four most significant bits used provide the instruction opcode I3 - I0. The R1 and R0 bits point to one of the four data registers of each associated potentiometer. The least two significant bits point to one of four Wiper Control Registers. The format is shown in Figure 9.

#### Table 12. DATA REGISTER SELECTION

| Data Register Selected | R1 | R0 |

|------------------------|----|----|

| DR0                    | 0  | 0  |

| DR1                    | 0  | 1  |

| DR2                    | 1  | 0  |

| DR3                    | 1  | 1  |

### WIPER CONTROL AND DATA REGISTERS

#### Wiper Control Register (WCR)

The CAT5259 contains four 8-bit Wiper Control Registers, one for each potentiometer. The Wiper Control Register output is decoded to select one of 256 switches along its resistor array. The contents of the WCR can be altered in four ways: it may be written by the host via Write Wiper Control Register instruction; it may be written by transferring the contents of one of four associated Data Registers via the XFR Data Register instruction, it can be modified one step at a time by the Increment/decrement instruction (see Instruction section for more details). Finally, it is loaded with the content of its data register zero (DR0) upon power-up.

The Wiper Control Register is a volatile register that loses its contents when the CAT5259 is powered-down. Although the register is automatically loaded with the value in DR0 upon power-up, this may be different from the value present at power-down.

#### Data Registers (DR)

Each potentiometer has four 8-bit non-volatile Data Registers. These can be read or written directly by the host.

Data can also be transferred between any of the four Data Registers and the associated Wiper Control Register. Any data changes in one of the Data Registers is a non-volatile operation and will take a maximum of 10 ms.

If the application does not require storage of multiple settings for the potentiometer, the Data Registers can be used as standard memory locations for system parameters or user preference data.

#### Instructions

Four of the nine instructions are three bytes in length. These instructions are:

- **Read Wiper Control Register** read the current wiper position of the selected potentiometer in the WCR

- Write Wiper Control Register change current wiper position in the WCR of the selected potentiometer

- **Read Data Register** read the contents of the selected Data Register

- Write Data Register write a new value to the selected Data Register

|                                                          |    |    |    |    | Instr | uctior | n Set   |         |                                                                                                                                     |

|----------------------------------------------------------|----|----|----|----|-------|--------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                                              | 13 | 12 | 11 | 10 | R1    | R0     | WCR1/P1 | WCR0/P0 | Operation                                                                                                                           |

| Read Wiper Control<br>Register                           | 1  | 0  | 0  | 1  | 0     | 0      | 1/0     | 1/0     | Read the contents of the Wiper Control<br>Register pointed to by P1-P0                                                              |

| Write Wiper Control<br>Register                          | 1  | 0  | 1  | 0  | 0     | 0      | 1/0     | 1/0     | Write new value to the Wiper Control Register<br>pointed to by P1-P0                                                                |

| Read Data Register                                       | 1  | 0  | 1  | 1  | 1/0   | 1/0    | 1/0     | 1/0     | Read the contents of the Data Register pointed to by P1-P0 and R1-R0                                                                |

| Write Data Register                                      | 1  | 1  | 0  | 0  | 1/0   | 1/0    | 1/0     | 1/0     | Write new value to the Data Register pointed to<br>by P1-P0 and R1-R0                                                               |

| XFR Data Register to<br>Wiper Control Register           | 1  | 1  | 0  | 1  | 1/0   | 1/0    | 1/0     | 1/0     | Transfer the contents of the Data Register<br>pointed to by P1-P0 and R1-R0 to its<br>associated Wiper Control Register             |

| XFR Wiper Control<br>Register to Data<br>Register        | 1  | 1  | 1  | 0  | 1/0   | 1/0    | 1/0     | 1/0     | Transfer the contents of the Wiper Control<br>Register pointed to by P1-P0 to the Data<br>Register pointed to by R1-R0              |

| Gang XFR Data<br>Registers to Wiper<br>Control Registers | 0  | 0  | 0  | 1  | 1/0   | 1/0    | 0       | 0       | Transfer the contents of the Data Registers<br>pointed to by R1-R0 of all four pots to their<br>respective Wiper Control Registers  |

| Gang XFR Wiper Control<br>Registers to Data<br>Register  | 1  | 0  | 0  | 0  | 1/0   | 1/0    | 0       | 0       | Transfer the contents of both Wiper Control<br>Registers to their respective data Registers<br>pointed to by R1-R0 of all four pots |

| Increment/Decrement<br>Wiper Control Register            | 0  | 0  | 1  | 0  | 0     | 0      | 1/0     | 1/0     | Enable Increment/decrement of the Control<br>Latch pointed to by P1–P0                                                              |

Table 13. INSTRUCTION SET (Note: 1/0 = data is one or zero.)

The basic sequence of the three byte instructions is illustrated in Figure 11. These three-byte instructions exchange data between the WCR and one of the Data Registers. The WCR controls the position of the wiper. The response of the wiper to this action will be delayed by  $t_{WR}$ . A transfer from the WCR (current wiper position), to a Data Register is a write to non-volatile memory and takes a minimum of  $t_{WR}$  to complete. The transfer can occur between one of the four potentiometers and one of its associated registers; or the transfer can occur between all potentiometers and one associated register.

Four instructions require a two-byte sequence to complete, as illustrated in Figure 10. These instructions transfer data between the host/processor and the CAT5259; either between the host and one of the data registers or directly between the host and the Wiper Control Register. These instructions are:

- XFR Data Register to Wiper Control Register This transfers the contents of one specified Data Register to the associated Wiper Control Register.

- XFR Wiper Control Register to Data Register This transfers the contents of the specified Wiper

Control Register to the specified associated Data Register.

- Gang XFR Data Register to Wiper Control Register This transfers the contents of all specified Data Registers to the associated Wiper Control Registers.

- Gang XFR Wiper Counter Register to Data Register This transfers the contents of all Wiper Control Registers to the specified associated Data Registers.

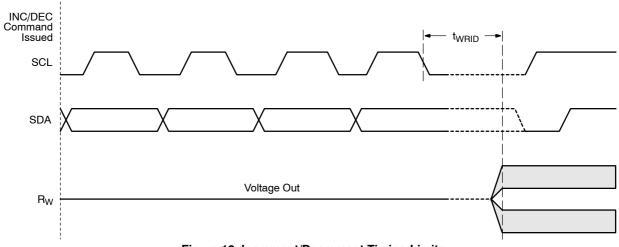

# Increment/Decrement Command

The final command is Increment/Decrement (Figures 12 and 13). The Increment/Decrement command is different from the other commands. Once the command is issued and the CAT5259 has responded with an acknowledge, the master can clock the selected wiper up and/or down in one segment steps; thereby providing a fine tuning capability to the host. For each SCL clock pulse ( $t_{HIGH}$ ) while SDA is HIGH, the selected wiper will move one resistor segment towards the R<sub>H</sub> terminal. Similarly, for each SCL clock pulse while SDA is LOW, the selected wiper will move one resistor segment towards the RL terminal.

See Instructions format for more detail.

Figure 10. Two-byte Instruction Sequence

Figure 11. Three-byte Instruction Sequence

Figure 12. Increment/Decrement Instruction Sequence

Figure 13. Increment/Decrement Timing Limits

# **INSTRUCTION FORMAT**

# Table 14. READ WIPER CONTROL REGISTER (WCR)

| S                |   |   | DE\ | /ICE |    | RESS | SES |    | A |   |   |   | INS | TRUC | TION |    |    | A      |   |   |   | DA | TA |   |   |   | A      | S           |

|------------------|---|---|-----|------|----|------|-----|----|---|---|---|---|-----|------|------|----|----|--------|---|---|---|----|----|---|---|---|--------|-------------|

| T<br>A<br>R<br>T | 0 | 1 | 0   | 1    | A3 | A2   | A1  | A0 | K | 1 | 0 | 0 | 1   | 0    | 0    | P1 | P0 | С<br>К | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | С<br>К | Т<br>О<br>Р |

# Table 15. WRITE WIPER CONTROL REGISTER (WCR)

| S                |   |   | DE۱ | /ICE | ADD | RES | SES |    | A      |   |   |   | INS | TRUC | TION |    |    | A      |   |   |   | DA | TA |   |   |   | A      | S           |

|------------------|---|---|-----|------|-----|-----|-----|----|--------|---|---|---|-----|------|------|----|----|--------|---|---|---|----|----|---|---|---|--------|-------------|

| T<br>A<br>R<br>T | 0 | 1 | 0   | 1    | A3  | A2  | A1  | A0 | С<br>К | 1 | 0 | 1 | 0   | 0    | 0    | P1 | P0 | С<br>К | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | с<br>К | r<br>O<br>P |

# Table 16. READ DATA REGISTER (DR)

| S           |   |   | DE\ | /ICE | ADD | RESS | SES |    | A |   |   |   | INS | TRUC | TION |    |    | A        |   |   |   | DA | TA |   |   |   | A      | S      |

|-------------|---|---|-----|------|-----|------|-----|----|---|---|---|---|-----|------|------|----|----|----------|---|---|---|----|----|---|---|---|--------|--------|

| A<br>R<br>T | 0 | 1 | 0   | 1    | A3  | A2   | A1  | A0 | K | 1 | 0 | 1 | 1   | R1   | R0   | P1 | P0 | с к<br>К | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | С<br>К | O<br>P |

# Table 17. WRITE DATA REGISTER (DR)

| S                |   |   | DE\ | /ICE | E ADD | RESS | SES |    | A |   |   |   | INS | TRUC | TION |    |    | A |   |   |   | DA | TA |   |   |   | A | S           |

|------------------|---|---|-----|------|-------|------|-----|----|---|---|---|---|-----|------|------|----|----|---|---|---|---|----|----|---|---|---|---|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0   | 1    | AЗ    | A2   | A1  | A0 | K | 1 | 1 | 0 | 0   | R1   | R0   | P1 | P0 | K | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 | K | I<br>O<br>P |

# Table 18. GANG TRANSFER DATA REGISTER (DR)TO WIPER CONTROL REGISTER (WCR)

| S                |   |   | DE | VICE | EADD | RES | SES |    | Α  |   |   |   | INS | TRUC | TION |   |   | A | S           |

|------------------|---|---|----|------|------|-----|-----|----|----|---|---|---|-----|------|------|---|---|---|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0  | 1    | A3   | A2  | A1  | A0 | СК | 0 | 0 | 0 | 1   | R1   | R0   | 0 | 0 | K | I<br>O<br>P |

# Table 19. GANG TRANSFER WIPER CONTROL REGISTER (WCR) TO DATA REGISTER (DR)

| S                |   |   | DE | VICE | EADD | RESS | SES |    | A      |   |   |   | INS | TRUC | TION |   |   | A | S           |

|------------------|---|---|----|------|------|------|-----|----|--------|---|---|---|-----|------|------|---|---|---|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0  | 1    | A3   | A2   | A1  | A0 | С<br>К | 1 | 0 | 0 | 0   | R1   | R0   | 0 | 0 | ĸ | I<br>O<br>P |

# Table 20. TRANSFER WIPER CONTROL REGISTER (WCR) TO DATA REGISTER (DR)

| S                |   |   | DE | VICE | EADD | RES | SES |    | A |   |   |   | INS | TRUC | TION |    |    | A      | S           |

|------------------|---|---|----|------|------|-----|-----|----|---|---|---|---|-----|------|------|----|----|--------|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0  | 1    | A3   | A2  | A1  | A0 | K | 1 | 1 | 1 | 0   | R1   | R0   | P1 | P0 | с<br>К | I<br>O<br>P |

# Table 21. TRANSFER DATA REGISTER (DR) TO WIPER CONTROL REGISTER (WCR)

| S                |   |   | DE | VICE | EADD | RESS | SES |    | Α  |   |   |   | INS | TRUC | TION |    |    | A | S           |

|------------------|---|---|----|------|------|------|-----|----|----|---|---|---|-----|------|------|----|----|---|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0  | 1    | A3   | A2   | A1  | A0 | СК | 1 | 1 | 0 | 1   | R1   | R0   | P1 | P0 | K | I<br>O<br>P |

# Table 22. INCREMENT (I)/DECREMENT (D) WIPER CONTROL REGISTER (WCR)

| S                |   |   | DE\ | /ICE | ADD | RESS | SES |    | A |   |   |   | INS | TRUC | TION |    |    | Α |     |     | DATA |     |     | S           |

|------------------|---|---|-----|------|-----|------|-----|----|---|---|---|---|-----|------|------|----|----|---|-----|-----|------|-----|-----|-------------|

| I<br>A<br>R<br>T | 0 | 1 | 0   | 1    | A3  | A2   | A1  | A0 | ĸ | 0 | 0 | 1 | 0   | 0    | 0    | P1 | P0 | K | I/D | I/D |      | I/D | I/D | I<br>O<br>P |

NOTE: Any write or transfer to the Non-volatile Data Registers is followed by a high voltage cycle after a STOP has been issued.

# **Table 23. ORDERING INFORMATION**

| Orderable Part Number | Resistance (k $\Omega$ ) | Lead Finish | Package   | Shipping <sup>†</sup> |

|-----------------------|--------------------------|-------------|-----------|-----------------------|

| CAT5259WI-50-T1       | 50                       |             | SOIC      | 1000 / Tana & Daal    |

| CAT5259WI-00-T1       | 100                      |             | (Pb-Free) | 1000 / Tape & Reel    |

| CAT5259YI-50-T2       | 50                       |             | TSSOP     | 0000 / Tana & Daal    |

| CAT5259YI-00-T2       | 100                      | Matte-Tin   | (Pb-Free) | 2000 / Tape & Reel    |

| CAT5259WI50           | 50                       | Malle-III   | SOIC      | 01 Unite / Turka      |

| CAT5259WI00           | 100                      |             | (Pb-Free) | 31 Units / Tube       |

| CAT5259YI50           | 50                       | 1           | TSSOP     | 60 Unite / Turke      |

| CAT5259YI00           | 100                      | 1           | (Pb-Free) | 62 Units / Tube       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

12. For detailed information and a breakdown of device nomenclature and numbering systems, please see the ON Semiconductor Device Nomenclature document, TND310/D, available at <u>www.onsemi.com</u>.

13. All packages are RoHS-compliant (Lead-Free, Halogen-Free).

14. The standard lead finish is Matte-Tin.

15. For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

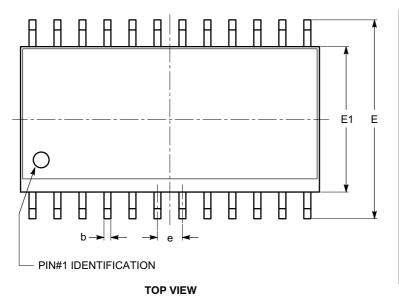

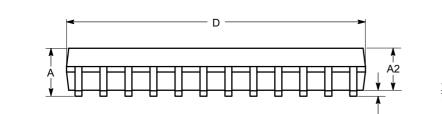

# PACKAGE DIMENSIONS

| SYMBOL | MIN   | NOM      | MAX   |

|--------|-------|----------|-------|

| А      | 2.35  |          | 2.65  |

| A1     | 0.10  |          | 0.30  |

| A2     | 2.05  |          | 2.55  |

| b      | 0.31  |          | 0.51  |

| с      | 0.20  |          | 0.33  |

| D      | 15.20 |          | 15.40 |

| E      | 10.11 |          | 10.51 |

| E1     | 7.34  |          | 7.60  |

| е      |       | 1.27 BSC |       |

| h      | 0.25  |          | 0.75  |

| L      | 0.40  |          | 1.27  |

| θ      | 0°    |          | 8°    |

| θ1     | 5°    |          | 15°   |

SIDE VIEW

θ1-

θ1

- h

h

#### Notes:

All dimensions are in millimeters. Angles in degrees.

Complies with JEDEC MS-013.

Á1

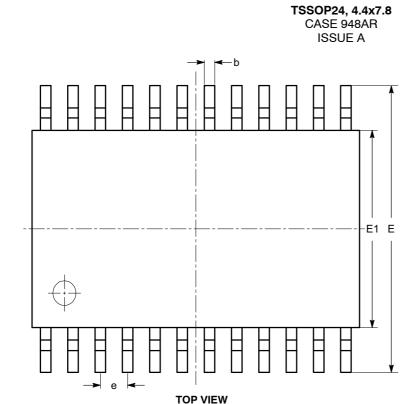

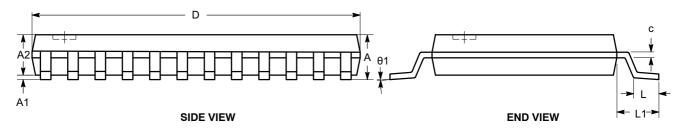

# PACKAGE DIMENSIONS

| SYMBOL | MIN      | NOM  | MAX  |

|--------|----------|------|------|

| А      |          |      | 1.20 |

| A1     | 0.05     |      | 0.15 |

| A2     | 0.80     |      | 1.05 |

| b      | 0.19     |      | 0.30 |

| с      | 0.09     |      | 0.20 |

| D      | 7.70     | 7.80 | 7.90 |

| E      | 6.25     | 6.40 | 6.55 |

| E1     | 4.30     | 4.40 | 4.50 |

| е      | 0.65 BSC |      |      |

| L      | 0.50     | 0.60 | 0.70 |

| L1     | 1.00 REF |      |      |

| θ      | 0°       |      | 8°   |

#### Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MO-153.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

#### N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative