**Data Sheet**

June 2006

**Features**

- Low jitter clock outputs suitable for OC-192, OC-48, OC-12, OC-3 and OC-1 SONET applications as defined in Telcordia GR-253-CORE

- Low jitter clock outputs suitable for STM-64, STM-16, STM-4 and STM-1 applications as defined in ITU-T G.813

- Provides one differential LVPECL output clock selectable to 19.44, 38.88, 77.76, 155.52 or 622.08 MHz

- Provides a single-ended CMOS output clock at 19.44 MHz

- Accepts a single-ended CMOS reference at 19.44 MHz or a differential LVDS, LVPECL or CML reference at 19.44 or 77.76 MHz

- · Provides a LOCK indication

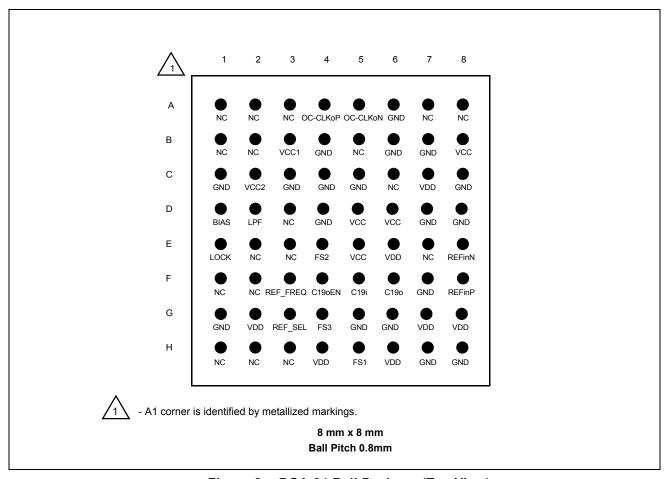

- 8 mm x 8 mm CABGA package

- 3.3 V supply

#### **Applications**

SONET/SDH line cards

#### **Ordering Information**

ZL30416GGG 64 Ball CABGA Trays, Bake & Drypack ZL30416GGG2 64 Ball CABGA\* Trays, Bake & Drypack \*Pb Free Tin/Silver/Copper

-40°C to +85°C

# **Description**

The ZL30416 is an Analog Phase-Locked Loop (APLL) designed to provide jitter attenuation and rate conversion for SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The ZL30416 generates low jitter output clocks suitable for Telcordia GR-253-CORE OC-192, OC-48, OC-12, OC-3, and OC-1 and ITU-T G.813 STM-64, STM-16, STM-4 and STM-1 applications.

The ZL30416 accepts a CMOS compatible reference at 19.44 MHz or a differential LVDS, LVPECL or CML reference at 19.44 or 77.76 MHz and generates a differential LVPECL output clock selectable to 19.44, 38.88, 77.76, 155.52 or 622.08 MHz and a single-ended CMOS clock at 19.44 MHz. The ZL30416 provides a lock indication.

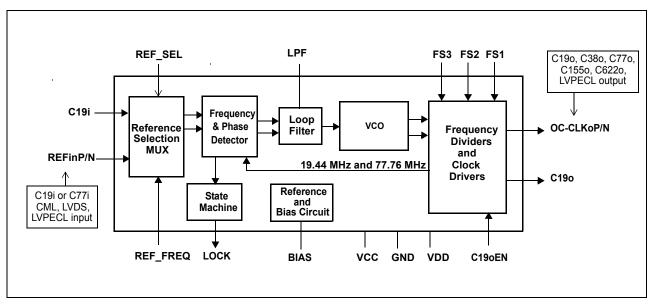

Figure 1 - Functional Block Diagram

Figure 2 - BGA 64 Ball Package (Top View)

# 1.0 Ball Description

#### **Ball Description Table**

| Ball #           | Name                 | Description                                                                                                                                                                                                                 |

|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2<br>A3     | NC                   | No internal bonding Connection. Leave unconnected.                                                                                                                                                                          |

| A4<br>A5         | OC-CLKoP<br>OC-CLKoN | SONET/SDH Clock (LVPECL Output). These outputs provide a selectable differential LVPECL clock at 19.44 Hz, 38.88 MHz, 77.76 MHz, 155.52 MHz, and 622.08 MHz. The output frequency is selected with FS3, FS2 and FS1 inputs. |

| A6               | GND                  | Ground. 0 volt                                                                                                                                                                                                              |

| A7, A8<br>B1, B2 | NC                   | No internal bonding Connection. Leave unconnected.                                                                                                                                                                          |

| В3               | VCC1                 | Positive Analog Power Supply. +3.3 V +/-10%                                                                                                                                                                                 |

| B4               | GND                  | Ground. 0 volt                                                                                                                                                                                                              |

| B5               | NC                   | No internal bonding Connection. Leave unconnected.                                                                                                                                                                          |

| B6, B7           | GND                  | Ground. 0 volt                                                                                                                                                                                                              |

# **Ball Description Table (continued)**

| Ball #         | Name              | Description                                                                                                                                                                                                                              |

|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B8             | VCC               | Positive Analog Power Supply. +3.3 V ±10%                                                                                                                                                                                                |

| C1             | GND               | Ground. 0 volt                                                                                                                                                                                                                           |

| C2             | VCC2              | Positive Analog Power Supply. +3.3 V ±10%                                                                                                                                                                                                |

| C3, C4<br>C5   | GND               | Ground. 0 volt                                                                                                                                                                                                                           |

| C6             | NC                | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                       |

| C7             | VDD               | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                                               |

| C8             | GND               | Ground. 0 volt                                                                                                                                                                                                                           |

| D1             | BIAS              | Bias Circuit.                                                                                                                                                                                                                            |

| D2             | LPF               | <b>External Low-Pass Filter</b> (Analog). Connect external RC network for the low-pass filter.                                                                                                                                           |

| D3             | NC                | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                       |

| D4             | GND               | Ground. 0 volt                                                                                                                                                                                                                           |

| D5, D6         | VCC               | Positive Analog Power Supply. +3.3 V ±10%                                                                                                                                                                                                |

| D7, D8         | GND               | Ground. 0 volt                                                                                                                                                                                                                           |

| E1             | LOCK              | <b>Lock Indicator (CMOS Output).</b> This output goes high when the PLL is frequency locked to the selected input reference.                                                                                                             |

| E2, E3         | NC                | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                       |

| G4<br>E4<br>H5 | FS3<br>FS2<br>FS1 | Frequency Select 3-1 (CMOS Input). These inputs select the clock frequency on the OC-CLKo output. The possible output frequencies are: 19.44 MHz (000), 38.88 MHz (001), 77.76 MHz (010), 155.52 MHz (011), 622.08 (100)                 |

| E5             | VCC               | Positive Analog Power Supply. +3.3 V ±10%                                                                                                                                                                                                |

| E6             | VDD               | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                                               |

| E7             | NC                | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                       |

| E8<br>F8       | REFinN<br>REFinP  | Differential Reference Clock Input (CML/LVDS/LVPECL Compatible Input). These inputs accept a differential clock at 77.76 MHz or 19.44 MHz as the reference for synchronization. These inputs do not have on-chip AC coupling capacitors. |

| F1, F2         | NC                | No internal bonding Connection. Leave unconnected.                                                                                                                                                                                       |

| F3             | REF_FREQ          | Reference Frequency (CMOS Input). This input selects the rate of the differential input clock (REFinP/N) to be either 77.76 MHz or 19.44 MHz.                                                                                            |

| F4             | C19oEN            | C19o Output Enable (CMOS Input). If tied high this control input enables the C19o output clock. Pulling this pin low forces the output driver into a high impedance state.                                                               |

| F5             | C19i              | C19 Reference Input (CMOS Input). This is a single-ended input reference source used for synchronization. This input accepts 19.44 MHz.                                                                                                  |

#### **Ball Description Table (continued)**

| Ball #       | Name    | Description                                                                                                                                                                                                    |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F6           | C19o    | Clock 19.44 MHz (CMOS Output). This output provides a single-ended CMOS clock at 19.44 MHz.                                                                                                                    |

| F7, G1       | GND     | Ground. 0 volt                                                                                                                                                                                                 |

| G2           | VDD     | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                     |

| G3           | REF_SEL | Reference Select (CMOS Input). If tied low then the C19i single-ended reference is used as the input reference source. If tied high then the REFinP/N differential pair is used as the input reference source. |

| G4           | FS3     | See E4 ball description.                                                                                                                                                                                       |

| G5, G6       | GND     | Ground. 0 volt                                                                                                                                                                                                 |

| G7, G8       | VDD     | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                     |

| H1, H2<br>H3 | NC      | No internal bonding Connection. Leave unconnected.                                                                                                                                                             |

| H4           | VDD     | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                     |

| H5           | FS1     | See E4 ball description.                                                                                                                                                                                       |

| H6           | VDD     | Positive Digital Power Supply. +3.3 V ±10%                                                                                                                                                                     |

| H7, H8       | GND     | Ground. 0 volt.                                                                                                                                                                                                |

# 2.0 Functional Description

The ZL30416 is an analog phased-locked loop which provides rate conversion and jitter attenuation for SONET/SDH OC-192/STM-64, OC-48/STM-16, OC-12/STM-4 and OC-3/STM-1 applications. A functional block diagram of the ZL30416 is shown in Figure 1 and a brief description is presented in the following sections.

#### 2.1 Reference Selection Multiplexer

The ZL30416 accepts two types of input reference clocks:

- differential: operating at 19.44 MHz or 77.76 MHz, compatible with LVDS/LVPECL/CML threshold levels

- single-ended: operating at 19.44 MHz, compatible with CMOS switching levels

The REF\_SEL input determines whether the single-ended CMOS reference input (REFin) or the differential reference inputs (REFinP/N) are used as input reference clocks. The REF\_FREQ input selects the rate of the differential input clock to be either 19.44 MHz or 77.76 MHz. See Table 1 for details.

| REF_SEL | REF_FREQ | Selected Input Reference | Reference Frequency      |

|---------|----------|--------------------------|--------------------------|

| 0       | х        | C19i                     | 19.44 MHz (CMOS)         |

| 1       | 0        | REFin                    | 77.76 MHz (Differential) |

| 1       | 1        | REFin                    | 19.44 MHz (Differential) |

**Table 1 - Input Reference Selection**

#### 2.2 Frequency/Phase Detector

The Frequency/Phase Detector compares the frequency/phase of the input reference signal with the feedback signal from the Frequency Divider circuit and provides an error signal equal to the frequency/phase difference between the two. This error signal is passed to the Loop Filter circuit.

#### 2.3 Lock Indicator

The ZL30416 has a built-in LOCK detector that measures frequency difference between input reference clock C19i and the VCO frequency. When the VCO frequency is less than  $\pm 300$  ppm apart from the input reference frequency then the LOCK output is set high. The LOCK output is pulled low if the frequency difference exceeds  $\pm 1000$  ppm.

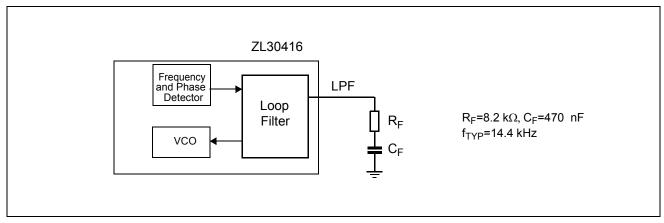

#### 2.4 Loop Filter

The Loop Filter is a low-pass filter. This low-pass filter eliminates high frequency spectral components from a phase error signal produced by the Phase Detector. This ensures low output jitter that meets network jitter requirements. The corner frequency of the Loop Filter is configurable with an external capacitor and resistor connected to the LPF ball and ground as shown in Figure 3.

Figure 3 - Loop Filter Elements

#### 2.5 VCO

The voltage-controlled oscillator (VCO) receives the filtered error signal from the Loop Filter and based on the voltage of the error signal generates a primary frequency. The VCO output is connected to the "Frequency Dividers and Clock Drivers" block that divides VCO frequency and buffer generated clocks.

# 2.6 Frequency Dividers and Clock Drivers

The output of the VCO feeds the high frequency clock to the "Frequency Dividers and Clock Drivers" circuit to provide one differential LVPECL compatible clock with selectable frequency and one single-ended 19.44 MHz C190 output clock. The C190 clock can be enabled or disabled with the associated C190EN Output Enable ball. Internally, this block provides a feedback clock that closes the PLL loop.

The frequency of the OC-CLKo differential output clock is selected with FS3, FS2 and FS1 inputs as is shown in the following table.

| FS3 | FS2 | FS1 | OC-CLKo<br>Frequency |

|-----|-----|-----|----------------------|

| 0   | 0   | 0   | 19.44 MHz            |

| 0   | 0   | 1   | 38.88 MHz            |

| 0   | 1   | 0   | 77.76 MHz            |

| 0   | 1   | 1   | 155.52 MHz           |

| 1   | 0   | 0   | 622.08 MHz           |

| 1   | 0   | 1   | Reserved             |

| 1   | 1   | 0   | Reserved             |

| 1   | 1   | 1   | Reserved             |

Table 2 - OC-CLKo Clock Frequency Selection

#### 3.0 ZL30416 Performance

The following are some of the ZL30416 performance indicators that complement results listed in the Characteristics section of this data sheet.

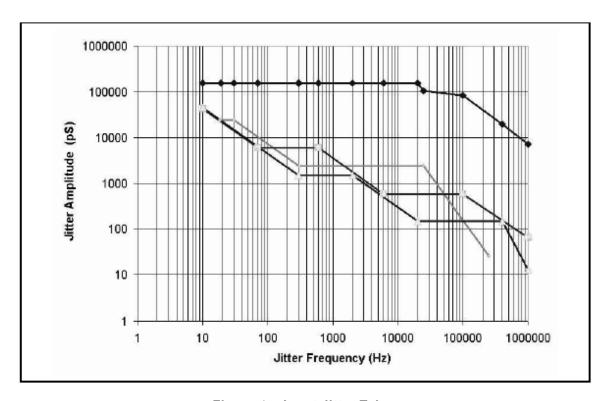

#### 3.1 Input Jitter Tolerance

Jitter tolerance is a measure of the PLL's ability to operate properly (i.e., remain in lock and/or regain lock in the presence of large jitter magnitudes at various jitter frequencies) in the presence of jitter applied to its input reference. The input jitter tolerance of the ZL30416 is shown in Figure 4. On this graph, the single line at the top represents the input jitter tolerance and the three overlapping lines below represent the specification for minimum input jitter tolerance for OC-192, OC-48 and OC-12 network interfaces. The jitter tolerance is expressed in picoseconds (pk-pk) to accommodate requirements for interfaces operating at different rates.

Figure 4 - Input Jitter Tolerance

#### 3.2 Jitter Transfer Characteristic

Jitter Transfer Characteristic represents a ratio of the jitter at the output of a PLL to the jitter applied to the input of a PLL. This ratio is expressed in dB and it characterizes the PLL's ability to attenuate (filter) jitter. The ZL30416 jitter transfer characteristic complies with the maximum 0.1 dB jitter gain specified in Telcordia's GR-253-CORE.

# 4.0 Applications

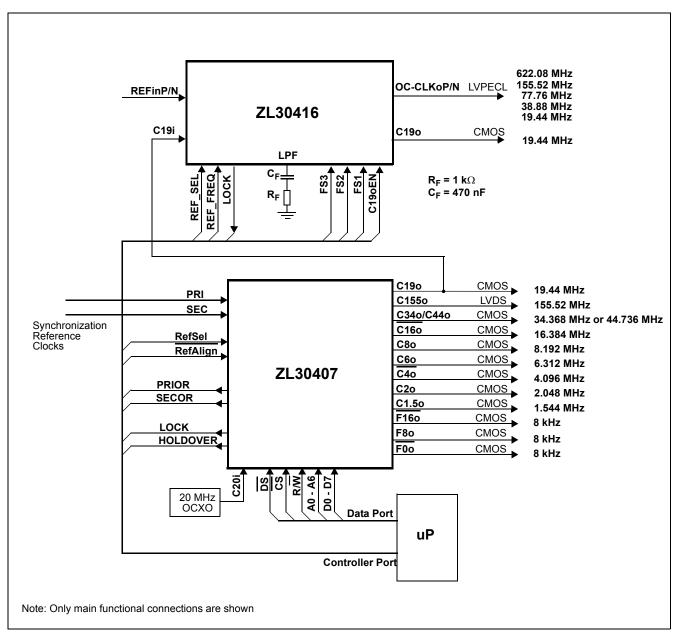

### 4.1 Generation of Low Jitter SONET/SDH Equipment Clocks

The functionality and performance of the ZL30416 complements the entire family of the Zarlink's advanced network synchronization PLL's. Its jitter filtering characteristics exceed requirements of SONET/SDH optical interfaces operating up to OC-192/STM-64. The ZL30416 in combination with the MT90401 or the ZL30407 (SONET/SDH Network Element PLL's) provides the core building blocks for high quality equipment clocks suitable for network synchronization (see Figure 5).

Figure 5 - SONET/SDH Equipment Clock

#### 4.2 Recommended Interface Circuit

#### 4.2.1 Interfacing to REFin Receiver

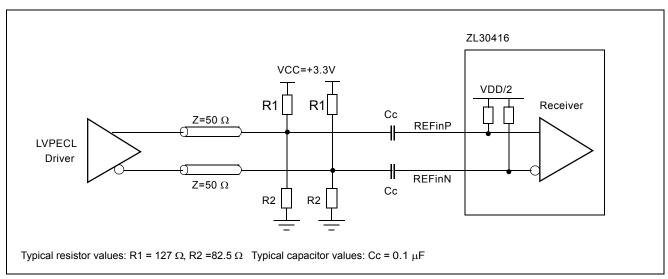

#### 4.2.1.1 Interfacing REFin Receiver to LVPECL Driver

The ZL30416 REFin differential receiver can be connected to LVPECL compatible driver with an interface circuit, as shown in Figure 7. The R1s and R2s terminating resistors should be placed close to the REFin input balls.

Figure 6 - Interfacing to LVPECL Driver

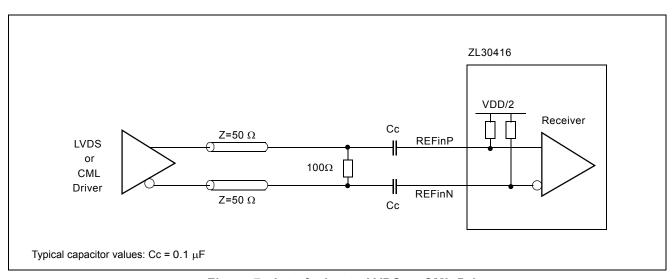

#### 4.2.1.2 Interfacing REFin Receiver to LVDS or CML Drivers

The ZL30416 REFin differential receiver can be connected to LVDS or CML driver with an interface circuit, as shown in Figure 7. The 100  $\Omega$  terminating resistors should be placed close to the REFin input balls.

Figure 7 - Interfacing to LVDS or CML Driver

#### 4.2.2 Interfacing to OC-CLKo Output

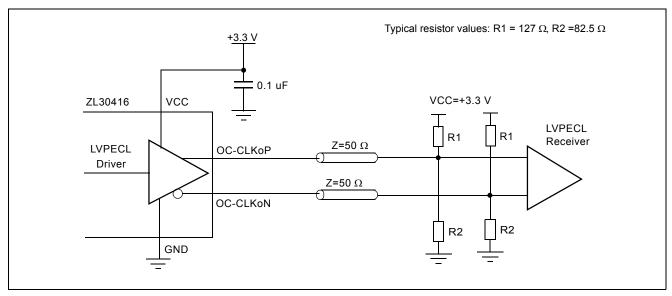

#### 4.2.2.1 LVPECL to LVPECL Interface

The OC-CLKo outputs provide differential LVPECL clocks at 622.08 MHz, 155.52 MHz, 77.76 MHz, 38.88 MHz and 19.44 MHz selectable with FS3, FS2 and FS1 frequency select inputs. The LVPECL output drivers require a 50  $\Omega$  termination connected to the Vcc-2V source for each output terminal at the terminating end as shown below. The terminating resistors should be placed close to the LVPECL receiver.

Figure 8 - LVPECL to LVPECL Interface

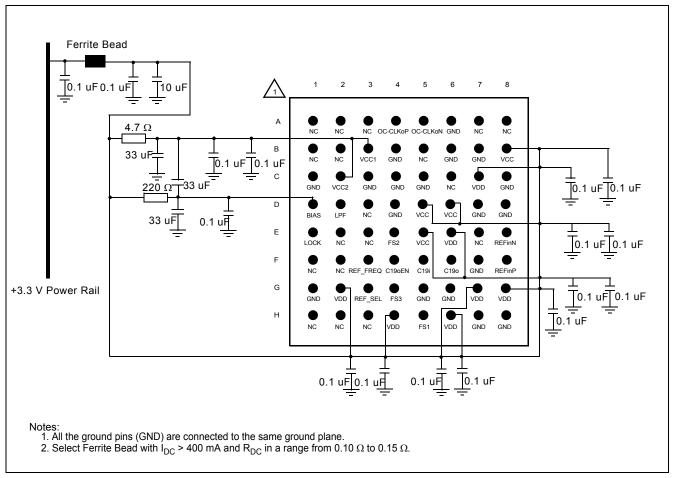

# 4.3 Power supply and BIAS Circuit Filtering Recommendations

Figure 9 presents a complete filtering arrangement that is recommended for applications requiring maximum jitter performance. The level of required filtering is subject to further optimization and simplification. Please check Zarlink's web site for updates.

Figure 9 - Power Supply and BIAS Circuit Filtering

# 5.0 Characteristics

# **Absolute Maximum Ratings**<sup>†</sup>

|   | Characteristics           | Sym.                                | Min. <sup>‡</sup> | Max. <sup>‡</sup>                              | Units |

|---|---------------------------|-------------------------------------|-------------------|------------------------------------------------|-------|

| 1 | Supply voltage            | V <sub>DDR</sub> , V <sub>CCR</sub> | TBD               | TBD                                            | V     |

| 2 | Voltage on any ball       | $V_{BALL}$                          | -0.5              | V <sub>CC</sub> + 0.5<br>V <sub>DD</sub> + 0.5 | V     |

| 3 | Current on any ball       | I <sub>BALL</sub>                   | -0.5              | 30                                             | mA    |

| 4 | ESD rating                | V <sub>ESD</sub>                    |                   | 1250                                           | V     |

| 5 | Storage temperature       | T <sub>ST</sub>                     | -55               | 125                                            | °C    |

| 6 | Package power dissipation | P <sub>PD</sub>                     |                   | 1.0                                            | W     |

<sup>†</sup> Voltages are with respect to ground unless otherwise stated.

# Recommended Operating Conditions<sup>†</sup>

|   | Characteristics       | Sym.                              | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|-----------------------|-----------------------------------|------|-------------------|------|-------|-------|

| 1 | Operating temperature | T <sub>OP</sub>                   | -40  | 25                | +85  | °C    |       |

| 2 | Positive supply       | V <sub>DD</sub> , V <sub>CC</sub> | 3.0  | 3.3               | 3.6  | V     |       |

<sup>†</sup> Voltages are with respect to ground unless otherwise stated.

#### DC Electrical Characteristics<sup>†</sup>

|   | Characteristics                                                   | Sym.                             | Min.                | Typ. <sup>‡</sup> | Max.                | Units | Notes                                      |

|---|-------------------------------------------------------------------|----------------------------------|---------------------|-------------------|---------------------|-------|--------------------------------------------|

| 1 | Supply current                                                    | I <sub>DD</sub> +I <sub>CC</sub> |                     | 185               |                     | mA    | Note 1<br>Note 2                           |

| 2 | CMOS: High-level input voltage                                    | V <sub>IH</sub>                  | 0.7 V <sub>DD</sub> |                   | V <sub>DD</sub>     | V     |                                            |

| 3 | CMOS: Low-level input voltage                                     | $V_{IL}$                         | 0                   |                   | 0.3 V <sub>DD</sub> | V     |                                            |

| 4 | CMOS: Input leakage current                                       | I <sub>IL</sub>                  |                     | 1                 | 5                   | uA    | V <sub>I</sub> = V <sub>DD</sub><br>or 0 V |

| 5 | CMOS: Input bias current for pulled-down inputs: FS1, FS2 and FS3 | I <sub>B-PU</sub>                |                     | 300               |                     | uA    | V <sub>I</sub> = V <sub>DD</sub>           |

| 6 | CMOS: Input bias current for pulled-up inputs: C19oEN             | I <sub>B-PD</sub>                |                     | 90                |                     | uA    | V <sub>I</sub> = 0 V                       |

| 7 | CMOS: High-level output voltage                                   | V <sub>OH</sub>                  | 2.4                 |                   |                     | V     | I <sub>OH</sub> = 8 mA                     |

<sup>‡</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

# DC Electrical Characteristics<sup>†</sup> (continued)

|    | Characteristics                     | Sym.                         | Min.         | Typ. <sup>‡</sup> | Max.         | Units | Notes                  |

|----|-------------------------------------|------------------------------|--------------|-------------------|--------------|-------|------------------------|

| 8  | CMOS: Low-level output voltage      | V <sub>OL</sub>              |              |                   | 0.4          | V     | I <sub>OL</sub> = 4 mA |

| 9  | CMOS: C19o output rise time         | T <sub>R</sub>               |              | 1.8               | 3.3          | ns    | 18 pF load             |

| 10 | CMOS: C19o output fall time         | T <sub>F</sub>               |              | 1.1               | 1.4          | ns    | 18 pF load             |

| 11 | LVPECL: Differential output voltage | IV <sub>OD_LVPEC</sub><br>LI |              | 1.30              |              | V     | for 622 MHz<br>Note 2  |

| 12 | LVPECL: Offset voltage              | V <sub>OS_LVPECL</sub>       | Vcc-<br>1.38 | Vcc-<br>1.27      | Vcc-<br>1.15 | V     | for 622 MHz<br>Note 2  |

| 13 | LVPECL: Output rise/fall times      | T <sub>RF</sub>              |              | 260               |              | ps    | for 622 MHz<br>Note 2  |

<sup>†</sup> Voltages are with respect to ground unless otherwise stated.

Note 2: LVPECL outputs terminated with  $Z_T$  = 50  $\Omega$  resistors biased to  $V_{CC}$ -2V (see Figure 8).

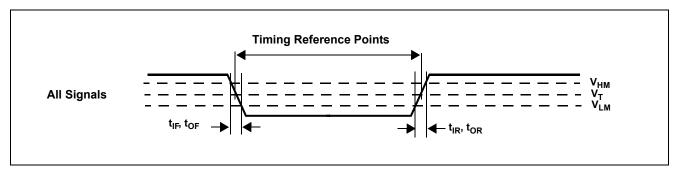

# AC Electrical Characteristics<sup>†</sup> - Output Timing Parameters Measurement Voltage Levels

|   | Characteristics                      | Sym.                                         | смоѕ                | LVPECL                     | Units |

|---|--------------------------------------|----------------------------------------------|---------------------|----------------------------|-------|

| 1 | Threshold voltage                    | V <sub>T-CMOS</sub><br>V <sub>T-LVPECL</sub> | 0.5 V <sub>DD</sub> | 0.5 V <sub>OD_LVPECL</sub> | V     |

| 2 | Rise and fall threshold voltage high | V <sub>HM</sub>                              | 0.7 V <sub>DD</sub> | 0.8 V <sub>OD_LVPECL</sub> | V     |

| 3 | Rise and fall threshold voltage low  | V <sub>LM</sub>                              | 0.3 V <sub>DD</sub> | 0.2 V <sub>OD_LVPECL</sub> | V     |

<sup>†</sup> Voltages are with respect to ground unless otherwise stated.

Figure 10 - Output Timing Parameter Measurement Voltage Levels

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

Supply voltage and operating temperature are as per Recommended Operating Conditions.

Note 1: The I<sub>LVPECL</sub> current is determined by the external termination network connected to LVPECL outputs. More than 25% of this current (10 mA) flows outside the chip and it does not contribute to the internal power dissipation. The Supply Current value listed in the table includes this current to reflect total current consumption of the ZL30416 and the attached LVPECL termination network.

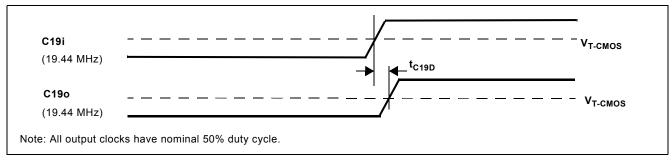

# AC Electrical Characteristics<sup>†</sup> - C19i Input to C19o Output Timing

|   | Characteristics    | Sym.              | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|--------------------|-------------------|------|-------------------|------|-------|-------|

| 1 | C19i to C19o delay | t <sub>C19D</sub> | 4.4  | 6.7               | 9.4  | ns    |       |

<sup>†</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions.

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

Figure 11 - C19i Input to C19o Output Timing

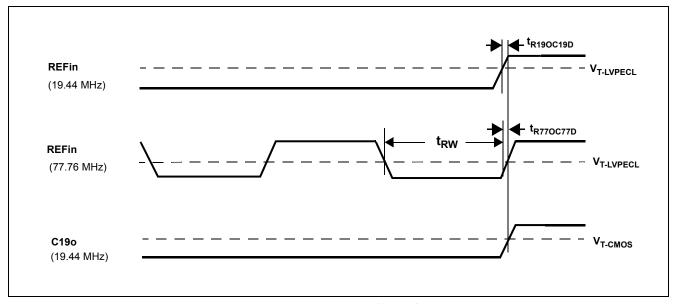

# AC Electrical Characteristics<sup>†</sup> - REFin to C19o Output Timings

|   | Characteristics                             | Sym.                  | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|---------------------------------------------|-----------------------|------|-------------------|------|-------|-------|

| 1 | REFin (19.44 MHz) to C19o (19.44 MHz) delay | t <sub>R190C19D</sub> | 1.4  | 7.8               | 10   | ns    |       |

| 2 | REFin (77.76 MHz) to C19o (19.44 MHz) delay | t <sub>R77OC77D</sub> | 7.9  | 9.9               | 13   | ns    |       |

Figure 12 - REFin Input to C19o Output Timing

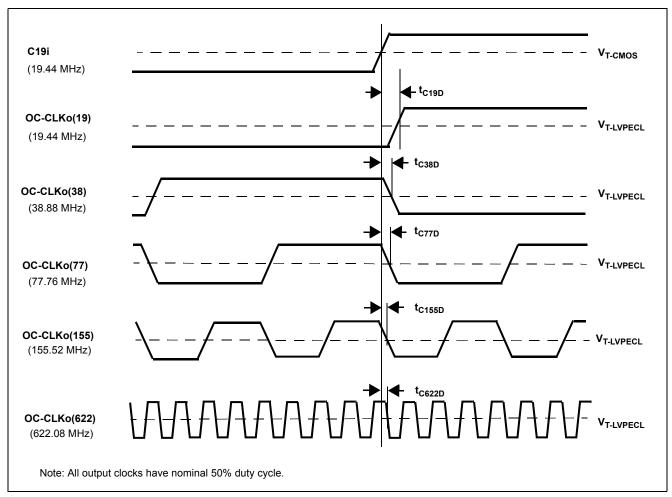

# AC Electrical Characteristics<sup>†</sup> - C19i Input to OC-CLKo Output Timing

|   | Characteristics                  | Sym.               | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|----------------------------------|--------------------|------|-------------------|------|-------|-------|

| 1 | C19i(CMOS) to C19o(LVPECL) delay | t <sub>C19D</sub>  | 1.4  | 3.3               | 5.1  | ns    |       |

| 2 | C19i(CMOS) to OC-CLKo(38) delay  | t <sub>C38D</sub>  | 1.2  | 3.0               | 4.8  | ns    |       |

| 3 | C19i(CMOS) to OC-CLKo(77) delay  | t <sub>C77D</sub>  | 0.9  | 2.6               | 4.4  | ns    |       |

| 4 | C19i(CMOS) to OC-CLKo(155) delay | t <sub>C155D</sub> | 0.6  | 2.3               | 4.1  | ns    |       |

| 5 | C19i(CMOS) to OC-CLKo(622) delay | t <sub>C622D</sub> | 0    | 0.8               | 1.6  | ns    |       |

| 6 | All Output Clock duty cycle      | d <sub>C</sub>     | 48   | 50                | 52   | %     |       |

<sup>†</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions.

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

Figure 13 - C19i Input to OC-CLKo Output Timing

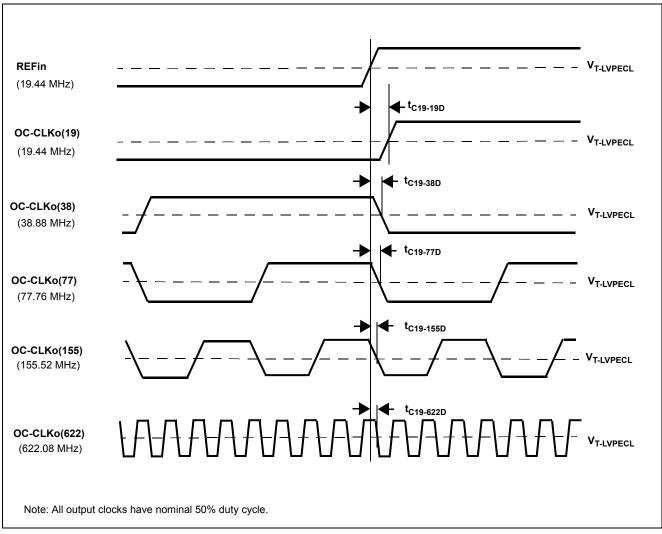

# AC Electrical Characteristics<sup>†</sup> - REFin (19.44 MHz) Input to OC-CLKo Output Timing

|   | Characteristics                        | Sym.                  | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|----------------------------------------|-----------------------|------|-------------------|------|-------|-------|

| 1 | REFin(19.44 MHz) to OC-CLKo(19) delay  | t <sub>C19-19D</sub>  | 2.4  | 4.3               | 6.2  | ns    |       |

| 2 | REFin(19.44 MHz) to OC-CLKo(38) delay  | t <sub>C19-38D</sub>  | 1.9  | 4.0               | 6.0  | ns    |       |

| 3 | REFin(19.44 MHz) to OC-CLKo(77) delay  | t <sub>C19-77D</sub>  | 1.7  | 3.7               | 5.6  | ns    |       |

| 4 | REFin(19.44 MHz) to OC-CLKo(155) delay | t <sub>C19-155D</sub> | 1.4  | 3.4               | 5.3  | ns    |       |

| 5 | REFin(19.44 MHz) to OC-CLKo(622) delay | t <sub>C19-622D</sub> | 0    | 0.8               | 1.6  | ns    |       |

<sup>†</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions.

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

Figure 14 - REFin (19.44 MHz) Input to OC-CLKo Output Timing

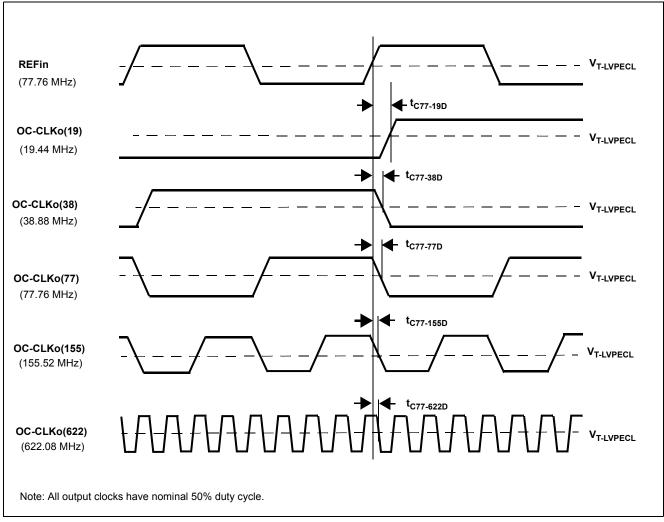

# AC Electrical Characteristics<sup>†</sup> - REFin (77.76 MHz) Input to OC-CLKo Output Timing

|   | Characteristics                        | Sym.                  | Min. | Typ. <sup>‡</sup> | Max. | Units | Notes |

|---|----------------------------------------|-----------------------|------|-------------------|------|-------|-------|

| 1 | REFin(77.76 MHz) to OC-CLKo(19) delay  | t <sub>C77-19D</sub>  | 3.5  | 6.5               | 9.5  | ns    |       |

| 2 | REFin(77.76 MHz) to OC-CLKo(38) delay  | t <sub>C77-38D</sub>  | 3.2  | 6.2               | 9.2  | ns    |       |

| 3 | REFin(77.76 MHz) to OC-CLKo(77) delay  | t <sub>C77-77D</sub>  | 2.9  | 5.9               | 8.8  | ns    |       |

| 4 | REFin(77.76 MHz) to OC-CLKo(155) delay | t <sub>C77-155D</sub> | 2.6  | 5.6               | 8.6  | ns    |       |

| 5 | REFin(77.76 MHz) to OC-CLKo(622) delay | t <sub>C77-622D</sub> | 0    | 0.8               | 1.6  | ns    |       |

<sup>†</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions.

<sup>‡</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

Figure 15 - REFin (77.76 MHz) Input to OC-CLKo Output Timing

# Performance Characteristics - Functional - ( $V_{CC}$ = 3.3 V ±10%; $T_A$ = -40 to 85°C)

|   | Characteristics | Min.  | Тур. | Max. | Units | Notes                                                       |

|---|-----------------|-------|------|------|-------|-------------------------------------------------------------|

| 1 | Pull-in range   | ±1000 |      |      | ppm   | At nominal input<br>reference frequency<br>C19i = 19.44 MHz |

| 2 | Lock Time       |       |      | 300  | ms    |                                                             |

# Performance Characteristics: Output Jitter Generation - GR-253-CORE conformance ( $V_{CC}$ = 3.3 V $\pm$ 10%; $T_A$ = -40 to 85°C)

|   | GR-253-                    | CORE Jitter Generat             | ZL30416 Jitter Generation Performance |                                       |                   |                   |                   |

|---|----------------------------|---------------------------------|---------------------------------------|---------------------------------------|-------------------|-------------------|-------------------|

|   | Interface<br>(Category II) | Jitter<br>Measurement<br>Filter | Limit in<br>UI                        | Equivalent<br>limit in time<br>domain | Typ. <sup>†</sup> | Max. <sup>‡</sup> | Units             |

| 1 | OC-192                     | 4 MHz to 80 MHz                 | 0.1 Ulpp                              | 10.0                                  | -                 | 6.95              | ps <sub>P-P</sub> |

|   | STS-192                    |                                 |                                       |                                       | 0.49              | 0.89              | ps <sub>RMS</sub> |

|   |                            | 20 kHz to 80 MHz                | 0.3 Ulpp                              | 30.1                                  | -                 | 11.5              | ps <sub>P-P</sub> |

|   |                            |                                 |                                       |                                       | 0.82              | 1.04              | ps <sub>RMS</sub> |

| 2 | OC-48                      |                                 | 0.1 UI <sub>PP</sub>                  | 40.2                                  | -                 | 7.32              | ps <sub>P-P</sub> |

|   | STS-48                     |                                 | 0.01 UI <sub>RMS</sub>                | 4.02                                  | 0.58              | 0.83              | ps <sub>RMS</sub> |

| 3 | OC-12                      |                                 | 0.1 UI <sub>PP</sub>                  | 161                                   | -                 | 4.37              | ps <sub>P-P</sub> |

|   | STS-12                     |                                 | 0.01 UI <sub>RMS</sub>                | 16.1                                  | 0.34              | 0.60              | ps <sub>RMS</sub> |

<sup>†</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

$<sup>\</sup>ddagger$  Loop Filter components: R<sub>F</sub>=8.2 kΩ, C<sub>F</sub>=470 nF.

Performance Characteristics: Output Jitter Generation - G.813 conformance (Option 1 and 2) ( $V_{CC}$  = 3.3 V  $\pm 10\%$ ;  $T_A$  = -40 to 85°C)

|   | G.81      | 13 Jitter Generation            | s              | ZL304                                 | 16 Jitter Gen<br>Performance |       |                   |

|---|-----------|---------------------------------|----------------|---------------------------------------|------------------------------|-------|-------------------|

|   | Interface | Jitter<br>Measurement<br>Filter | Limit in<br>UI | Equivalent<br>limit in time<br>domain | Typ.†                        | Max.‡ | Units             |

|   |           | Option 1                        |                |                                       |                              |       |                   |

| 1 | STM-64    | 4 MHz to 80 MHz                 | 0.1 Ulpp       | 10.0                                  | -                            | 6.95  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.49                         | 0.89  | ps <sub>RMS</sub> |

|   |           | 20 kHz to 80 MHz                | 0.5 Ulpp       | 50.2                                  | -                            | 11.5  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.82                         | 1.04  | ps <sub>RMS</sub> |

| 2 | STM-16    | 1 MHz to 20 MHz                 | 0.1 Ulpp       | 40.2                                  | -                            | 6.40  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.50                         | 0.68  | ps <sub>RMS</sub> |

|   |           | 5 kHz to 20 MHz                 | 0.5 Ulpp       | 201                                   | -                            | 8.67  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.68                         | 1.06  | ps <sub>RMS</sub> |

| 3 | STM-4     | 250 kHz to 5 MHz                | 0.1 Ulpp       | 161                                   | -                            | 3.33  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.26                         | 0.42  | ps <sub>RMS</sub> |

|   |           | 1 kHz to 5 MHz                  | 0.5 Ulpp       | 804                                   | -                            | 19.1  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 1.51                         | 2.88  | ps <sub>RMS</sub> |

|   |           | Option 2                        |                |                                       |                              |       | <u> </u>          |

| 5 | STM-64    | 4 MHz to 80 MHz                 | 0.1 Ulpp       | 10.0                                  | -                            | 6.95  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.49                         | 0.89  | ps <sub>RMS</sub> |

|   |           | 20 kHz to 80 MHz                | 0.3 Ulpp       | 30.1                                  | -                            | 11.5  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.82                         | 1.04  | ps <sub>RMS</sub> |

| 6 | STM-16    | 12 kHz - 20 MHz                 | 0.1 Ulpp       | 40.2                                  | -                            | 7.32  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.58                         | 0.83  | ps <sub>RMS</sub> |

| 7 | STM-4     | 12 kHz - 5 MHz                  | 0.1 Ulpp       | 161                                   | -                            | 4.37  | ps <sub>P-P</sub> |

|   |           |                                 |                |                                       | 0.34                         | 0.60  | ps <sub>RMS</sub> |

<sup>†</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

$<sup>\</sup>ddagger$  Loop Filter components: RF=8.2 kΩ, CF=470 nF.

Performance Characteristics: Output Jitter Generation - ETSI EN 300 462-7-1conformance ( $V_{CC}$  = 3.3 V  $\pm$ 10%;  $T_A$  = -40 to 85°C)

|        | EN 300 4  | 62-7-1 Jitter Genera            | ZL30416 Jitter Generation<br>Performance |                                       |                   |       |                                                                                |

|--------|-----------|---------------------------------|------------------------------------------|---------------------------------------|-------------------|-------|--------------------------------------------------------------------------------|

|        | Interface | Jitter<br>Measurement<br>Filter | Limit in<br>UI                           | Equivalent<br>limit in time<br>domain | Typ. <sup>†</sup> | Max.‡ | Units                                                                          |

| 1 STM- | STM-16    | 1 MHz to 20 MHz                 | 0.1 Ulpp                                 | 40.2                                  | -                 | 6.40  | ps <sub>P-P</sub>                                                              |

|        |           |                                 |                                          |                                       | 0.50              | 0.68  | ps <sub>RMS</sub>                                                              |

|        |           | 5 kHz to 20 MHz                 | 0.5Ulpp                                  | 201                                   | -                 | 8.67  | ps <sub>P-P</sub>                                                              |

|        |           |                                 |                                          |                                       | 0.68              | 1.06  | ps <sub>RMS</sub>                                                              |

| 2      | STM-4     | 250 kHz to 5 MHz                | 0.1 Ulpp                                 | 161                                   | -                 | 3.33  | ps <sub>P-P</sub>                                                              |

|        |           |                                 |                                          |                                       | 0.26              | 0.42  | Units  ps <sub>P-P</sub> ps <sub>RMS</sub> ps <sub>P-P</sub> ps <sub>RMS</sub> |

|        |           | 1 kHz to 5 MHz                  | 0.5 Ulpp                                 | 804                                   | -                 | 19.1  | ps <sub>P-P</sub>                                                              |

|        |           |                                 |                                          |                                       | 1.51              | 2.88  | ps <sub>RMS</sub>                                                              |

<sup>†</sup> Typical figures are for design aid only: not guaranteed and not subject to production testing.

$<sup>\</sup>ddagger$  Loop Filter components: RF=8.2 kΩ, CF=470 nF

# For more information about all Zarlink products visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sub>2</sub>C components conveys a licence under the Philips I<sub>2</sub>C Patent rights to use these components in and I<sub>2</sub>C System, provided that the system conforms to the I<sub>2</sub>C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc.

TECHNICAL DOCUMENTATION - NOT FOR RESALE