#### **FEATURES**

- Designed for PCB space savings with 3 low-power Programmable PLLs and up to 8 clock outputs.

- Low-Power Consumption

- o 10µA typical when PDB is activated

- Output Frequency:

- <166MHz @ 2.5V operation

- < <200MHz @ 3.3V operation</p>

- Input Frequency:

- Fundamental Crystal: 10MHz to 40MHz

- Reference Input: 10MHz to 200MHz

- Programmable I/O pins can be configured as Output Enable (OE), Configuration Switching (CSEL), Frequency Switching (FSELX), Power Down (PDB) inputs, or Clock outputs.

- Disabled outputs programmable as HiZ or Active Low

- Four distinct configurations selectable with CSEL[0:1]

- Single 1.8V, 2.5V, or 3.3V ± 10% power supply

- Temperature range: 0°C to 70°C, -40°C to +85°C

- Available in GREEN/RoHS compliant 3x3 QFN or (T)SSOP packages.

#### DESCRIPTION

The PL613-01 is an advanced triple PLL design based on PicoPLL™, world's smallest programmable clock, technology. This advanced technology allows the 8 output PL613-01 to fit in to a small 3mmx3mm QFN package or (T)SSOP for high performance, low-power, low-cost applications. Besides its small form factor and 8 outputs that can reduce overall system costs, the PL613-01 offers superior phase noise, jitter and power consumption performance.

The power down feature of PL613-01, when activated, allows the IC to consume less than 10µA of power, while its CSEL[0:1] allows switching between up to 4 pre-programmed configurations. The FSELX, on the other hand, allows frequency switching of two outputs (CLK1 & CLK2) on a single clock pin (CLK2).

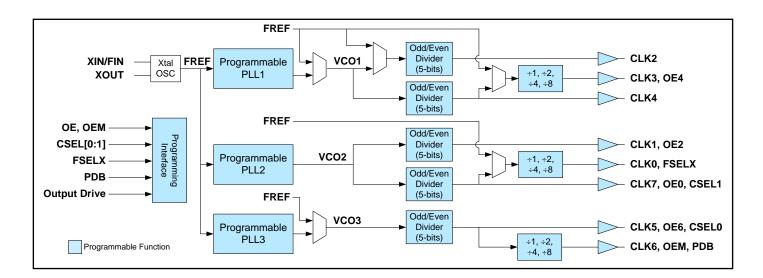

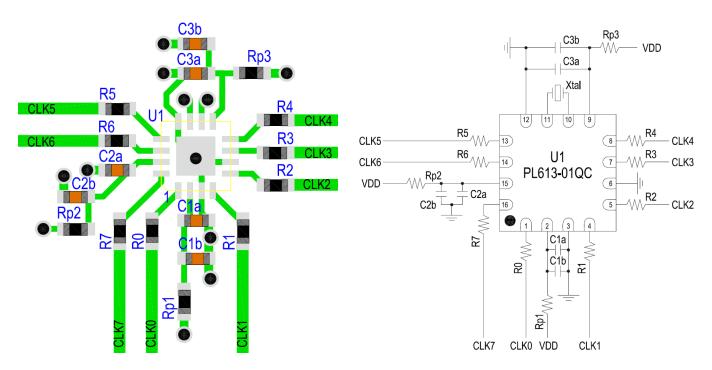

#### **BLOCK DIAGRAM**

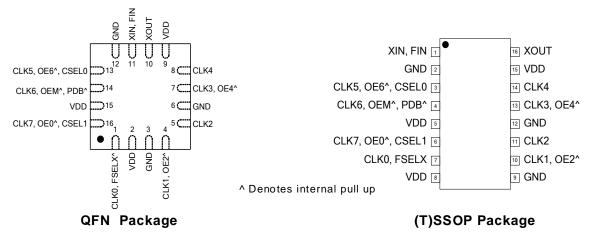

#### **PIN CONFIGURATION**

#### **PACKAGE PIN ASSIGNMENT**

| No                  | Package Pin # |             | <b>T</b> | D                                                                                                                                             |

|---------------------|---------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Name                | QFN-16L       | (T)SSOP-16L | Туре     | Description                                                                                                                                   |

| CLK0, FSELX         | 1             | 7           | В*       | <ul><li>Programmable Clock (CLK0) output or</li><li>CLK2 Frequency Switching (FSELX) input.</li></ul>                                         |

| GND                 | 3, 6, 12      | 2, 9, 12    | Р        | GND connection.                                                                                                                               |

| VDD                 | 2, 9, 15      | 5, 8, 15    | Р        | VDD connection.                                                                                                                               |

| CLK1, OE2           | 4             | 10          | B*       | - Programmable Clock (CLK1) output or - Output Enable (OE) input for CLK2.                                                                    |

| CLK2                | 5             | 11          | 0        | Programmable Clock (CLK2) output.                                                                                                             |

| CLK3, OE4           | 7             | 13          | B*       | - Programmable Clock (CLK3) output or - Output Enable (OE) input for CLK4.                                                                    |

| CLK4                | 8             | 14          | 0        | Programmable Clock (CLK4) output.                                                                                                             |

| XOUT                | 10            | 16          | 0        | Crystal output pin. Do Not Connect when using FIN.                                                                                            |

| XIN, FIN            | 11            | 1           | I        | Crystal or Reference Clock input.                                                                                                             |

| CLK5, OE6,<br>CSEL0 | 13            | 3           | B*       | <ul> <li>Programmable Clock (CLK5) output or</li> <li>Output Enable (OE) input for CLK6 or</li> <li>Configuration Switching input.</li> </ul> |

| CLK6, OEM,<br>PDB   | 14            | 4           | B*       | - Programmable Clock (CLK6) output, or - Output Enable Master (OEM) for all clock outputs, or - Power Down mode (PDB) input.                  |

| CLK7, OE0,<br>CSEL1 | 16            | 6           | B*       | <ul> <li>Programmable Clock (CLK7) output or</li> <li>Output Enable (OE) input for CLK0 or</li> <li>Configuration Switching input.</li> </ul> |

<sup>\*</sup> Note: All bidirectional buffers (I/Os) incorporate an internal  $60K\Omega$  pull up resistor when used as an input except when PDB mode is used. In configurations that use PDB, the PDB pin will have a  $10M\Omega$  pull up resistor.

#### **KEY PROGRAMMING PARAMETERS**

| CLK[ 0:7 ]<br>Output Frequency                                                                                                                                                                            | Output Drive Strength                                                    | Programmable Input/Output                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK[0,3,6] $F_{VCOx} / (P^*(1,2,4,8)), F_{REF} \text{ or } F_{REF} / (P^*(1,2,4,8))$                                                                                                                      | Each output has three optional drive strengths to choose from. They are: | Most pins are multi-function I/Os. In addition to CLK, they can be configured to perform as:                                                                                                                                                                                                                                   |

| $CLK[1,4,7]$ $F_{VCOx} / P$ $CLK[2,5]$ $F_{VCOx} / P, F_{REF} \text{ or } F_{REF} / P$ $Where F_{VCOx} = F_{REF} * M / R$ $M = 11 \text{ bit}$ $R = 8 \text{ bit}$ $P = 5 \text{ bit (Odd/Even Divider)}$ | <ul><li>Low: 4mA</li><li>Std: 8mA (default)</li><li>High:16mA</li></ul>  | <ul> <li>OE [0,2,4,6] – (Output Enable for individual I/Os)</li> <li>OEM – (Master OE controlling all outputs)</li> <li>CSEL[0:1] – (Device Configuration Switching)</li> <li>FSELX – (CLK2 Frequency Switching)</li> <li>PDB – (Power Down)</li> <li>CLK[0:8] – (Output)</li> <li>HiZ or Active Low disabled state</li> </ul> |

#### **FUNCTIONAL DESCRIPTION**

The PL613-01 is a highly featured, very flexible, advanced triple PLL design for high performance, low-power applications. The device accepts a low-cost fundamental crystal input of 10MHz to 40MHz or a reference clock input of 10MHz to 200MHz and is capable of producing 8 distinct output frequencies up to 200MHz. All 3-PLLs are fully programmable, with a total of five, 5-bit Post VCO, Odd/Even 'P-counter' dividers with additional 1, 2, 4 or 8 'Post P-counter' dividers to allow generating most demanding frequencies, easily. The outputs can be programmed to deliver the generated frequencies from the PLLs, or the reference input. Each bidirectional feature pin (I/O) on the PL613-01 incorporates a  $60 \text{K}\Omega$  pull up resistor and can be configured to perform various functions. Usage of various design features of these products is mentioned in the following paragraphs.

#### **PLL Programming**

The three PLLs in PL613-01 are fully programmable. Each PLL is equipped with an 8-bit input frequency divider (R-Counter) and an 11-bit VCO frequency feedback loop (M-Counter) divider. The three PLL outputs are transferred to five 5-bit post VCO, Odd/Even dividers (P-Counter), as shown in the above diagrams. In addition, there are three optional (÷1, ÷2, ÷4 or ÷8) post P-Counter dividers, that can further divide the VCO frequency. In general, the PLL output frequency is determined by the following formula:

$$F_{OUT} = (F_{REF} * M)/(R*P)$$

For output calculations, please note that 'P' includes the 'P' counter bits plus the additional optional  $(\div 1, \div 2, \div 4 \text{ or } \div 8)$  dividers, if used.

#### **CLKx (Clock Outputs)**

There are a maximum of 8 outputs available on the PL613-01. Clock output frequencies can be configured as follows:

CLK[0,3,6]

$$F_{VCOx} / (P^*(1, 2, 4, 8))$$

$$F_{REF} (Crystal \text{ or Reference Clock frequency})$$

$$F_{REF} / (P^*(1,2,4,8))$$

CLK[1, 7]

$$F_{VCOx} / P$$

CLK[2, 4, 5]

$$F_{VCOx} / P, F_{REF} \text{ or } F_{REF} / P$$

Each output can be programmed with a 4mA, 8mA, or 16mA drive strength. The maximum output frequency is 200MHz @ 3.3V, 166MHz @ 2.5V or 110MHz @ 1.8V.

#### **OE** (Output Enable)

Four pins can be configured as OE inputs for controlling individual clock outputs, as shown in the table below:

| OEx | Controls Output<br>On CLK# |

|-----|----------------------------|

| OE0 | CLK0                       |

| OE2 | CLK2                       |

| OE4 | CLK4                       |

| OE6 | CLK6                       |

Note: Typical enable time is <500ns plus one clock period.

The OE feature can be programmed to allow the output to float (Hi Z), or to operate in the 'Active low' mode. The programming control for individual OEs is shown below:

| OE<br>Pin | OE Type<br>(Programmable) | Osc     | PLL    | Output     |

|-----------|---------------------------|---------|--------|------------|

| 0         | 0 (Default)               | On      | On     | Hi Z       |

| 0         | 1                         | 1 On    | On     | Active '0' |

| 1         | Normal Op                 | eration | (Defau | ult)       |

#### **OEM (Master Output Enable)**

One pin can be configured to be a single Master OE (OEM) input pin that controls all the outputs of the PL613-01. In addition the state of the disabled outputs can be programmed to float (Hi Z) or to operate in the 'Active low' mode. The OEM Function operates on the following logic:

| OEM<br>Pin | OE Type<br>(Programmable) | Osc     | PLL    | Output     |

|------------|---------------------------|---------|--------|------------|

| 0          | 0 (Default)               | On      | On     | Hi Z       |

| U          | 1                         | On      | On     | Active '0' |

| 1          | Normal Op                 | eration | (Defau | ult)       |

Note: Typical enable time is <500ns plus one clock period.

#### **Power-Down Control (PDB)**

When activated, PDB 'Disables all the PLLs, the oscillator circuitry, counters, and all other active circuitry. PDB activation disables all outputs and the IC consumes <10 $\mu$ A of power. The PDB input incorporates a 10M $\Omega$  pull up resistor for normal operating condition.

The PDB feature can be programmed to allow the output to float (Hi Z), or to operate in the 'Active low' mode. The logic for PDB is shown below:

| PDB<br>Pin | PDB Type<br>Program        | Osc | PLL | Output     |  |

|------------|----------------------------|-----|-----|------------|--|

| 0          | 0 (Default)                | Off | Off | Hi Z       |  |

| 0          | 1                          | Off | Off | Active '0' |  |

| 1          | Normal Operation (Default) |     |     |            |  |

Note: Typical enable time from power down is <2ms.

#### **On-The-Fly Configuration Switching (CSEL)**

The PL613-01 can be programmed to allow switching between 4 different configurations, allowing for changes in the output frequencies. Many applications (i.e. video/audio) can use the same design footprint, but allow for configuration switching, adhering to various standards. CSEL0 and CSEL1 are used in the switching selection. These pins incorporate a  $60k\Omega$  pull up resistor for normal operating condition. The logic for configuration switching of the programmed parts is shown below:

| CSEL1 | CSEL0 | Programmed Configuration |

|-------|-------|--------------------------|

| 0     | 0     | 0                        |

| 0     | 1     | 1                        |

| 1     | 0     | 2                        |

| 1     | 1     | 3 (Default)              |

Note: Typical enable time is <500 µs.

## On-The-Fly Output Frequency Switching Between Two Output Frequencies (FSELX)

The PL613-01 is equipped with the FSELX feature to allow frequency switching of two frequencies on one of the output pins. Frequencies assigned to CLK1 and CLK2 can be switched, when FSELX is activated, on CLK2 output. The logic for FSELX is shown below:

| FSELX       | CLK2 Output |

|-------------|-------------|

| 0           | Frequency 2 |

| 1 (default) | Frequency 1 |

Note: Typical enable time is <10ns plus one clock period.

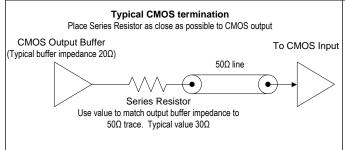

#### LAYOUT RECOMMENDATIONS

The following guidelines are to assist you with a performance optimized PCB design:

#### Signal Integrity and Termination Considerations

- Keep traces short!

- Trace = Inductor. With a capacitive load this equals ringing!

- Long trace = Transmission Line. Without proper termination this will cause reflections (looks like ringing).

- Design long traces (>1 inch) as "striplines" or "microstrips" with defined impedance.

- Match trace at one side to avoid reflections bouncing back and forth.

#### **Decoupling and Power Supply Considerations**

- Place decoupling capacitors as close as possible to the  $V_{\text{DD}}$  pin(s) to limit noise from the power supply

- Multiple  $V_{\text{DD}}$  pins should be decoupled separately for best performance.

- Addition of resistors in series with  $V_{\text{DD}}$  can help prevent noise from other board sources. Traditionally ferrite beads are also used for this purpose but with the PL613-01 the results are better when using resistors.

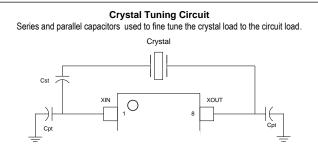

CST – Series Capacitor, used to lower circuit load to match crystal load. Raises frequency offset. This can be eliminated by using a crystal with a Cload of equal or greater value than the oscillator CPT – Parallel Capacitors, Used to raise the circuit load to match the crystal load. Lowers frequency offset.

#### LAYOUT EXAMPLE

U1 = PL613-01 in QFN-16L. In this example all 8 outputs are used.

C1a, C2a, C3a =  $0.1\mu\text{F}$  and C1b, C2b, C3b =  $1\mu\text{F}$  for Power Supply decoupling. The vias connected to the capacitors go to the ground plane inside the PCB.

R1p, R2p, R3p =  $10\Omega$  for Power Supply filtering. The power supply filter is a 1st order low pass filter with -3dB at 30KHz. It is important that the frequencies of the loop bandwidth of the PLLs are filtered properly. The loop bandwidth of the PLLs is in the range 100KHz to 1MHz, depending upon the programmed configuration. The vias connected to Rp1, Rp2 and Rp3 go to the VDD plane inside the PCB.

$R0 \sim R7 = 30\Omega$  for matching CLK0  $\sim$  CLK7 outputs to the PCB trace impedance. Place the resistors as close as possible to the IC pins and design the traces to the target clock inputs as transmission lines (microstrip or stripline) for the best signal integrity and the lowest EMI.

When using ferrite beads instead of Rp1, Rp2 or Rp2, make sure the resonance frequency of the bead with the decoupling capacitors is below 50KHz, to not interfere with the PLL loop bandwidth. This requirement is difficult to fulfill so we recommend using the resistors Rp1, Rp2 and Rp3 for power supply filtering.

## ELECTRICAL SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                            | SYMBOL   | MIN. | MAX.                 | UNITS |

|---------------------------------------|----------|------|----------------------|-------|

| Supply Voltage Range                  | $V_{DD}$ | -0.5 | 4.6                  | V     |

| Input Voltage Range                   | Vı       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage Range                  | Vo       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Soldering Temperature (Green package) |          |      | 260                  | °C    |

| Data Retention @ 85°C                 |          | 10   |                      | Year  |

| Storage Temperature                   | Ts       | -65  | 150                  | °C    |

| Ambient Operating Temperature*        |          | -40  | 85                   | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

#### **AC SPECIFICATIONS**

| PARAMETERS                         | CONDITIONS                                                                                            | MIN. | TYP. | MAX.     | UNITS |

|------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|----------|-------|

| Crystal Input Frequency (XIN)      | Fundamental crystal                                                                                   | 10   |      | 40       | MHz   |

|                                    | @ V <sub>DD</sub> = 3.3V, ±10%                                                                        |      |      | 200      |       |

| Input (FIN) Frequency              | @ V <sub>DD</sub> = 2.5V, ±10%                                                                        | 10   |      | 166      | MHz   |

|                                    | @ V <sub>DD</sub> = 1.8V, ±10%                                                                        |      |      | 110      |       |

| Input (FIN) Signal Amplitude       | Internally AC coupled                                                                                 | 0.8  |      | $V_{DD}$ | Vpp   |

|                                    | @ V <sub>DD</sub> = 3.3V, ±10% (High Drive)                                                           |      |      | 200      |       |

| Output Frequency                   | @ V <sub>DD</sub> = 2.5V, ±10% (High Drive)                                                           | 1    |      | 166      | MHz   |

|                                    | @ V <sub>DD</sub> = 1.8V, ±10% (High Drive)                                                           |      |      | 110      |       |

| Settling Time                      | At power-up ( $V_{DD} \ge 90\%$ of operating $V_{DD}$ )                                               |      |      | 2        | ms    |

| Output Enable Time                 | OE Function; Ta=25° C, 15pF Load. Add one clock period to this measurement for a usable clock output. |      |      | 500      | ns    |

|                                    | PDB Function; Ta=25° C, 15pF Load                                                                     |      |      | 2        | ms    |

| V <sub>DD</sub> Sensitivity        | Frequency vs. V <sub>DD,</sub> ±10%                                                                   | -2   |      | 2        | ppm   |

| Output Rise Time                   | 15pF Load, 10/90% V <sub>DD</sub> , High Drive, 3.3V                                                  |      | 1.2  | 1.7      | ns    |

| Output Fall Time                   | 15pF Load, 90/10% V <sub>DD</sub> , High Drive, 3.3V                                                  |      | 1.2  | 1.7      | ns    |

| Duty Cycle                         | PLL driven output, @ V <sub>DD</sub> /2, 15pF load,<br>High Drive, over entire frequency range        | 45   | 50   | 55       | %     |

| Period Jitter*<br>(10,000 samples) | Configuration dependant, with capacitive decoupling between V <sub>DD</sub> and GND.                  |      | 300  |          | ps    |

<sup>\*</sup> Note: Jitter performance depends on the programming parameters.

#### **DC SPECIFICATIONS**

| PARAMETERS                             | SYMBOL           | CONDITIONS                                               | MIN. | TYP. | MAX. | UNITS |

|----------------------------------------|------------------|----------------------------------------------------------|------|------|------|-------|

| Supply Current, V <sub>DD</sub> = 3.3V | I <sub>DD</sub>  | All 8 outputs @ 20MHz<br>No Load, V <sub>DD</sub> = 3.3V |      | 17   | 23   | mA    |

| Supply Current, V <sub>DD</sub> = 2.5V | I <sub>DD</sub>  | All 8 outputs @ 20MHz<br>No Load, V <sub>DD</sub> = 2.5V |      | 13.5 | 18   | mA    |

| Supply Current, V <sub>DD</sub> = 1.8V | I <sub>DD</sub>  | All 8 outputs @ 20MHz No Load, $V_{DD} = 1.8V$           |      | 9.5  | 13   | mA    |

| Supply Current                         | $I_{DD}$         | When PDB=0                                               |      | 10   |      | μA    |

|                                        |                  | Configured for 3.3V Operation                            | 2.97 | 3.3  | 3.63 |       |

| Operating Voltage                      | $V_{\text{DD}}$  | Configured for 2.5V Operation                            | 2.25 | 2.5  | 2.75 | V     |

|                                        |                  | Configured for 1.8V Operation                            | 1.62 | 1.8  | 1.98 |       |

| Output Low Voltage                     | V <sub>OL</sub>  | I <sub>OL</sub> = +4mA Std Drive, 3.3V                   |      |      | 0.4  | V     |

| Output High Voltage                    | V <sub>OH</sub>  | I <sub>OH</sub> = -4mA Std Drive, 3.3V                   | 2.4  |      |      | V     |

| Output Current, Low Drive              | I <sub>OSD</sub> | $V_{OL} = 0.4V, V_{OH} = 2.4V, 3.3V$                     | 4    |      |      | mA    |

| Output Current, Std Drive              | I <sub>OSD</sub> | $V_{OL} = 0.4V, V_{OH} = 2.4V, 3.3V$                     | 8    |      |      | mA    |

| Output Current, High Drive             | I <sub>OHD</sub> | $V_{OL} = 0.4V, V_{OH} = 2.4V, 3.3V$                     | 16   |      |      | mA    |

#### **CRYSTAL SPECIFICATIONS**

| PARAMETERS                              |                   | SYMBOL                | MIN | TYP | MAX | UNITS |

|-----------------------------------------|-------------------|-----------------------|-----|-----|-----|-------|

| Fundamental Crystal Resonator Frequency |                   | F <sub>XIN</sub>      | 10  |     | 40  | MHz   |

| Crystal Loading Rating                  |                   | C <sub>L (xtal)</sub> |     | 15  |     | pF    |

| Operating Drive Level                   |                   |                       |     | 0.1 | 2   | mW    |

| Motol Con Caratal                       | Shunt Capacitance | C0                    |     |     | 5.5 | pF    |

| Metal Can Crystal                       | ESR Max           | ESR                   |     |     | 40  | Ω     |

| Cmall CMD Cavatal                       | Shunt Capacitance | C0                    |     |     | 2.5 | pF    |

| Small SMD Crystal                       | ESR Max           | ESR                   |     |     | 60  | Ω     |

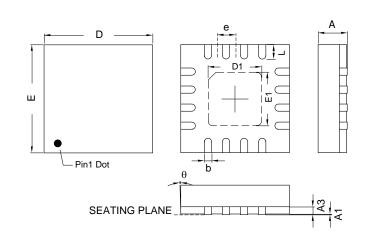

# 1.8V to 3.3V, PicoPLL, 3-PLL, 200MHz, 8 Output Clock IC PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

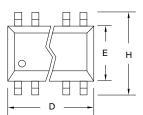

#### QFN-16L

| Symbol | Dimension in MM |      |

|--------|-----------------|------|

| Symbol | Min.            | Max. |

| Α      | 0.7             | 0.8  |

| A1     | 0.05            | 0.05 |

| А3     | 0.20            |      |

| b      | 0.18            | 0.30 |

| D      | 3.00 BSC        |      |

| Е      | 3.00 BSC        |      |

| D1     |                 | 1.70 |

| E1     |                 | 1.70 |

| L      | 0.30            | 0.50 |

| е      | 0.50 BSC        |      |

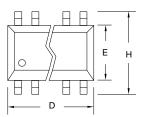

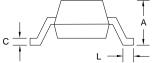

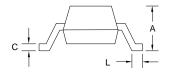

#### TSSOP-16L

| Symbol | Dimension in MM |      |  |

|--------|-----------------|------|--|

| Symbol | Min.            | Max. |  |

| Α      | -               | 1.20 |  |

| A1     | 0.05            | 0.15 |  |

| b      | 0.19            | 0.30 |  |

| С      | 0.09            | 0.20 |  |

| D      | 4.90            | 5.10 |  |

| Е      | 4.30            | 4.50 |  |

| Н      | 6.20            | 6.60 |  |

| L      | 0.45            | 0.75 |  |

| е      | 0.65 BSC        |      |  |

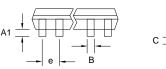

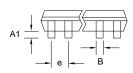

#### SSOP-16L

| Symbol | Dimension in MM |      |

|--------|-----------------|------|

|        | Min.            | Max. |

| Α      | 1.35            | 1.75 |

| A1     | 0.05            | 0.15 |

| b      | 0.20            | 0.30 |

| С      | 0.18            | 0.25 |

| D      | 4.80            | 5.00 |

| Е      | 3.80            | 3.98 |

| Н      | 5.80            | 6.20 |

| L      | 0.40            | 1.27 |

| е      | 0.635 BSC       |      |

# 1.8V to 3.3V, PicoPLL, 3-PLL, 200MHz, 8 Output Clock IC ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)

#### For part ordering, please contact our Sales Department:

2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

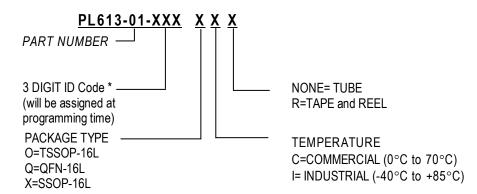

#### **PART NUMBER**

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

\* Micrel will assign a unique 3-digit ID code for each approved programmed part number.

| Part Number/Order Number | Marking <sup>†</sup>       | Package Option               |

|--------------------------|----------------------------|------------------------------|

| PL613-01-XXXOC           | P613-01<br>XXX(I)<br>LLLLL | 16-Pin TSSOP (Tube)          |

| PL613-01-XXXOC-R         | P613-01<br>XXX(I)<br>LLLLL | 16-Pin TSSOP (Tape and Reel) |

| PL613-01-XXXQC-R         | P61301<br>XXX(I)<br>LLL    | 16-Pin QFN (Tape and Reel)   |

| PL613-01-XXXXC           | P613-01<br>XXX(I)<br>LLLLL | 16-Pin SSOP (Tube)           |

| PL613-01-XXXXC-R         | P613-01<br>XXX(I)<br>LLLLL | 16-Pin SSOP (Tape and Reel)  |

Marking Notes

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.

<sup>1)</sup> The "I" after the three digit programming code will be marked for Industrial Temperature grade products only. Commercial grade products will not have a character in this position.

<sup>2)</sup> LLL represents the production lot number