### **ATPL Series Power Line Communications Device**

**DATASHEET**

## **Description**

ATPL250A is a G3-PLC modem for Power Line Communication. ATPL250A flexible architecture, composed of hardware accelerators and coprocessors, achieves a very efficient G3 PHY layer implementation.

ATPL250A is therefore a compact and high-efficient device for a wide range of Smart Grid applications such as Smart Metering (Smart Meters and Data Concentrators), Lighting, Industrial/Home Automation, Home and Building Energy Management Systems, Solar Energy and Plug-in Hybrid Electric Vehicle (PHEV) Charging Stations.

ATPL250A has been conceived to be bundled with an external Atmel<sup>®</sup> MCU. Atmel provides a G3 PHY layer library which is used by the external MCU to take control of ATPL250A PHY layer device.

ATMEL provides high-efficient, reduced BOM reference designs for different coupling options, targeting common configurations in standard frequency bands complying with existing regulations (CENELEC, FCC, ARIB).

### 1. Features

- G3-PLC modem

- Implements G3 CENELEC-A, FCC and ARIB profiles (ITU-T G.9903, June '14)

- Power Line Carrier Modem for 50 Hz and 60 Hz mains

- G3-PLC coherent and differential modulation schemes available

- Automatic Gain Control and continuous amplitude tracking in signal reception

- 1 SPI peripheral (slave) to external MCU

- Zero cross detection

- Embedded PLC Analog Front End (AFE), requires only external discrete high efficient Class D Line Driver for signal injection

- TA range -40°C to +85°C

- Package

- 80-lead LQFP

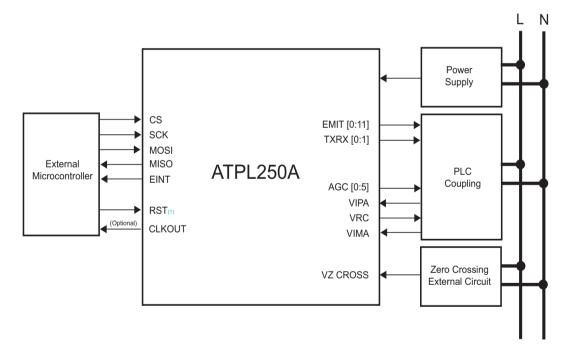

## 1.1 ATPL250A Application Block Diagram

ATPL250A has been conceived to be easily managed by an external microcontroller through a 5-line interface. This interface is comprised of a 4-line standard Serial Peripheral Interface (SPI) and an additional line used as interrupt from the ATPL250A to the external microcontroller. The external microcontroller can fully manage and control the ATPL250A (Phy layer, MAC coprocessing, etc.) by accessing the internal peripheral registers.

Figure 1-1. ATPL250A application example

Note: 1. There are several RST signals (ARST, SRST and PLL INIT), for more details see Section 3. "Signal Description".

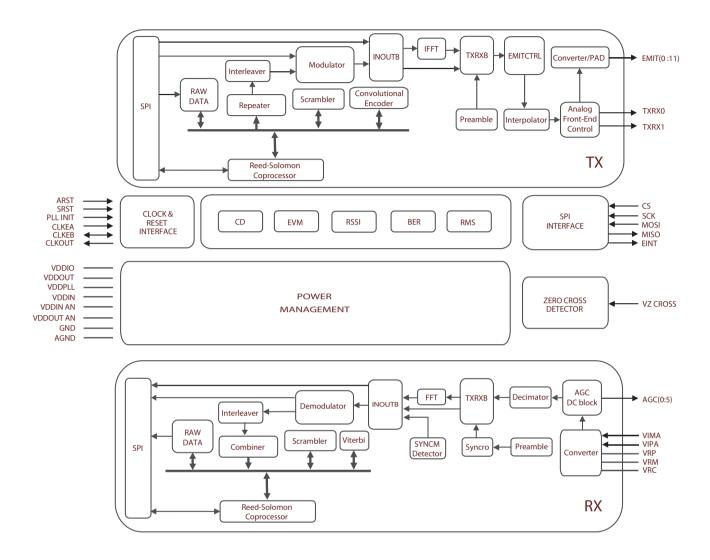

## 2. Block Diagram

Figure 2-1. ATPL250A Functional Block Diagram

# 3. Signal Description

Table 3-1. Signal Description List

| Signal Name                | Function                                                                                                                                                                                                                                                                 | Туре      | Active<br>Level | Voltage<br>reference | Comments                        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|----------------------|---------------------------------|

|                            | Power Sup                                                                                                                                                                                                                                                                | plies     | -               |                      |                                 |

| VDDIO                      | 3.3V digital supply. Digital power supply must be decoupled by external capacitors                                                                                                                                                                                       | Power     |                 |                      | 3.0V to 3.6V                    |

| VDDIN                      | 3.3V Digital LDO input supply                                                                                                                                                                                                                                            | Power     |                 |                      | 3.0V to 3.6V                    |

| VDDIN AN                   | 3.3V Analog LDO input supply                                                                                                                                                                                                                                             | Power     |                 |                      | 3.0V to 3.6V                    |

| VDDOUT AN                  | 1.2V Analog LDO output. A capacitor in the range 0.1 μF - 10 μF must be connected to each pin                                                                                                                                                                            | Power     |                 |                      | 1.2V                            |

| VDDOUT                     | 1.2V Digital LDO output. A capacitor in the range 0.1 $\mu F$ - 10 $\mu F$ must be connected to each pin                                                                                                                                                                 | Power     |                 |                      | 1.2V                            |

| VDDPLL                     | 1.2V PLL supply. It must be decoupled by a 100nF external capacitor, and connected to VDDOUT through a filter (Cut off frequency: 25 kHz)                                                                                                                                | Power     |                 |                      | 1.2V                            |

| GND <sup>(1)</sup>         | Digital Ground                                                                                                                                                                                                                                                           | Power     |                 |                      |                                 |

| AGND <sup>(1)</sup>        | Analog Ground                                                                                                                                                                                                                                                            | Power     |                 |                      |                                 |

|                            | Clocks, Oscillator                                                                                                                                                                                                                                                       | s and PLL | s               |                      |                                 |

| CLKEA <sup>(2)</sup>       | External Clock Oscillator     CLKEA must be connected to one terminal of a crystal (when a crystal is being used) or used as input for external clock signal                                                                                                             | Input     |                 | VDDIO                |                                 |

| CLKEB <sup>(2)</sup>       | External Clock Oscillator     CLKEB must be connected to one terminal of a crystal (when a crystal is being used) or must be floating when an external clock signal is connected through CLKEA                                                                           | I/O       |                 | VDDIO                |                                 |

| CLKOUT                     | 12 MHz CLK Output                                                                                                                                                                                                                                                        | Output    |                 | VDDIO                |                                 |

|                            | Reset/Te                                                                                                                                                                                                                                                                 | st        | 1               |                      |                                 |

| ARST                       | Asynchronous Reset                                                                                                                                                                                                                                                       | Input     | Low             | VDDIO                | Internal pull up <sup>(3)</sup> |

| SRST                       | Synchronous Reset                                                                                                                                                                                                                                                        | Input     | Low             | VDDIO                | Internal pull up <sup>(3)</sup> |

| PLL INIT                   | PLL Initialization Signal                                                                                                                                                                                                                                                | Input     | Low             | VDDIO                | Internal pull up <sup>(3)</sup> |

|                            | GPLC (G3 Power Line Comm                                                                                                                                                                                                                                                 | unication | s) Transce      | eiver                |                                 |

| EMIT [0:11] <sup>(4)</sup> | PLC Tri-state Transmission ports                                                                                                                                                                                                                                         | Output    |                 | VDDIO                |                                 |

| AGC [0:5]                  | Automatic Gain Control:     These digital tri-state outputs are managed by AGC hardware logic to drive external circuitry when input signal attenuation is needed                                                                                                        | Output    |                 | VDDIO                |                                 |

| TXRX0                      | Analog Front-End Transmission/Reception for TXDRV0  This digital output is used to modify external coupling behavior in Transmission/Reception. The suitable value depends on the external circuitry configuration. The polarity of this pin can be inverted by software | Output    |                 | VDDIO                |                                 |

**Table 3-1. Signal Description List**

| Signal Name             | Function                                                                                                                                                                                                                                                                 | Туре        | Active<br>Level | Voltage<br>reference | Comments                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|----------------------|-----------------------------------|

| TXRX1                   | Analog Front-End Transmission/Reception for TXDRV1  This digital output is used to modify external coupling behavior in Transmission/Reception. The suitable value depends on the external circuitry configuration. The polarity of this pin can be inverted by software | Output      |                 | VDDIO                |                                   |

| VZ CROSS <sup>(5)</sup> | Mains Zero-Cross Detection Signal:     This input detects the zero-crossing of the mains voltage                                                                                                                                                                         | Input       |                 | VDDIO                | Internal pull down <sup>(3)</sup> |

| VIMA                    | Negative Differential Voltage Input                                                                                                                                                                                                                                      | Input       |                 | VDDOUT AN            |                                   |

| VIPA                    | Positive Differential Voltage Input                                                                                                                                                                                                                                      | Input       |                 | VDDOUT AN            |                                   |

| VRP                     | Internal Reference "Plus" Voltage. Connect an external decoupling capacitor between VRP and VRM (1nF - 100nF)                                                                                                                                                            | Output      |                 | VDDOUT AN            |                                   |

| VRM                     | Internal Reference "Minus" Voltage. Connect an external decoupling capacitor between VRP and VRM (1nF - 100nF)                                                                                                                                                           | Output      |                 | VDDOUT AN            |                                   |

| VRC                     | Common-mode Voltage. Bypass to analog ground with an external decoupling capacitor (100pF - 1nF)                                                                                                                                                                         | Output      |                 | VDDOUT AN            |                                   |

|                         | Serial Peripheral In                                                                                                                                                                                                                                                     | terface - S | SPI             |                      |                                   |

| cs                      | SPI CS • SPI bridge Slave Select                                                                                                                                                                                                                                         | Input       | Low             | VDDIO                | Internal pull up <sup>(3)</sup>   |

| SCK                     | SPI SCK • SPI bridge Clock signal                                                                                                                                                                                                                                        | Input       |                 | VDDIO                | Internal pull up <sup>(3)</sup>   |

| MOSI                    | SPI MOSI • SPI bridge Master Out Slave In                                                                                                                                                                                                                                | Input       |                 | VDDIO                | Internal pull up <sup>(3)</sup>   |

| MISO                    | SPI MISO • SPI bridge Master In Slave Out                                                                                                                                                                                                                                | Output      |                 | VDDIO                |                                   |

| EINT                    | PHY Layer External Interrupt                                                                                                                                                                                                                                             | Output      | Low             | VDDIO                |                                   |

- Notes: 1. Separate pins are provided for GND and AGND grounds. Layout considerations should be taken into account to reduce interference. Ground pins should be connected as shortly as possible to the system ground plane. For more details about EMC Considerations, please refer to AVR040 application note.

- 2. The crystal should be located as close as possible to CLKEA and CLKEB pins. See Table 6-7 on page 19.

- 3. See Table 6-5 on page 16.

- 4. Different configurations allowed depending on external topology and net behavior.

- 5. Depending on whether an isolated or a non-isolated power supply is being used, isolation of this pin should be taken into account in the circuitry design. Please refer to the Reference Design for further information.

## 4. Package and Pinout

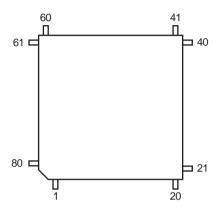

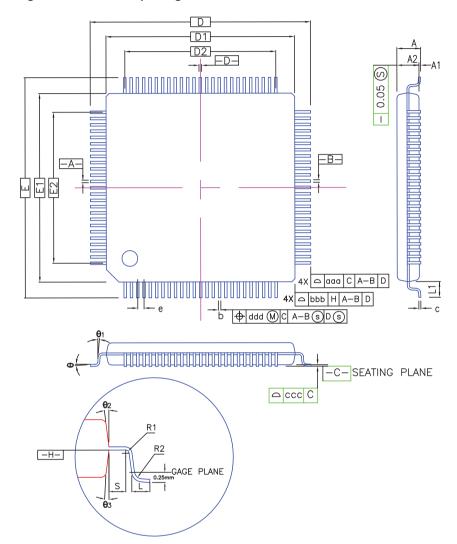

## 4.1 80-Lead LQFP Package Outline

The 80-lead LQFP package has a 0.5 mm pitch and respects Green standards.

Figure 4-1 shows the orientation of the 80-lead LQFP package. Refer to the section "Mechanical Characteristics" for the 80-lead LQFP package mechanical drawing.

Figure 4-1. Orientation of the 80-Lead LQFP Package

## 4.2 80-Lead LQFP Pinout

Table 4-1. 80 - Lead LQFP Pinout

| 1  | NC       | 21 | VDDIO  | 41 | GND    | 61 | GND       |

|----|----------|----|--------|----|--------|----|-----------|

| 2  | NC       | 22 | NC     | 42 | EMIT8  | 62 | AGND      |

| 3  | NC       | 23 | CLKOUT | 43 | EMIT9  | 63 | VDDOUT AN |

| 4  | ARST     | 24 | CS     | 44 | EMIT10 | 64 | VIMA      |

| 5  | PLL INIT | 25 | SCK    | 45 | EMIT11 | 65 | VIPA      |

| 6  | GND      | 26 | MOSI   | 46 | VDDIO  | 66 | VDDOUT AN |

| 7  | CLKEA    | 27 | MISO   | 47 | GND    | 67 | AGND      |

| 8  | GND      | 28 | VDDIO  | 48 | VDDOUT | 68 | VRP       |

| 9  | CLKEB    | 29 | GND    | 49 | TXRX0  | 69 | VRM       |

| 10 | VDDIO    | 30 | EMIT0  | 50 | TXRX1  | 70 | VRC       |

| 11 | GND      | 31 | EMIT1  | 51 | GND    | 71 | VDDIN AN  |

| 12 | VDDPLL   | 32 | EMIT2  | 52 | AGC2   | 72 | AGND      |

| 13 | GND      | 33 | EMIT3  | 53 | AGC5   | 73 | AGND      |

| 14 | VDDIN    | 34 | VDDIO  | 54 | AGC1   | 74 | VDDIN AN  |

| 15 | VDDIN    | 35 | GND    | 55 | AGC4   | 75 | GND       |

| 16 | GND      | 36 | EMIT4  | 56 | AGC0   | 76 | VDDIO     |

| 17 | VDDOUT   | 37 | EMIT5  | 57 | AGC3   | 77 | VZ CROSS  |

| 18 | GND      | 38 | EMIT6  | 58 | VDDIO  | 78 | NC        |

| 19 | NC       | 39 | EMIT7  | 59 | GND    | 79 | NC        |

| 20 | SRST     | 40 | VDDIO  | 60 | EINT   | 80 | NC        |

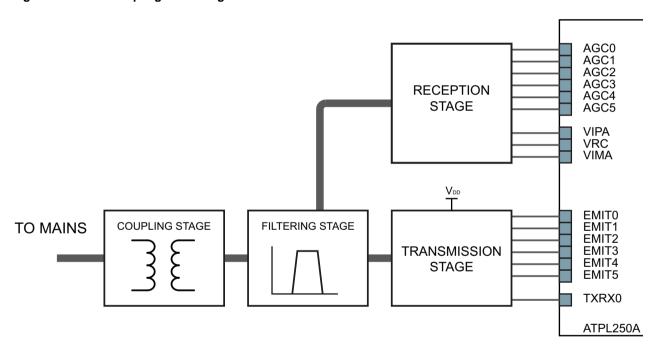

## 5. Analog Front-End

### 5.1 PLC coupling circuitry description

Atmel PLC coupling reference designs have been designed to achieve high performance, low cost and simplicity.

With these values on mind, Atmel has developed a set of PLC couplings covering frequencies below 500 kHz compliant with different applicable regulations.

Atmel PLC technology is purely digital and does not require external DAC/ADC, thus simplifying the external required circuitry. Generally Atmel PLC coupling reference designs make use of few passive components plus a Class D amplification stage for transmission.

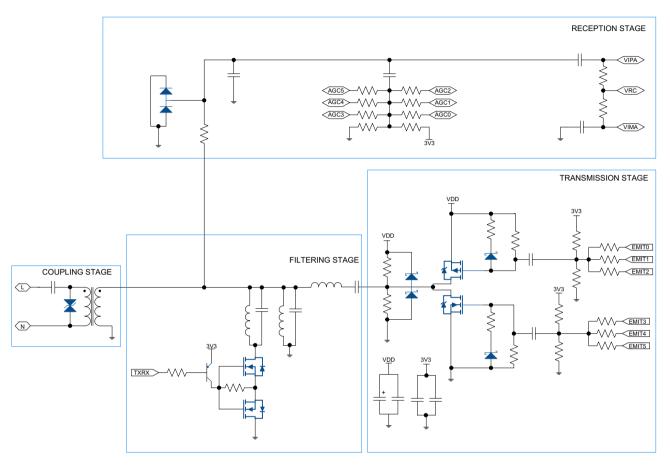

All PLC coupling reference designs are generally composed by the same sub-circuits:

- Transmission Stage

- Reception Stage

- Filtering Stage

- Coupling Stage

Figure 5-1. PLC coupling block diagram

A particular reference design can contain more than one sub-circuit of the same kind (i.e.: two transmission stages).

### 5.1.1 Transmission Stage

The transmission stage adapts the EMIT signals and amplifies them if required. It can be composed by:

- Driver: A group of resistors which adapt the EMIT signals to either control the Class-D amplifier or to be filtered by the next stage.

- Amplifier: If required, a Class-D amplifier which generates a square waveform from 0 to V<sub>DD</sub> is included.

- Bias and protection: A couple of resistors and a couple of Schottky barrier diodes provide a DC component and provide protection from received disturbances.

Transmission stage shall be always followed by a filtering stage.

### 5.1.2 Filtering Stage

The filtering stage is composed by band-pass filters which have been designed to achieve high performance in field deployments complying at the same time with the proper normative and standards.

The in-band flat response filtering stage does not distort the injected signal, reduces spurious emission to the limits set by the corresponding regulation and blocks potential interferences from other transmission channels.

The Filtering stage has three aims:

- Band-pass filtering of high frequency components of the square waveform generated by the Transmission Stage.

- Adapt Input/Output impedances for optimal reception/transmission. This is controlled by TXRX signal.

- In some cases, Band-pass filtering for received signals.

When the system is intended to be connected to a physical channel with high voltage or which is not electrically referenced to the same point then the filtering stage must be always followed by a coupling stage.

#### 5.1.3 Coupling Stage

The coupling stage blocks the DC component of the line to/from which the signal is injected/received (i.e.: 50/60 Hz of the mains). This is carried out by a high voltage capacitor.

Coupling stage could also electrically isolate the coupling circuitry from the external world by means of a 1:1 transformer.

#### 5.1.4 Reception Stage

The reception stage adapts the received analog signal to be properly captured by the ATPL250A internal reception chain. Reception circuit is independent of the PLC channel which is being used. It basically consists of:

- Anti aliasing filter (RC Filter)

- Automatic Gain Control (AGC) circuit

- Driver of the internal ADC

The AGC circuit avoids distortion on the received signal that may arise when the input signal is high enough to polarize the protective diodes in direct region.

The driver to the internal ADC comprises a couple of resistors and a couple of capacitors. This driver provides a DC component and adapts the received signal to be properly converted by the internal reception chain.

### 5.1.5 Generic PLC Coupling

Please consider that this is a generic PLC Coupling design for a particular application please refer to Atmel doc43052 "PLC Coupling Reference Designs".

Figure 5-2. PLC Coupling block diagram detailed

## 5.2 ATPLCOUP reference designs

Atmel provides PLC coupling reference designs for different applications and frequency bands up to 500 kHz. Please refer to Atmel doc43052 "PLC Coupling Reference Designs" for a detailed description.

## 5.3 Zero-crossing detector

#### 5.3.1 Overview

Zero Crossing Detector block works predicting future zero crossing in function of the past zero crossings. To achieve this, the system embeds a configurable Input Signal Management (ISM) block and a PLL, both of which manage Zero Crossing Detector Input Signal to calculate Zero Crossing Output Flag. The zero-cross detection of waves of 50 Hz and 60 Hz with ±10% of error is supported.

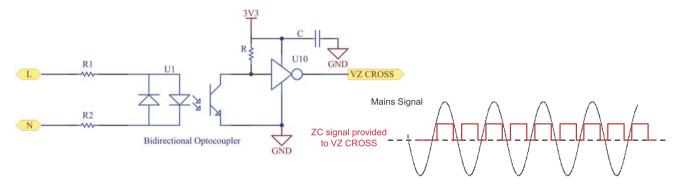

The PLL block interprets its input signal such a way that it indicates a zero cross in the middle of a positive pulse. It is important to note that depending on the external circuit which implements the Zero Crossing Detector Input Signal this interpretation is not always correct. So for these cases it is required to transform the Input Signal in a signal where the middle of a positive pulse corresponds to a truly zero cross. This transformation is implemented through the Input Signal Management (ISM) configured by MODE INV and MODE REP fields in ZC CONFIG register.

Zero Crossing Detector Input Signal (VZ CROSS) must fulfil some requirements. The first requirement is that VZ CROSS signal must be a pulse train which its duty cycle must be >60% or <40% (polarity is configurable). In addition, if we have to detect Ascent or Descent zero-crossing, Zero Crossing Detector Input Signal period must be equal than period of the wave we need to obtain zero-crossing. Ascent and Descent Zero Crossing Detection are configured by setting MODE MUX and MODE ASC fields in ZC CONFIG register.

Figure 5-3. Typical circuit, using a bidirectional optocoupler and a Schmitt trigger

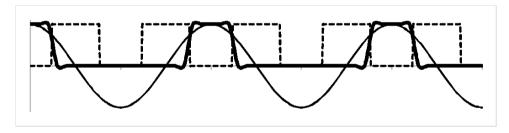

The input signal "VZ CROSS" (wider line) generated by this circuit for Zero Cross Detection of the wave "L"-"N" (finer line) is plotted in next figure. The digital signal at output of Input Signal Management (ISM) is plotted in Figure 5-4.

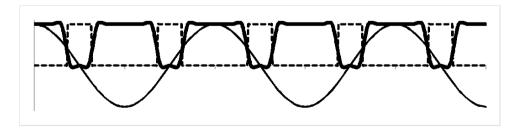

Figure 5-4. Digital signal (dashed line) at output of Input Signal Management (ISM) internal block

For this circuit, Zero Cross Internal registers should be configured this way:

```

ZC_CONFIG.MODE_MUX = '0'

ZC_CONFIG.MODE_ASC = '0'

ZC_CONFIG.MODE_INV = '1'

ZC_CONFIG.MODE_REP = '0'

ZC_CONFIG.FILTER_BP = '0'

```

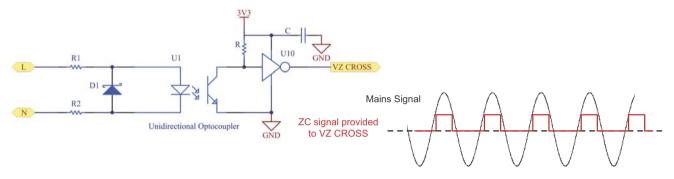

Some situations (for example in some protocols like G3) could require only ascent (or descent) mains signal zero-crossings to be detected. When we have to detect Ascent or Descent Zero Cross of the wave (finer line), the circuit should generate an input signal "VZ CROSS" (wider line) with the same period, as specified in next figure. This could be easily implemented by using an unidirectional optocoupler or a Zener diode topology in the external circuitry.

Figure 5-5. Typical circuit, using a unidirectional optocoupler and a Schmitt trigger

The digital signal at output of Input Signal Management (ISM) is plotted in Figure 5-6.

Figure 5-6. Digital signal (dashed line) at output of Input Signal Management (ISM) internal block

For this case, Zero Cross Internal registers should be configured this way:

```

ZC_CONFIG.MODE_MUX = '1'

ZC_CONFIG.MODE_ASC = '0'(ascent) or '1'(descent)

ZC_CONFIG.MODE_INV = '1'

ZC_CONFIG.MODE_REP = '1'

ZC_CONFIG.FILTER_BP = '0'

```

#### 5.3.2 Zero Crossing Config register

Name: ZC\_CONFIG

Address: 0x4A0

Access: Read/Write Reset: 0x00023210

| 31           | 30      | 29      | 28 | 27                      | 26       | 25              | 24              |

|--------------|---------|---------|----|-------------------------|----------|-----------------|-----------------|

| -            | -       | -       | -  | -                       | -        | -               | -               |

| 23           | 22      | 21      | 20 | 19                      | 18       | 17              | 16              |

| -            | -       | -       | -  | -                       | Reserved | PEAK2_ZC<br>_EN | PEAK1_ZC<br>_EN |

|              |         |         |    |                         |          |                 |                 |

| 15           | 14      | 13      | 12 | 11                      | 10       | 9               | 8               |

| 15<br>-      | 14      | 13      | •= | 11<br>LTER_NUM [6:      |          | 9               | 8               |

| 15<br>-<br>7 | 14<br>6 | 13<br>5 | •= | 11<br>LTER_NUM [6:<br>3 |          | 9               | 0               |

• MODE\_MUX: Zero Crossing Mode

'0': Selection of both ascent and descent zero-crossing

'1': Selection of ascent or descent zero-crossing

MODE ASC: Ascent-Descent Mode

'0': If MODE\_MUX is 1, Ascent Zero Crossing

'1': If MODE\_MUX is 1, Descent Zero Crossing

• MODE INV: Inversion Mode

'0': No effect.

'1': Zero Crossing Detector Input Signal is inverted.

• MODE\_REP: Repetition Mode

'0': No effect.

'1': Zero Crossing Detector Input Signal period is down by half.

• FILTER\_BP: Zero Crossing Input Signal Filter Enable

'0': Filter enabled.

'1': Filter not enabled.

• FILTER\_NUM[6:0]: Zero Crossing Input Signal Filter Parameter

Time (counted in number of clock cycles) that the Zero Crossing Input Signal (1-bit) must be constant to set that value as the input signal for Zero Crossing Detection. Used to refuse fast transitions in Zero Crossing Input Signal.

- **PEAK1\_ZC\_EN:** indicates if PEAK\_ZC\_TIME updates its value with the last ZC\_TIME when a PEAK1 is detected. It is active high.

- **PEAK2\_ZC\_EN:** indicates if PEAK\_ZC\_TIME updates its value with the last ZC\_TIME when a PEAK2 is detected. It is active high.

## 6. Electrical characteristics

## 6.1 Absolute Maximum Ratings

Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions given in the Recommended Operating Conditions section. Exposure to the Absolute Maximum Conditions for extended periods may affect device reliability.

Table 6-1. Absolute Maximum Ratings

| Parameter                     | Symbol          | Rating                        | Unit |  |

|-------------------------------|-----------------|-------------------------------|------|--|

| Supply Voltage                | VDDIO           | -0.5 to 4.0                   |      |  |

| Input Voltage                 | VI              | -0.5 to VDDIO +0.5 (≤ 4.0V)   | V    |  |

| Output Voltage                | VO              | VO -0.5 to VDDIO +0.5 (<4.0V) |      |  |

| Storage Temperature           | T <sub>ST</sub> | -55 to 125                    | °C   |  |

| Junction Temperature          | T <sub>J</sub>  | -40 to 125                    | , J  |  |

| Output Current <sup>(1)</sup> | Ю               | ±10 <sup>(2)</sup>            | mA   |  |

Notes: 1. DC current that continuously flows for 10 ms or more, or average DC current.

2. Applies to all the pins except EMIT pins. EMIT pins should be only used according to circuit configurations recommended by Atmel.

#### **ATTENTION observe EDS precautions**

Precautions for handling electrostatic sensitive devices should be taken into account to avoid malfunction. Charged devices and circuit boards can discharge without detection.

## 6.2 Recommended Operating Conditions

Table 6-2. Recommended Operating Conditions

| Parameter            | Symbol         |      |      | Unit |      |  |

|----------------------|----------------|------|------|------|------|--|

| Parameter            | Symbol         | Min  | Тур  | Max  | Onit |  |

| Supply Voltage       | VDDIO          | 3.00 | 3.30 | 3.60 |      |  |

|                      | VDDIN AN       |      | 3.30 | 3.60 | V    |  |

| Supply Voltage       | VDDIN          | 3.00 | 3.30 | 3.60 | V    |  |

|                      | VDDPLL         | 1.08 | 1.20 | 1.32 |      |  |

| Junction Temperature | T <sub>J</sub> | -40  | 25   | 125  | 00   |  |

| Ambient Temperature  | T <sub>A</sub> | -40  | -    | 85   | °C   |  |

Table 6-3. Thermal Data

| Parameter                                     | Symbol                | Cond       | itions    | LQFP80 | Unit |

|-----------------------------------------------|-----------------------|------------|-----------|--------|------|

| Parameter                                     | Symbol                | PCB Layers | Air Speed |        | Unit |

|                                               |                       |            | 0 m/s     | 64     |      |

|                                               |                       | 2          | 1 m/s     | 56     |      |

| Thermal resistance junction-to-ambient steady | _                     |            | 3 m/s     | 48     |      |

| state                                         | R <sub>Theta-ja</sub> |            | 0 m/s     | 43     | °C/W |

|                                               |                       | 4          | 1 m/s     | 40     |      |

|                                               |                       |            | 3 m/s     | 36     |      |

Theta-ja is calculated based on a standard JEDEC defined environment and is not reliable indicator of a device's thermal performance in a non-JEDEC environment. The customer should always perform their own calculations/simulations to ensure that their system's thermal performance is sufficient.

## 6.3 Electrical Pinout

Table 6-4. 80 - Lead LQFP Electrical Pinout

| Pin No | Pin Name | I/O | I(mA) | Res | HY | Pin No | Pin Name  | I/O | I(mA) | Res | HY |

|--------|----------|-----|-------|-----|----|--------|-----------|-----|-------|-----|----|

| 1      | NC       | -   | -     | -   | -  | 41     | GND       | Р   | -     | -   | -  |

| 2      | NC       | -   | -     | -   | -  | 42     | EMIT8     | ОТ  | ± 16  | -   | -  |

| 3      | NC       | -   | -     | -   | -  | 43     | EMIT9     | ОТ  | ± 16  | -   | -  |

| 4      | ARST     | I   | -     | PU  | Υ  | 44     | EMIT10    | ОТ  | ± 16  | -   | -  |

| 5      | PLL INIT | I   | -     | PU  | Υ  | 45     | EMIT11    | ОТ  | ± 16  | -   | -  |

| 6      | GND      | Р   | -     | -   | -  | 46     | VDDIO     | Р   | -     | -   | -  |

| 7      | CLKEA    | I   | -     | -   | -  | 47     | GND       | Р   | -     | -   | -  |

| 8      | GND      | Р   | -     | -   | -  | 48     | VDDOUT    | Р   | -     | -   | -  |

| 9      | CLKEB    | I/O | -     | -   | -  | 49     | TXRX0     | 0   | ± 8   | -   | -  |

| 10     | VDDIO    | Р   | -     | -   | -  | 50     | TXRX1     | 0   | ± 8   | -   | -  |

| 11     | GND      | Р   | -     | -   | -  | 51     | GND       | Р   | -     | -   | -  |

| 12     | VDDPLL   | Р   | -     | -   | -  | 52     | AGC2      | OT  | ± 16  | -   | Υ  |

| 13     | GND      | Р   | -     | -   | -  | 53     | AGC5      | OT  | ± 16  | -   | Υ  |

| 14     | VDDIN    | Р   | -     | -   | -  | 54     | AGC1      | OT  | ± 6   | -   | Y  |

| 15     | VDDIN    | Р   | -     | -   | -  | 55     | AGC4      | OT  | ± 6   | -   | Y  |

| 16     | GND      | Р   | -     | -   | -  | 56     | AGC0      | OT  | ± 4   | -   | Υ  |

| 17     | VDDOUT   | Р   | -     | -   | -  | 57     | AGC3      | ОТ  | ± 4   | -   | Υ  |

| 18     | GND      | Р   | -     | -   | -  | 58     | VDDIO     | Р   | -     | -   | -  |

| 19     | NC       | -   | -     | -   | -  | 59     | GND       | Р   | -     | -   | -  |

| 20     | SRST     | I   | -     | PU  | Y  | 60     | EINT      | 0   | ± 4   | -   | -  |

| 21     | VDDIO    | Р   | -     | -   | -  | 61     | GND       | Р   | -     | -   | -  |

| 22     | NC       | -   | -     | -   | -  | 62     | AGND      | Р   | -     | -   | -  |

| 23     | CLKOUT   | 0   | ± 8   | -   | -  | 63     | VDDOUT AN | Р   | -     | -   | -  |

| 24     | CS       | I   | -     | PU  | Y  | 64     | VIMA      | I   | -     | -   | -  |

| 25     | SCK      | ı   | -     | PU  | Y  | 65     | VIPA      | I   | -     | -   | -  |

| 26     | MOSI     | I   | -     | PU  | Y  | 66     | VDDOUT AN | Р   | -     | -   | -  |

| 27     | MISO     | 0   | ± 6   | -   | -  | 67     | AGND      | Р   | -     | -   | -  |

| 28     | VDDIO    | Р   | -     | -   | -  | 68     | VRP       | 0   | -     | -   | -  |

| 29     | GND      | Р   | -     | ı   | -  | 69     | VRM       | 0   | -     | ı   | -  |

| 30     | EMIT0    | OT  | ± 16  | ı   | -  | 70     | VRC       | 0   | -     | ı   |    |

| 31     | EMIT1    | ОТ  | ± 16  | ı   | -  | 71     | VDDIN AN  | Р   | -     | ı   | -  |

| 32     | EMIT2    | OT  | ± 16  | ı   | -  | 72     | AGND      | Р   | -     | 1   | -  |

| 33     | EMIT3    | ОТ  | ± 16  | ı   | -  | 73     | AGND      | Р   | -     | ı   | -  |

| 34     | VDDIO    | Р   | -     | -   | -  | 74     | VDDIN AN  | Р   | -     | -   | -  |

| 35     | GND      | Р   | -     | -   | -  | 75     | GND       | Р   | -     | -   | -  |

| 36     | EMIT4    | ОТ  | ± 16  | -   | -  | 76     | VDDIO     | Р   | -     | -   | -  |

| 37     | EMIT5    | ОТ  | ± 16  | -   | -  | 77     | VZ CROSS  | I   | -     | PD  | Y  |

| 38     | EMIT6    | ОТ  | ± 16  | -   | -  | 78     | NC        | -   | -     | 1   |    |

| 39     | EMIT7    | ОТ  | ± 16  | -   | -  | 79     | NC        | -   | -     | -   | -  |

| 40     | VDDIO    | Р   | -     | -   | -  | 80     | NC        | -   | -     | -   | -  |

I/O = pin direction: I = input, O = output, T = tri-state, P = power

I(mA) = nominal current: + = source, - = sink, X = fixed by external resistor. See "V-I curves"

Res = pin pull up/pull down resistor: PU = pull up, PD = pull down (15 - 70 k $\Omega$ , typical 33 k $\Omega$ )

HY = Input Hysteresis: Y = yes

## 6.4 DC Characteristics

Table 6-5. ATPL250A DC Characteristics

| Parameter.                                 | 0                         | 0     |                          |            | 11         |      |

|--------------------------------------------|---------------------------|-------|--------------------------|------------|------------|------|

| Parameter                                  | Condition Symbol          |       | Min                      | Тур        | Max        | Unit |

| Supply Voltage                             |                           | VDDIO | 3.00                     | 3.30       | 3.60       |      |

| H-level Input Voltage (3.3V CMOS)          |                           | VIH   | 2.0                      | -          | VDDIO +0.3 |      |

| L-level Input Voltage (3.3V CMOS)          | VIL                       | -0.3  | -                        | 0.8        | V          |      |

| H-level Output Voltage                     | 3.3V I/O<br>IOH = -100 μA | VOH   | VDDIO -0.2               | .2 - VDDIO |            |      |

| L-level Output Voltage                     | 3.3V I/O<br>IOL = 100 μA  | VOL   | 0                        | 0 - 0.2    |            |      |

| H-level Output V - I Characteristics       | 3.3V I/O<br>VDDIO=3.3±0.3 | ЮН    | See "V-I curves" section |            |            | m A  |

| L-level Output V - I Characteristics       | 3.3V I/O<br>VDDIO=3.3±0.3 | IOL   | See "V-I curves" section |            |            | mA   |

| Internal Pull-up Resistor <sup>(1)</sup>   | 3.3V I/O                  | Rpu   | 15 33 70                 |            | 70         | 1.0  |

| Internal Pull-down Resistor <sup>(1)</sup> | 3.3V I/O                  | Rpd   | 15                       | 33         | 70         | kΩ   |

Note: 1. Only applicable to pins with internal pulling.

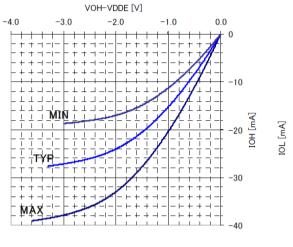

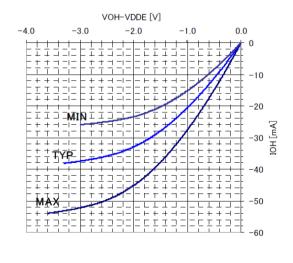

## 6.4.1 V-I curves

V-I Characteristics 3.3V standard CMOS IO L, M type

Apply to pins EINT, AGC0, AGC3

Condition: MIN Process = Slow  $T_J = 125^{\circ}\text{C}$  VDDIO = 3.0V

TYP Process = Typical  $T_J = 25^{\circ}\text{C}$  VDDIO = 3.3V MAX Process = Fast  $T_J = -40^{\circ}\text{C}$  VDDIO = 3.6V

Figure 6-1. V-I curves for pins EINT, AGC0, AGC3

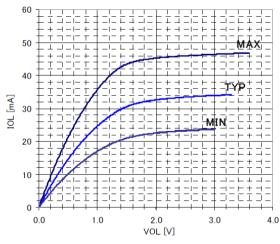

Apply to pins MISO, AGC1, AGC4

Condition: MIN Process = Slow  $T_J = 125$ °C VDDIO = 3.0V

TYP Process = Typical  $T_J = 25^{\circ}\text{C}$  VDDIO = 3.3V MAX Process = Fast  $T_J = -40^{\circ}\text{C}$  VDDIO = 3.6V

Figure 6-2. V-I curves for pins MISO, AGC1, AGC4

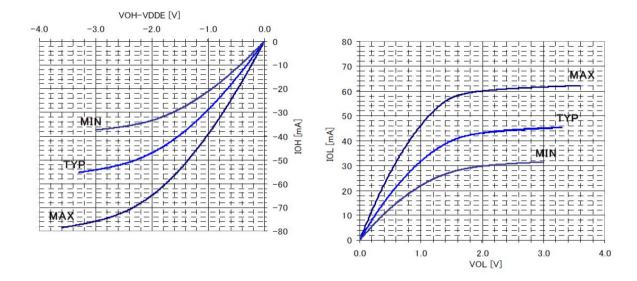

### Apply to pins CLKOUT, TXRX0, TXRX1

Condition: MIN Process = Slow  $T_J = 125^{\circ}\text{C}$  VDDIO = 3.0V TYP Process = Typical  $T_J = 25^{\circ}\text{C}$  VDDIO = 3.3V MAX Process = Fast  $T_J = -40^{\circ}\text{C}$  VDDIO = 3.6V

Figure 6-3. V-I curves for pins CLKOUT, TXRX0, TXRX1

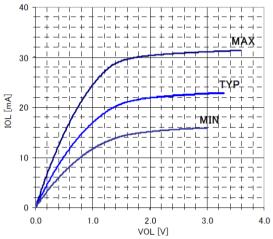

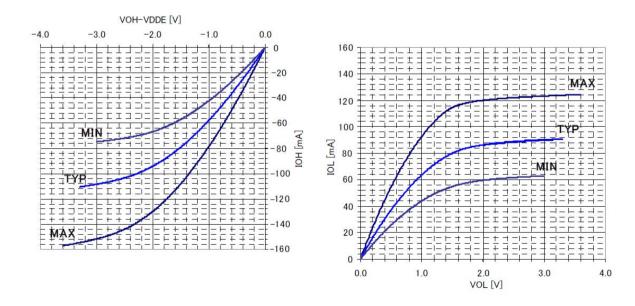

Apply to pins EMIT [0:11], AGC2, AGC5

Condition: MIN Process = Slow  $T_J = 125^{\circ}\text{C}$  VDDIO = 3.0V TYP Process = Typical  $T_J = 25^{\circ}\text{C}$  VDDIO = 3.3V MAX Process = Fast  $T_J = -40^{\circ}\text{C}$  VDDIO = 3.6V

Figure 6-4. V-I curves for pins EMIT [0:11], AGC2, AGC5

## 6.5 Power Consumption

Table 6-6. Power Consumption

| Parameter                      | Condition              | Symbol           |     | Unit |     |       |  |

|--------------------------------|------------------------|------------------|-----|------|-----|-------|--|

| rarameter                      | Condition              | Symbol           | Min | Тур  | Max | Oilit |  |

|                                | T <sub>J</sub> = 25°C  |                  |     | 245  |     |       |  |

| Dower Consumption              | VDDIO = 3.3V           | В                |     |      | -   |       |  |

| Power Consumption              | VDDIN = 3.3V           | P <sub>25</sub>  | -   |      |     |       |  |

|                                | VDDIN AN = 3.3V        |                  |     |      |     | mW    |  |

|                                | T <sub>J</sub> = 125°C |                  |     |      |     | IIIVV |  |

| Power Consumption (worst case) | VDDIO = 3.6V           | P <sub>125</sub> | -   | -    | 330 |       |  |

| Power Consumption (worst case) | <b>VDDIN = 3.6V</b>    | 125              |     |      |     |       |  |

|                                | VDDIN AN = 3.6V        |                  |     |      |     |       |  |

### 6.6 Oscillator

Table 6-7. ATPL250A 24 MHz Crystal Oscillator Characteristics

| Barranatan                       | Tool Condition          | Ols all              |     | g   | 1111       |      |

|----------------------------------|-------------------------|----------------------|-----|-----|------------|------|

| Parameter                        | Test Condition          | Symbol               | Min | Тур | Max        | Unit |

| Crystal Oscillator frequency     | Fundamental             | X <sub>tal</sub>     |     | 24  |            | MHz  |

| External Oscillator Capacitance  | C <sub>XTAL</sub>       | -                    | 18  | -   |            |      |

| External capacitor on CLKEA a    | C <sub>X</sub>          | -                    | 27  | -   | pF         |      |

| Internal parasitic capacitance   | Between CLKEA and CLKEB | C <sub>PARA24M</sub> | -   | 4   | -          |      |

| H-level Input Voltage            |                         | XVIH                 | 2   | -   | VDDIO +0.3 | V    |

| L-level Input Voltage            | L-level Input Voltage   |                      |     | -   | 0.8        | V    |

| External Oscillator Parallel Res | Rp                      | not needed           |     |     | 0          |      |

| External Oscillator Series Resis | stance                  | Rs                   | -   | 220 | -          | Ω    |

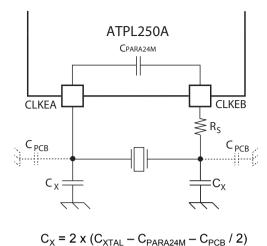

Notes: 1. The crystal should be located as close as possible to CLKEB and CLKEA pins.

- 2. Recommended value for Cx is 27 pF and Rs 220  $\Omega$ . These values may depend on the specific crystal characteristics and PCB layout. See example below. For further information please refer to Atmel doc43084 "Crystal Selection Guidelines" application note.

- 3. As a requirement of G3 specification, the System Clock tolerance from which transmit frequency and symbol timing are derived shall be ± 25 ppm maximum. Crystal Stability/Tolerance/Ageing values must be selected according to standard G3 requirements.

Figure 6-5. 24 MHz Crystal Oscillator Schematic

where  $C_{PCB}$  is the ground referenced parasitic capacitance of the printed circuit board (PCB) on CLKEA and CLKEB tracks.

As a practical example, taking the following crystal part number:

Manufacturer: TXC CORPORATION PartNumber: 9C-24.000MEEJ-T

Frequency: 24.000 MHz

Tolerance: 10 ppm (as low as possible to fullfil G3 specification requirements)

$C_{XTAL} = 18 pF$

Working in a typical layout / substrate with  $C_{PCB} = 1 pF$

The value of the external capacitors on CLKEA and CLKEB should be  $C_X = 2 \times (18 - 4 - 0.5) = 27 \text{ pF}$

It is strongly recommended to use capacitors with the lowest temperature stability possible. In this practical example, a suitable part number could be:

Manufacturer: MURATA

PartNumber: GRM1885C1H270FA01D

Capacitance: 27 pF Tolerance: 1 %

Dielectric: C0G / NP0 (0 drift)

### 6.7 Power On Considerations

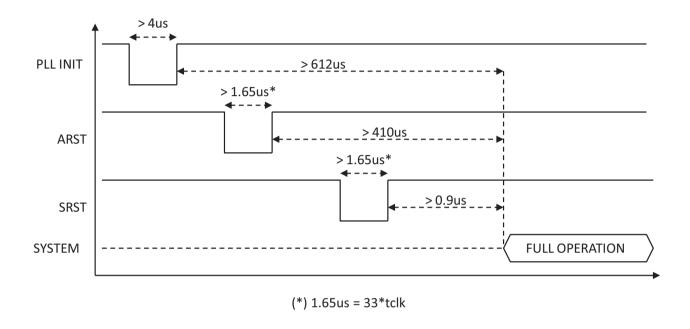

During power-on, PLL INIT pin should be tied to ground during 4  $\mu$ s at least, in order to ensure proper system start up. After releasing PLL INIT, the system will start no later than 612  $\mu$ s.

After power-up system can be restarted by means of low active pulse (min 1.65  $\mu$ s) in ARST or SRST. System full operation starts after 410  $\mu$ s (ARST pulse) or after 0.9  $\mu$ s (SRST pulse).

In case of simultaneous tie down of more than one initialization pin the longest time for operation must be respected.

Figure 6-6. Power On timing diagram

## 7. Mechanical Characteristics

### 7.1 LQFP80 Mechanical Characteristics

Figure 7-1. 80 LQFP package dimensions

CONTROL DIMENSIONS ARE IN MILLIMETERS.

| М    | ILLIMET                                                        | ER        |                                                                                                                                                                                                                                                                                                                                                                                                                              | INCH                   |                                                                                                                                                                                                                                                                                 |  |

|------|----------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MIN. | NOM.                                                           | MAX.      | MIN.                                                                                                                                                                                                                                                                                                                                                                                                                         | NOM.                   | MAX.                                                                                                                                                                                                                                                                            |  |

| _    | _                                                              | 1.60      | _                                                                                                                                                                                                                                                                                                                                                                                                                            | _                      | 0.063                                                                                                                                                                                                                                                                           |  |

| 0.05 | _                                                              | 0.15      | 0.002                                                                                                                                                                                                                                                                                                                                                                                                                        | _                      | 0.006                                                                                                                                                                                                                                                                           |  |

| 1.35 | 1.40                                                           | 1.45      | 0.053                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.055                  | 0.057                                                                                                                                                                                                                                                                           |  |

| 14   | 4.00 B                                                         | SC.       | 0.                                                                                                                                                                                                                                                                                                                                                                                                                           | 551 BS                 | SC.                                                                                                                                                                                                                                                                             |  |

| 1:   | 2.00 B                                                         | SC.       | 0.                                                                                                                                                                                                                                                                                                                                                                                                                           | 472 BS                 | SC.                                                                                                                                                                                                                                                                             |  |

| 14   | 4.00 B                                                         | SC.       | 0.                                                                                                                                                                                                                                                                                                                                                                                                                           | 551 BS                 | SC.                                                                                                                                                                                                                                                                             |  |

| 1:   | 2.00 B                                                         | SC.       | 0.472 BSC.                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                                                                                                                                                                                                                                                                 |  |

| 0.08 | _                                                              | 0.20      | 0.003                                                                                                                                                                                                                                                                                                                                                                                                                        | _                      | 0.008                                                                                                                                                                                                                                                                           |  |

| 0.08 | _                                                              | _         | 0.003                                                                                                                                                                                                                                                                                                                                                                                                                        | _                      | _                                                                                                                                                                                                                                                                               |  |

| 0.   | 3.5°                                                           | 7*        | 0.                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.5°                   | 7*                                                                                                                                                                                                                                                                              |  |

| 0,   | _                                                              | _         | 0,                                                                                                                                                                                                                                                                                                                                                                                                                           | _                      | _                                                                                                                                                                                                                                                                               |  |

| 11*  | 12°                                                            | 13°       | 11*                                                                                                                                                                                                                                                                                                                                                                                                                          | 12*                    | 13°                                                                                                                                                                                                                                                                             |  |

| 11*  | 12°                                                            | 13*       | 11"                                                                                                                                                                                                                                                                                                                                                                                                                          | 12°                    | 13°                                                                                                                                                                                                                                                                             |  |

| 0.09 | _                                                              | 0.20      | 0.004                                                                                                                                                                                                                                                                                                                                                                                                                        | _                      | 0.008                                                                                                                                                                                                                                                                           |  |

| 0.45 | 0.60                                                           | 0.75      | 0.018                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.024                  | 0.030                                                                                                                                                                                                                                                                           |  |

| 1    | .00 RE                                                         | F         | 0.039 REF                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                                                                                                                                                                                                                                                                                 |  |

| 0.20 |                                                                | _         | 0.008                                                                                                                                                                                                                                                                                                                                                                                                                        | _                      | _                                                                                                                                                                                                                                                                               |  |

|      | MIN. —  0.05 1.35 1. 1. 1. 0.08 0.08 0' 0' 11' 11' 0.09 0.45 1 | MIN. NOM. | —       1.60         0.05       —       0.15         1.35       1.40       1.45         12.00 BSC.       12.00 BSC.         12.00 BSC.       0.20         0.08       —       0.20         0.08       —       —         0'       3.5'       7'         0'       —       —         11'       12'       13'         11'       12'       13'         0.09       —       0.20         0.45       0.60       0.75         1.00 REF | MIN. NOM. MAX. MIN.  — | MIN. NOM. MAX. MIN. NOM.  — — 1.60 — —  0.05 — 0.15 0.002 —  1.35 1.40 1.45 0.053 0.055  14.00 BSC. 0.551 BS  12.00 BSC. 0.472 BS  14.00 BSC. 0.551 BS  12.00 BSC. 0.472 BS  0.08 — 0.20 0.003 —  0.08 — 0.20 0.003 —  0 3.5 7 0 3.5   0' — 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |  |

| 80L                             |            |      |       |            |       |       |

|---------------------------------|------------|------|-------|------------|-------|-------|

| SYMBOL                          | MILLIMETER |      | INCH  |            |       |       |

|                                 | MIN.       | NOM. | MAX.  | MIN.       | NOM.  | MAX.  |

| b                               | 0.17       | 0.20 | 0.27  | 0.007      | 0.008 | 0.011 |

| е                               | 0.50 BSC.  |      |       | 0.020 BSC. |       | SC.   |

| D2                              | 9.50       |      | 0.374 |            |       |       |

| E2                              | 9.50       |      | 0.374 |            |       |       |

| TOLERANCES OF FORM AND POSITION |            |      |       |            | Z     |       |

| aaa                             | 0.20       |      |       | 0.008      |       |       |

| bbb                             | 0.20       |      |       | 0.008      |       |       |

| ccc                             | 0.08       |      |       | 0.003      |       |       |

| ddd                             | 0.08       |      |       | 0.003      |       |       |

|                                 |            |      |       |            |       |       |

Table 7-1. LQFP Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

|-------------------------|--------|

Table 7-2. LQFP Package Characteristics

| Moisture Sensitivity Level | 3 |

|----------------------------|---|

|----------------------------|---|

This package respects the recommendations of the NEMI User Group.

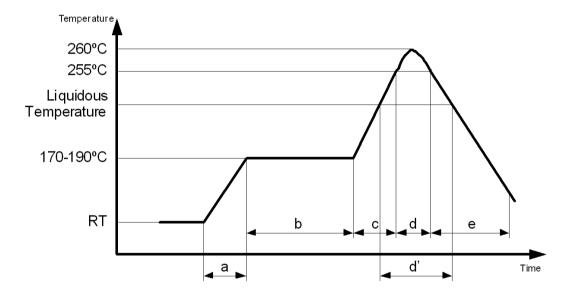

## 8. Recommended mounting conditions

### 8.1 Conditions of Standard Reflow

Table 8-1. Recommended mounting conditions of Standard Reflow

| Items                | Contents                                                                  |                                                                                                                                       |  |

|----------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Method               | IR (Infrared Reflow) / Convection                                         |                                                                                                                                       |  |

| Times                | 2                                                                         |                                                                                                                                       |  |

|                      | Before unpacking                                                          | Please use within 2 years after production                                                                                            |  |

|                      | From unpacking to second reflow                                           | Within 8 days                                                                                                                         |  |

| Floor Life           | In case over period of floor life                                         | Baking with 125°C +/- 3°C for 24hrs +2hrs/-0hrs is required. Then please use within 8 days (please remember baking is up to 2 times). |  |

| Floor Life Condition | Between 5°C and 30°C and also belo humidity in the required temp. range). | ow 70% RH required. (It is preferred lower                                                                                            |  |

Figure 8-1. LQFP80 package soldering profile

Note: H rank: 260°C Max

a: Average ramp-up rate: 1°C/s to 4°C/s

**b:** Preheat & Soak: 170°C to 190°C, 60s to 180s

**c:** Average ramp-up rate: 1°C/s to 4°C/s

**d:** Peak temperature: 260°C Max, up to 255°C within 10s

**d':** Liquidous temperature: Up to 230°C within 40s or

Up to 225°C within 60s or

Up to 220°C within 80s

e: Cooling: Natural cooling or forced cooling

## 8.2 Manual Soldering

Table 8-2. Recommended mounting conditions of Manual Soldering

| Items                | Contents                                                                    |                                                                                                             |  |  |

|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Floor life           | Before unpacking                                                            | Please use within 2 years after production                                                                  |  |  |

|                      | From unpacking to Manual Soldering                                          | Within 2 years after production (No control required for moisture adsorption because it is partial heating) |  |  |

| Floor life condition | Between 5°C and 30°C and also below humidity in the required temp. range).  | 70% RH required. (It is preferred lower                                                                     |  |  |

| Solder Condition     | Temperature of soldering iron: Max *Be careful for touching package body wi | 400°C, Time: Within 5 seconds/pin. th iron.                                                                 |  |  |

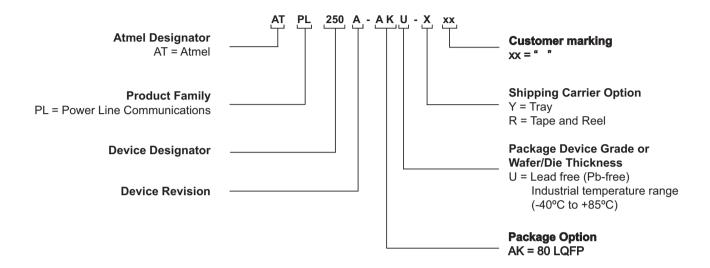

## 9. Ordering Information

Table 9-1. Ordering Information

| Atmel Ordering Code | Package | Package Type | Temperature Range          |

|---------------------|---------|--------------|----------------------------|

| ATPL250A-AKU-Y      | 80 LQFP | Pb-Free      | Industrial (-40°C to 85°C) |

| ATPL250A-AKU-R      | 80 LQFP | Pb-Free      | Industrial (-40°C to 85°C) |

# 10. Revision History

In the table that follows, the most recent version of the document appears first.

| Doc. Rev.<br>43079 | Comments                                                                                                                | Change<br>Request<br>Ref. |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|

| F                  | Figure 5-3 and Figure 5-5: updated.                                                                                     |                           |

| E                  | Section 5.3 "Zero-crossing detector": updated.                                                                          |                           |

| D                  | Format changes according to new templates.                                                                              |                           |

| С                  | Section 6.6 "Oscillator" updated: modified Figure 6-5, added equation and information after the figure.                 |                           |

|                    | Table 6-7 updated: added the values of $C_{\text{XTAL}}$ and $C_{\text{PARA24M}}$ . Modified the notes below the table. |                           |

|                    | Chapters order redefined.                                                                                               |                           |

|                    | Modified Section 1.1 "ATPL250A Application Block Diagram" (was Section 8. "Application information").                   |                           |

| В                  | Figure 1-1 updated: RST and CLKOUT signals introduced.                                                                  |                           |

|                    | Table 6-6 updated the values of Power Consumption and Power Consumption (worst case).                                   |                           |

|                    | Modified Section 5. "Analog Front-End" (was "PLC coupling circuitry description").                                      |                           |

|                    | Deleted Section "Power Considerations": the information of this section is in Section 3. "Signal Description".          |                           |

| Α                  | First Issue.                                                                                                            |                           |

## **Table of Contents**

| De  | cription                                                                                                                                                                                                   | 1                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.  | Features                                                                                                                                                                                                   |                            |

| 2.  | Block Diagram                                                                                                                                                                                              | 3                          |

| 3.  | Signal Description                                                                                                                                                                                         | 4                          |

| 4.  | Package and Pinout       4.1       80-Lead LQFP Package Outline.         4.2       80-Lead LQFP Pinout.                                                                                                    | . 6                        |

| 5.  | Analog Front-End                                                                                                                                                                                           | . 7<br>. 9                 |

| 6.  | Electrical characteristics 6.1 Absolute Maximum Ratings 6.2 Recommended Operating Conditions 6.3 Electrical Pinout 6.4 DC Characteristics 6.5 Power Consumption 6.6 Oscillator 6.7 Power On Considerations | 13<br>14<br>15<br>16<br>19 |

| 7.  | Mechanical Characteristics                                                                                                                                                                                 |                            |

|     | Recommended mounting conditions  8.1 Conditions of Standard Reflow  8.2 Manual Soldering                                                                                                                   | 23<br>24                   |

|     | Ordering Information                                                                                                                                                                                       |                            |

| Tal | le of Contents                                                                                                                                                                                             | 27                         |

© 2016 Atmel Corporation. / Rev.: Atmel-43079F-ATPL250A-Datasheet 22-Sep-16

1600 Technology Drive, San Jose, CA 95110 USA

F: (+1)(408) 436.4200

www.atmel.com

**Atmel Corporation**

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

**T**: (+1)(408) 441.0311

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.