# Intelligent Digital Amplifier PWM Controller and Audio Processor

# D2-45057, D2-45157

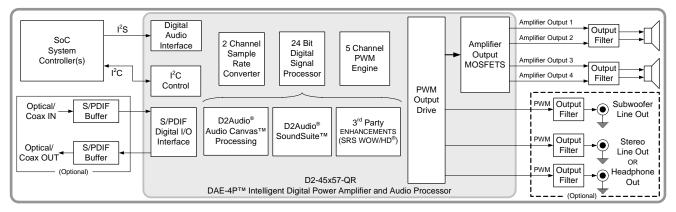

The D2-45057 and D2-45157 devices are complete System-on-Chip (SoC) Class-D digital audio amplifiers. Combining high performance integrated Power Stages along with an optimized Audio Processor feature set and PWM Controller, these devices offer a complete, powerful, and very cost effective audio solution for high volume and cost-critical products.

This 4th generation Digital Audio Engine (DAE-4P)<sup>™</sup> device combines extensive integrated Digital Signal Processor (DSP) audio processing with amplifier control, for a complete audio solution. Its ease of integration into the existing system processor provides complete support for all system product and amplifier functions.

The four configurable Power Stages operate as four separate Half-Bridge outputs, as two Full-Bridge outputs, or in combinations of Half-Bridge plus Full-Bridge, providing flexible loudspeaker drive solutions. Separate PWM outputs provide additional combinations to drive headphone, or line level stereo and subwoofer outputs.

# **Related Literature**

- DAE-4/DAE-4P Register API Specification

- DAE-4P Evaluation Kit Guides

### **Features**

- All Digital Class-D Amplifier and Controller with Integrated Digital Signal Processing (DSP)

- Four Integrated Power Stages Supporting

- 2 Channels, Bridged

- 4 Channels, Half-Bridge

- 2 Channels, Half-Bridge, plus 1 Channel Bridged

- Output Power (Bridged)

- 25W (8Ω, <1% THD); 30W (8Ω, <10% THD)

- Fully Programmable Digital Signal Processing (DSP)

- Up to 5 Programmable Audio Signal Path Channels

- Programmable Equalizers, Filters, Mixers, Limiters

- Includes D2Audio<sup>™</sup> SoundSuite<sup>™</sup> and SRS WOW/HD<sup>™</sup> Audio Enhancement Algorithms

- I<sup>2</sup>S and S/PDIF<sup>™</sup> Digital Audio Inputs

- Asynchronous Sample Rate Converters; Sample Rates from 32kHz up to 192kHz

- Wide 9V to 26V Power Stage HV Supply Range, plus Internally-Generated Gate Drive Supply

- Temperature and Undervoltage Monitoring and Individual Channel Protection

### **Applications**

- PC/Multimedia Speakers

- Digital TV Audio Systems

- Portable Device Docking Stations

- Powered Speaker Systems

# **Typical System Implementation**

SYSTEM APPLICATION IMPLEMENTING 2X FULL-BRIDGE LOUDSPEAKER OUTPUTS PLUS 3 LINE-LEVEL OUTPUTS

1

# **Ordering Information**

| PART<br>NUMBER<br>(Notes 3, 4) | PART<br>MARKING | AUDIO PROCESSING<br>FEATURE SET SUPPORT<br>(Note 1) | TEMP.<br>RANGE (°C) | PACKAGE<br>(Pb-Free)                 | PKG.<br>DWG. # |

|--------------------------------|-----------------|-----------------------------------------------------|---------------------|--------------------------------------|----------------|

| D2-45057-QR                    | D2-45057-QR     | D2Audio <sup>™</sup> SoundSuite <sup>™</sup>        | -10 to +85          | 68 Ld QFN                            | L68.10x10C     |

| D2-45057-QR-T (Note 2)         | D2-45057-QR     | D2Audio™ SoundSuite™                                | -10 to +85          | 68 Ld QFN<br>(1k pcs.) Tape and Reel | L68.10x10C     |

| D2-45157-QR                    | D2-45157-QR     | SRS WOW/HD™                                         | -10 to +85          | 68 Ld QFN                            | L68.10x10C     |

| D2-45157-QR-T (Note 2)         | D2-45157-QR     | SRS WOW/HD™                                         | -10 to +85          | 68 Ld QFN<br>(1k pcs.) Tape and Reel | L68.10x10C     |

NOTES:

1. The D2-45057, D2-45157 support audio processing algorithms for the D2Audio<sup>™</sup> SoundSuite<sup>™</sup>, and SRS WOW/HD<sup>™</sup> audio enhancement features. Algorithm support of these enhancements is device-dependent. Refer to specific part number for desired feature support.

- 2. Please refer to  $\underline{TB347}$  for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for <u>D2-45057, D2-45157</u>. For more information on MSL please see techbrief <u>TB363</u>.

# **Table of Contents**

| Ordering Information                                                                                                                                          | 2                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Absolute Maximum Ratings                                                                                                                                      | 4                                                              |

| Thermal Information                                                                                                                                           | 4                                                              |

| Recommended Operating Conditions                                                                                                                              | 4                                                              |

| Electrical Specifications                                                                                                                                     | 4                                                              |

| Performance Specifications                                                                                                                                    | 6                                                              |

| Serial Audio Interface Port Timing                                                                                                                            | 6                                                              |

| Two-Wire (I <sup>2</sup> C) Interface Port Timing                                                                                                             | 7                                                              |

| SPI™ Master Mode Interface Port Timing                                                                                                                        | 8                                                              |

| SPI™ Slave Mode Interface Port Timing                                                                                                                         | 8                                                              |

| Pin Configuration                                                                                                                                             |                                                                |

| Pin Description                                                                                                                                               | 10                                                             |

|                                                                                                                                                               |                                                                |

| Typical Performance Characteristics                                                                                                                           | 14                                                             |

| Typical Performance Characteristics         Test Considerations         Full-Bridge Typical Performance Curves         Half-Bridge Typical Performance Curves | 14<br>14                                                       |

| Test Considerations<br>Full-Bridge Typical Performance Curves                                                                                                 | 14<br>14<br>15                                                 |

| Test Considerations<br>Full-Bridge Typical Performance Curves<br>Half-Bridge Typical Performance Curves                                                       | 14<br>15<br>17<br>17<br>17<br>17<br>17<br>17<br>18<br>18<br>18 |

| Control and Operation                                                                                                                                                                                          | 19                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

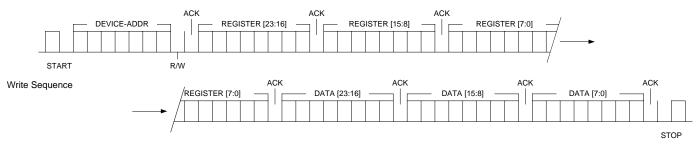

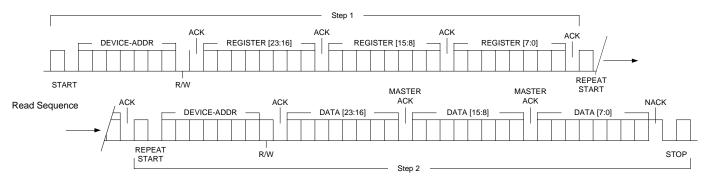

| Control Register Summary<br>I <sup>2</sup> C 2-Wire Control Interface<br>Reading and Writing Control Registers<br>Control Interface Address Spaces                                                             | 19<br>19                         |

| Storing Parameters to EEPROM<br>Serial Peripheral Interface (SPI)<br>Reset and Device Initialization<br>Boot Modes                                                                                             | 20<br>20<br>20                   |

| Power Supply Requirements                                                                                                                                                                                      | 21                               |

| High-Side Gate Drive Voltage<br>Power Supply Synchronization<br>Power Sequence Requirements<br>REG5V                                                                                                           | 21<br>21<br>22                   |

| Pin and Control Block Functions                                                                                                                                                                                | 22                               |

| I/O Control Pins<br>nPDN Input Pin<br>nERROR[0-3] Output Pins<br>IREF Pin<br>Configuration Assignment Pin Differences<br>OCFG0, OCFG1 Input Pins<br>nERROR/CFG0 and PSSYNC/CFG1 Pins<br>Temperature Monitoring | 22<br>22<br>22<br>22<br>23<br>23 |

| Configuration Setting                                                                                                                                                                                          | 24                               |

| Protection                                                                                                                                                                                                     | 26                               |

| Error Reporting<br>Short-Circuit and Overcurrent Sensing<br>Protection Monitoring and Control<br>Thermal Protection and Monitors<br>Graceful Overcurrent and Short Circuit<br>Power Supply Voltage Monitoring  | 26<br>26<br>26<br>27             |

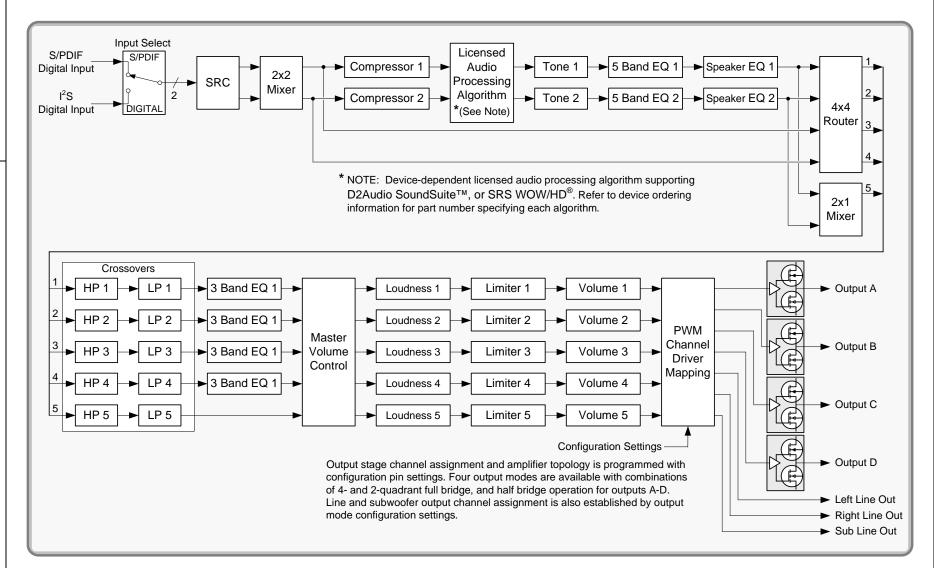

| Audio Processing                                                                                                                                                                                               | 27                               |

| Audio Processing Signal Flow Blocks                                                                                                                                                                            | 27                               |

| Revision History                                                                                                                                                                                               | 30                               |

| Products                                                                                                                                                                                                       | 30                               |

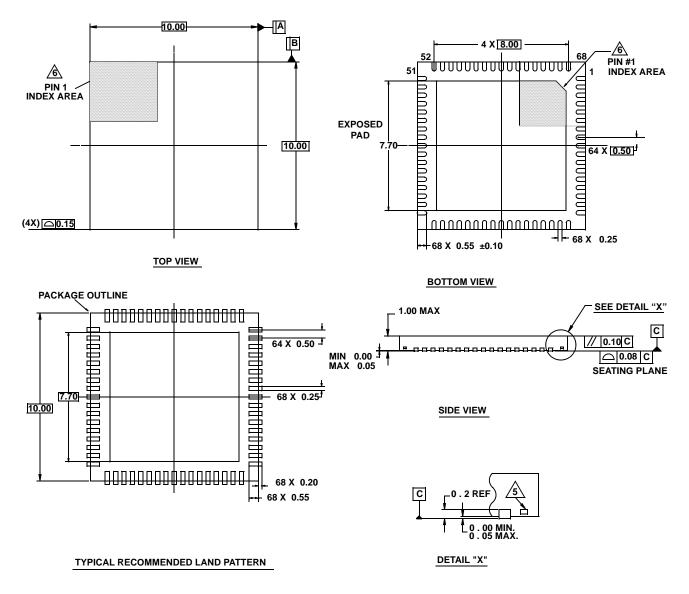

| Package Outline Drawing                                                                                                                                                                                        | 31                               |

#### **Absolute Maximum Ratings**

| Supply Voltage                      |

|-------------------------------------|

| HVDD[A:D], VDDHV                    |

| RVDD, PWMVDD                        |

| CVDD, PLLVDD                        |

| Input Voltage                       |

| Any Input but XTALI                 |

| XTALI                               |

| Input Current, Any Pin but Supplies |

#### **Thermal Information**

| Thermal Resistance (Typical)     | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|----------------------------------|------------------------|------------------------|

| 68 Ld QFN Package (Notes 5, 6)   | 25                     | 1                      |

| Maximum Storage Temperature      |                        | C to +150°C            |

| Pb-Free Reflow Profile           | Se                     | ee link below          |

| http://www.intersil.com/pbfree/F | b-FreeReflow.          | <u>asp</u>             |

#### **Recommended Operating Conditions**

| Temperature Range10°C to +85°C                                             |

|----------------------------------------------------------------------------|

| High Voltage Supply Voltage,                                               |

| HVDD[A:D], VDDHV                                                           |

| Digital I/O Supply Voltage, PWMVDD                                         |

| Core Supply Voltage, CVDD 1.8V                                             |

| Analog Supply Voltage, PLLVDD 1.8V                                         |

| Minimum Load Impedance (HVDD[A:D] $\leq$ 24.0V), Z <sub>L</sub> 4 $\Omega$ |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 5.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 7. Absolute Maximum parameters are not tested in production.

**Electrical Specifications**  $T_A = +25$ °C, HVDD[A:D]/VDDHV = 24V, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic.

| PARAMETER                                                                            | TEST<br>CONDITIONS              | SYMBOL           | MIN        | ТҮР  | мах    | UNIT |

|--------------------------------------------------------------------------------------|---------------------------------|------------------|------------|------|--------|------|

| Digital Input High Logic Level (Note 8)                                              |                                 | V <sub>IH</sub>  | 2          | -    | -      | V    |

| Digital Input Low Logic Level (Note 8)                                               |                                 | $V_{IL}$         | -          | -    | 0.8    | V    |

| High Level Output Drive Voltage<br>(I <sub>OUT</sub> at -Pin Drive Strength Current) |                                 | V <sub>OH</sub>  | RVDD - 0.4 | -    | -      | V    |

| Low Level Output Drive Voltage<br>(I <sub>OUT</sub> at +Pin Drive Strength Current)  |                                 | V <sub>OL</sub>  | -          | -    | 0.4    | V    |

| High Level Input Drive Voltage XTALI Pin                                             |                                 | $V_{\text{IHX}}$ | 0.7        | -    | PLLVDD | V    |

| Low Level Input Drive Voltage XTALI Pin                                              |                                 | V <sub>ILX</sub> | -          | -    | 0.3    | V    |

| Input Leakage Current (Note 9)                                                       |                                 | I <sub>IN</sub>  | -          | -    | ±10    | μA   |

| Input Capacitance                                                                    |                                 | Cin              | -          | 9    | -      | pF   |

| Output Capacitance                                                                   | All Outputs Except<br>OUT[A:D]  | Cout             | -          | 9    | -      | pF   |

|                                                                                      | OUT[A:D]                        |                  | -          | 190  | -      | pF   |

| nRESET Pulse Width                                                                   |                                 | t <sub>RST</sub> | -          | 10   | -      | ns   |

| Internal Pull-Up Resistance to PWMVDD<br>(for nERROR0-3, OCFG, nPDN)                 |                                 | -                | -          | 100  | -      | kΩ   |

| Digital I/O Supply Pin Voltage, Current                                              |                                 | RVDD             | 3          | 3.3  | 3.6    | V    |

|                                                                                      | Active Current                  | and<br>PWMVDD    | -          | 10   | -      | mA   |

|                                                                                      | Power-Down Current              |                  | -          | 0.01 | -      | mA   |

| Core Supply Pins                                                                     |                                 | CVDD             | 1.7        | 1.8  | 1.9    | V    |

|                                                                                      | Active Current                  | 1                | -          | 300  | -      | mA   |

|                                                                                      | Power-Down Current<br>(Note 10) |                  | -          | 6    | -      | mA   |

4

## D2-45057, D2-45157

**Electrical Specifications**  $T_A = +25$ °C, HVDD[A:D]/VDDHV = 24V, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic. (Continued)

| PARAMETER                                                                                        | TEST<br>CONDITIONS              | SYMBOL             | MIN  | ТҮР     | МАХ | UNIT |

|--------------------------------------------------------------------------------------------------|---------------------------------|--------------------|------|---------|-----|------|

| Analog Supply Pins (PLL)                                                                         |                                 | PLLVDD             | 1.7  | 1.8     | 1.9 | V    |

|                                                                                                  | Active Current                  |                    | -    | 10      | -   | mA   |

|                                                                                                  | Power-Down Current<br>(Note 10) |                    | -    | 5       | -   | mA   |

| CRYSTAL OSCILLATOR                                                                               |                                 |                    |      |         |     |      |

| Crystal Frequency (Fundamental Mode Crystal)                                                     |                                 | Хо                 | 20   | 24.576  | 25  | MHz  |

| Duty Cycle                                                                                       |                                 | Dt                 | 40   | -       | 60  | %    |

| Start-up Time (Start-up Time is Oscillator Enabled<br>(with Valid Supply) to Stable Oscillation) |                                 | t <sub>START</sub> | -    | 5       | 20  | ms   |

| PLL                                                                                              |                                 |                    |      |         |     |      |

| VCO Frequency                                                                                    |                                 | F <sub>VCO</sub>   | 240  | 294.912 | 300 | MHz  |

| PLL Lock Time from any Input Change                                                              |                                 |                    | -    | 3       | -   | ms   |

| 1.8V POWER-ON RESET                                                                              |                                 |                    |      |         |     |      |

| Reset Enabled Voltage Level                                                                      |                                 | V <sub>EN</sub>    | 0.95 | 1.1     | 1.3 | V    |

| POR Minimum Output Pulse Width                                                                   |                                 | t <sub>DIS</sub>   | -    | 5       | -   | μs   |

| 1.8V BROWNOUT DETECTION                                                                          |                                 |                    |      |         |     |      |

| Detect Level                                                                                     |                                 |                    | 1.4  | 1.5     | 1.7 | V    |

| Pulse Width Rejection                                                                            |                                 | t <sub>BOD1</sub>  | -    | 100     | -   | ns   |

| Minimum Output Pulse Width                                                                       |                                 | t <sub>O1</sub>    | -    | 20      | -   | ns   |

| 3.3V (PWMVDD) BROWNOUT DETECTION                                                                 |                                 |                    |      |         |     |      |

| Detect Level                                                                                     |                                 |                    | 2.5  | 2.7     | 2.9 | V    |

| Pulse Width Rejection                                                                            |                                 | t <sub>BOD3</sub>  | -    | 100     | -   | ns   |

| Minimum Output Pulse Width                                                                       |                                 | t <sub>O3</sub>    | -    | 20      | -   | ns   |

| GATE DRIVE INTERNAL +5V BROWN-OUT DETECT                                                         | ION                             |                    |      |         |     |      |

| Gate Drive Supply Undervoltage Threshold                                                         |                                 |                    | -    | 4.5     | -   | V    |

| Gate Drive Supply Undervoltage Threshold Hysteresis                                              |                                 |                    | -    | 200     | -   | mV   |

| Gate Drive Supply Undervoltage Threshold Glitch<br>Rejection                                     |                                 |                    | -    | 50      | -   | ns   |

| PROTECTION DETECT                                                                                |                                 |                    |      |         |     |      |

| High Voltage (+VDDHV) Undervoltage Protection                                                    |                                 |                    | -    | 7       | 9   | V    |

| Overcurrent Trip Threshold                                                                       |                                 |                    | -    | 4       | -   | А    |

| Overcurrent De-glitch                                                                            |                                 |                    | -    | 2.5     | -   | ns   |

| Short-Circuit Current Limit (Peak)                                                               |                                 |                    | -    | 8       | -   | А    |

| Overcurrent Response Time                                                                        |                                 |                    | -    | 20      | -   | ns   |

| Thermal Shut-Down (Power Stages)                                                                 |                                 |                    | -    | 140     | -   | °C   |

| Thermal Shut-Down Hysteresis (Power Stages)                                                      |                                 |                    | -    | 30      | -   | °C   |

NOTES:

8. All input pins except XTALI.

9. Input leakage applies to all pins except XTALO.

10. Power-down is with device in reset and clocks stopped.

**Performance Specifications**  $T_A = +25^{\circ}C$ , HVDD[A:D]/VDDHV = 24V, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic.

| PARAMETER                                                 | SYMBOL              | MIN | ТҮР  | MAX | UNIT |

|-----------------------------------------------------------|---------------------|-----|------|-----|------|

| r <sub>DS(ON)</sub> (Maximum, MOSFETs @ +25°C)            | r <sub>DS(ON)</sub> | -   | 200  | -   | mΩ   |

| r <sub>DS(ON)</sub> Mismatch                              |                     | -   | 1    | -   | %    |

| PWM Switching Rate                                        |                     | -   | 384  | -   | kHz  |

| nPDN Input Off Delay                                      | t <sub>PDNOFF</sub> | -   | 1.4  | -   | ms   |

| nPDN Input On Delay                                       | t <sub>PDNON</sub>  | -   | 1.4  | -   | ms   |

| POWER OUTPUT                                              |                     |     |      |     |      |

| <1% THD, Bridged, Load = $8\Omega$ , HVDD[A:D] = 24V      | POUT                | -   | 25   | -   | W    |

| <10% THD, Bridged, Load = $8\Omega$ , HVDD[A:D] = 24V     | POUT                | -   | 30   | -   | W    |

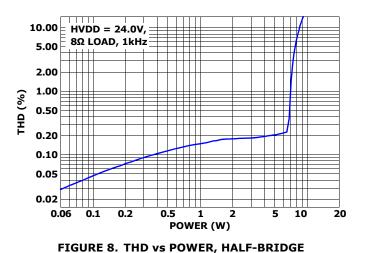

| <1% THD, Half-Bridge, Load = $8\Omega$ , HVDD[A:D] = 24V  | POUT                | -   | 7    | -   | W    |

| <10% THD, Half-Bridge, Load = $8\Omega$ , HVDD[A:D] = 24V | POUT                | -   | 9    | -   | W    |

| THD+N                                                     | I                   |     | 4    | 1   |      |

| Load = $8\Omega$ , Power = 25W, Bridged, 1kHz             | THD+N               | -   | 0.3  | -   | %    |

| Load = $8\Omega$ , Power = 1W, Bridged, 1kHz              |                     | -   | 0.05 | -   | %    |

| SNR                                                       | SNR                 | -   | 110  | -   | dB   |

| Efficiency (Power Stage, Load = $8\Omega$ )               |                     | -   | 90   | -   | %    |

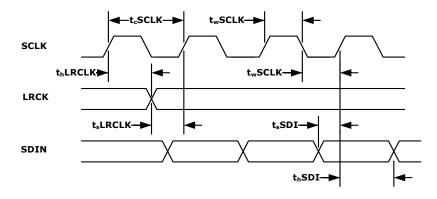

**Serial Audio Interface Port Timing**  $T_A = +25^{\circ}C$ , HVDD[A:D]/VDDHV = 24V, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground. PLL at 294.912MHz, OSC at 24.576MHz, core running at 147.456MHz with typical audio data traffic.

| SYMBOL               | DESCRIPTION                              | MIN | ТҮР | MAX  | UNIT |

|----------------------|------------------------------------------|-----|-----|------|------|

| t <sub>c</sub> SCLK  | SCLK Frequency - (SCLK)                  | -   | -   | 12.5 | MHz  |

| t <sub>w</sub> SCLK  | SCLK Pulse Width (high and low) - (SCLK) | 40  | -   | -    | ns   |

| t <sub>s</sub> LRCLK | LRCKR Setup to SCLK Rising - (LRCK)      | 20  | -   | -    | ns   |

| t <sub>h</sub> LRCLK | LRCKR Hold from SCLK Rising - (LRCK)     | 20  | -   | -    | ns   |

| t <sub>s</sub> SDI   | SDIN Setup to SCLK Rising - (SDIN)       | 20  | -   | -    | ns   |

| t <sub>h</sub> SDI   | SDIN Hold from SCLK Rising - (SDIN)      | 20  | -   | -    | ns   |

#### FIGURE 1. SERIAL AUDIO INTERFACE PORT TIMING

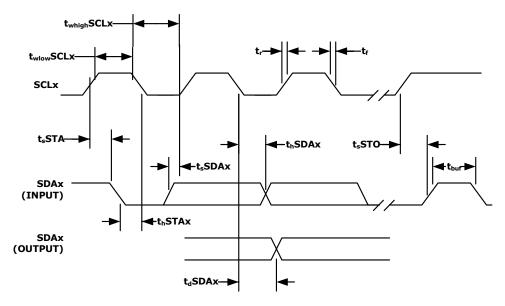

| SYMBOL                  | DESCRIPTION                             | MIN         | MAX | UNIT    |

|-------------------------|-----------------------------------------|-------------|-----|---------|

| f <sub>SCL</sub>        | SCL Frequency                           | -           | 100 | kHz     |

| t <sub>buf</sub>        | Bus Free Time Between Transmissions     | 4.7         | -   | μs      |

| t <sub>wlow</sub> SCLx  | SCL Clock Low                           | 4.7         | -   | μs      |

| t <sub>whigh</sub> SCLx | SCL Clock High                          | 4.0         | -   | μs      |

| t <sub>s</sub> STA      | Setup Time For a (Repeated) Start       | 4.7         | -   | μs      |

| t <sub>h</sub> STA      | Start Condition Hold Time               | 4.0         | -   | μs      |

| t <sub>h</sub> SDAx     | SDA Hold From SCL Falling (Note 11)     | 1 (typical) |     | sys clk |

| t <sub>s</sub> SDAx     | SDA Setup Time to SCL Rising            | 250         | -   | ns      |

| t <sub>d</sub> SDAx     | SDA Output Delay Time From SCL Falling  | -           | 3.5 | μs      |

| t <sub>r</sub>          | Rise Time of Both SDA and SCL (Note 12) | -           | 1   | μs      |

| t <sub>f</sub>          | Fall Time of Both SDA and SCL (Note 12) | -           | 300 | ns      |

| t <sub>s</sub> STO      | Setup Time For a Stop Condition         | 4.7         | -   | μs      |

**Two-Wire (I<sup>2</sup>C) Interface Port Timing**  $T_A = +25$ °C, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

NOTES:

11. Data is clocked in as valid on next XTALI rising edge after SCL goes low.

12. Limits established by characterization and not production tested.

FIGURE 2. I<sup>2</sup>C INTERFACE TIMING

### D2-45057, D2-45157

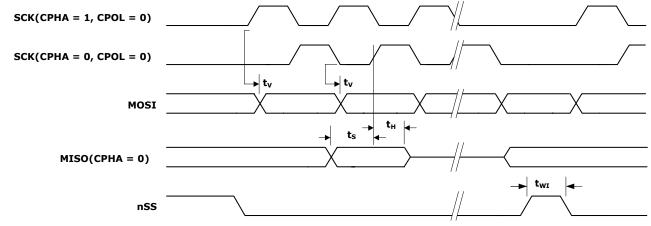

**SPI<sup>TM</sup> Master Mode Interface Port Timing**  $T_A = +25$ °C, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL          | DESCRIPTION                | MIN                   | MAX | UNIT |

|-----------------|----------------------------|-----------------------|-----|------|

| t <sub>V</sub>  | MOSI Valid From Clock Edge | -                     | 8   | ns   |

| t <sub>S</sub>  | MISO Setup to Clock Edge   | 10                    | -   | ns   |

| t <sub>H</sub>  | MISO Hold From Clock Edge  | 1 system clock + 2ns  |     |      |

| t <sub>WI</sub> | nSS Minimum Width          | 3 system clocks + 2ns |     |      |

**SPI<sup>TM</sup> Slave Mode Interface Port Timing**  $T_A = +25$ °C, CVDD = PLLVDD = 1.8V ±5%, RVDD = PWMVDD = 3.3V ±10%. All grounds at 0.0V. All voltages referenced to ground.

| SYMBOL          | DESCRIPTION                | MIN                   | MAX                  | UNIT |  |  |  |

|-----------------|----------------------------|-----------------------|----------------------|------|--|--|--|

| t <sub>V</sub>  | MISO Valid From Clock Edge | 3 system clocks + 2ns |                      |      |  |  |  |

| ts              | MOSI Setup to Clock Edge   | 10                    | -                    | ns   |  |  |  |

| t <sub>H</sub>  | MOSI Hold From Clock Edge  | 1 s                   | 1 system clock + 2ns |      |  |  |  |

| t <sub>WI</sub> | 3 sy                       | ystem clocks +        | 2ns                  |      |  |  |  |

FIGURE 3. SPI TIMING

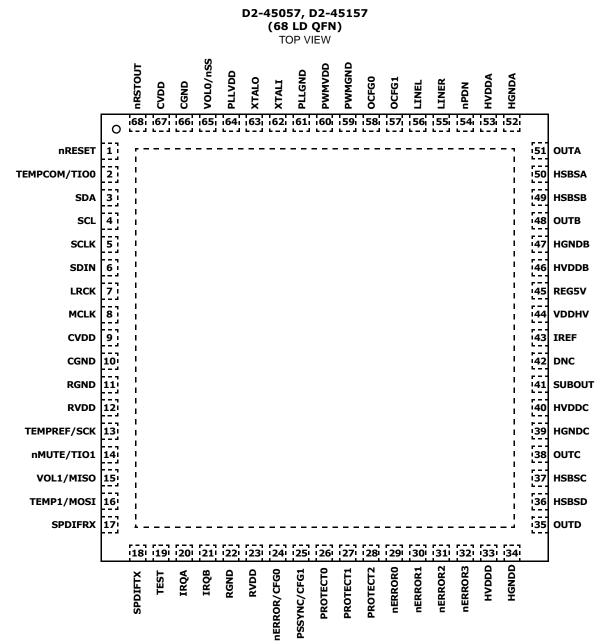

# **Pin Configuration**

# **Pin Description**

| PIN | PIN<br>NAME<br>(Note 13) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----|--------------------------|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | nRESET                   | I    | 3.3                     | Active low reset input with hysteresis. Low level activates system level reset, initializing all internal logic and program operations. System latches boot mode selection on the IRQ input pins on the rising edge.                                                                                                                                                                    |  |  |  |

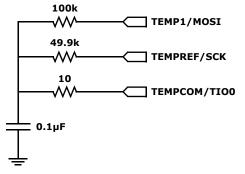

| 2   | TEMPCOM/<br>TIO0         | I/O  | 3.3                     | Board temperature monitor common I/O pin. When operating as output, provides 16mA drive strength.                                                                                                                                                                                                                                                                                       |  |  |  |

| 3   | SDA                      | I/O  | 3.3                     | Two-Wire Serial data port, open drain driver with 8mA drive strength. Bidirectional signal used by both the master and slave controllers for data transport. Pin floats on reset.                                                                                                                                                                                                       |  |  |  |

| 4   | SCL                      | I/O  | 3.3                     | Two-Wire Serial clock port, open drain driver with 8mA drive strength. Bidirectional signal is used by both the master and slave controllers for clock signaling. Pin floats on reset.                                                                                                                                                                                                  |  |  |  |

| 5   | SCLK                     | Ι    | 3.3                     | I <sup>2</sup> S Serial Audio Bit Clock (SCLK) Input. Input has hysteresis.                                                                                                                                                                                                                                                                                                             |  |  |  |

| 6   | SDIN                     | Ι    | 3.3                     | I <sup>2</sup> S Serial Audio Data (SDIN) Input. Input has hysteresis.                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 7   | LRCK                     | Ι    | 3.3                     | I <sup>2</sup> S Serial Audio Left/Right (LRCK) Input. Input has hysteresis.                                                                                                                                                                                                                                                                                                            |  |  |  |

| 8   | MCLK                     | 0    | 3.3                     | $\rm I^2S$ Serial Audio Master Clock output for external ADC/DAC components, drives low on reset. Output is an 8mA driver.                                                                                                                                                                                                                                                              |  |  |  |

| 9   | CVDD                     | Р    | 3.3                     | Core power, +1.8VDC. Used in the chip internal DSP, logic and interfaces.                                                                                                                                                                                                                                                                                                               |  |  |  |

| 10  | CGND                     | GND  | 3.3                     | Core ground.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 11  | RGND                     | GND  | 3.3                     | Digital pad ring ground. Internally connected to PWMGND.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 12  | RVDD                     | Р    | 3.3                     | Digital pad ring power, 3.3V. This 3.3V supply is used for all the digital I/O pad drivers and receivers, except for the analog pads. There are 2 of these pins and both are required to be connected. Internally connected to PWMVDD.                                                                                                                                                  |  |  |  |

| 13  | TEMPREF/<br>SCK          | I/O  | 3.3                     | Reference pin for temperature monitor and SPI clock. At de-assertion of device reset, pin operates as SPI clock with 8mA drive strength. Upon internal D2-45057, D2-45157 firmware execution, pin becomes temperature monitor reference.                                                                                                                                                |  |  |  |

| 14  | nMUTE/<br>TIO1           | 0    | 3.3                     | Mute signal output. Low active: mute condition drives pin low. Output is a 16mA driver.<br>Initializes as input on reset, then becomes output upon internal firmware execution.                                                                                                                                                                                                         |  |  |  |

| 15  | VOL1/<br>MISO            | I/O  | 3.3                     | Volume control pulse input and SPI master- input/slave-output data signal. At de-assertion of device reset, pin operates as SPI master input or slave output. (When operating as output, provides 4mA drive strength.) Then upon internal D2-45057, D2-45157 firmware execution, pin becomes input for monitoring up/down phase pulses from volume control. (1 of 2 volume input pins.) |  |  |  |

| 16  | TEMP1/<br>MOSI           | I/O  | 3.3                     | Board temperature monitor pin, and SPI master-output/slave-input data signal. At de-<br>assertion of device reset, pin operates as SPI master output or slave input. (When operating<br>as output, provides 4mA drive strength.) Then upon internal D2-45057, D2-45157 firmware<br>execution, pin becomes input for monitoring board temperature.                                       |  |  |  |

| 17  | SPDIFRX                  | Ι    | 3.3                     | S/PDIF Digital audio data input                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 18  | SPDIFTX                  | 0    | 3.3                     | S/PDIF Digital audio data output This pin is the S/PDIF audio output and drives a 8mA, 3.3V stereo output up to 192kHz. Pin floats on reset.                                                                                                                                                                                                                                            |  |  |  |

| 19  | TEST                     | Ι    | 3.3                     | Hardware test mode control. For factory use only. Must be tied low.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 20  | IRQA                     | Ι    | 3.3                     | Interrupt request port A. One of 2 IRQ pins, tied to logic (3.3V) high or to ground. High/low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle.                                                                                                                                                                                                   |  |  |  |

| 21  | IRQB                     | Ι    | 3.3                     | Interrupt request port B. One of 2 IRQ pins, tied to logic (3.3V) high or to ground. High/low logic status establishes boot mode selection upon de-assertion of reset (nRESET) cycle.                                                                                                                                                                                                   |  |  |  |

| 22  | RGND                     | GND  | 3.3                     | Digital pad ring ground. Internally connected to PWMGND.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 23  | RVDD                     | Р    | 3.3                     | Digital pad ring power, 3.3V. This 3.3V supply is used for all the digital I/O pad drivers and receivers, except for the analog pads. There are 2 of these pins and both are required to be connected. Internally connected to PWMVDD.                                                                                                                                                  |  |  |  |

10

# Pin Description (Continued)

| PIN | PIN<br>NAME<br>(Note 13) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------------|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | nERROR/<br>CFG0          | I/O  | 3.3                     | Output configuration selection input, and nERROR output. Upon device reset, pin operates as input, using application-installed pull-up or pull-down connection to pin to specify one of 4 amplifier configurations. Upon internal D2-45057, D2-45157 firmware execution, pin becomes output, providing active-low output drive when amplifier protection monitoring detects an error condition. When operating as output, provides 4mA drive strength. (Note: This pin may also be referenced as "PSCURR" on some reference designs. Function is identical regardless of name.) |

| 25  | PSSYNC/<br>CFG1          | I/O  | 3.3                     | Output configuration selection input, and power supply sync output. Upon device reset, pin operates as input, using application-installed pull-up or pull-down connection to pin to specify one of 4 amplifier configurations. Upon internal D2-45057, D2-45157 firmware execution, pin becomes output, providing synchronizing signal to on-board power supply circuits. When operating as output, provides 4mA drive strength. Note: This pin may also be referenced as "PSTEMP" on some reference designs. Function is identical regardless of name.                         |

| 26  | PROTECTO                 | I/O  | 3.3                     | PWM protection input. Input has hysteresis. Protection monitoring functionality of pin is controlled by internal D2-45057, D2-45157 firmware, and dependent on which of the 4 amplifier configurations is enabled.                                                                                                                                                                                                                                                                                                                                                              |

| 27  | PROTECT1                 | I/O  | 3.3                     | PWM protection input. Input has hysteresis. Protection monitoring functionality of pin is controlled by internal D2-45057, D2-45157 firmware, and dependent on which of the 4 amplifier configurations is enabled.                                                                                                                                                                                                                                                                                                                                                              |

| 28  | PROTECT2                 | I/O  | 3.3                     | PWM protection input. Input has hysteresis. Protection monitoring functionality of pin is controlled by internal D2-45057, D2-45157 firmware, and dependent on which of the 4 amplifier configurations is enabled.                                                                                                                                                                                                                                                                                                                                                              |

| 29  | nERROR0                  | 0    | 3.3                     | Overcurrent protection output, channel A output stage. Open drain 16mA driver, with internal $100$ k $\Omega$ (approx.) pull-up. Pulls low when active from overcurrent detection of output stage.                                                                                                                                                                                                                                                                                                                                                                              |

| 30  | nERROR1                  | 0    | 3.3                     | Overcurrent protection output, channel B output stage. Open drain 16mA driver, with internal $100$ k $\Omega$ (approx.) pull-up. Pulls low when active from overcurrent detection of output stage.                                                                                                                                                                                                                                                                                                                                                                              |

| 31  | nERROR2                  | 0    | 3.3                     | Overcurrent protection output, channel C output stage. Open drain 16mA driver, with internal $100k\Omega$ (approx.) pull-up. Pulls low when active from overcurrent detection of output stage.                                                                                                                                                                                                                                                                                                                                                                                  |

| 32  | nERROR3                  | 0    | 3.3                     | Overcurrent protection output, channel D output stage. Open drain 16mA driver, with internal $100k\Omega$ (approx.) pull-up. Pulls low when active from overcurrent detection of output stage.                                                                                                                                                                                                                                                                                                                                                                                  |

| 33  | HVDDD                    | Р    | HV                      | Output stage D high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                                                                                                                                                                                                                                                                                                                                                       |

| 34  | HGNDD                    | GND  | HV                      | Output stage D high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 15).                                                                                                                                                                                                                                                                                                                                                                        |

| 35  | OUTD                     | 0    | HV                      | PWM power amplifier output, channel D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 36  | HSBSD                    | Ι    | HV                      | High-side boot strap input, output channel D. Capacitor couples to OUTD amplifier output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 37  | HSBSC                    | Ι    | HV                      | High-side boot strap input, output channel C. Capacitor couples to OUTC amplifier output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 38  | OUTC                     | 0    | HV                      | PWM power amplifier output, channel C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 39  | HGNDC                    | GND  | HV                      | Output stage C high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 15).                                                                                                                                                                                                                                                                                                                                                                        |

| 40  | HVDDC                    | Р    | HV                      | Output stage C high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                                                                                                                                                                                                                                                                                                                                                       |

| 41  | SUBOUT                   | 0    | 3.3                     | "Subwoofer" channel PWM output, with 16mA drive strength. Connects to filter network for supplying line-level analog output to subwoofer.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 42  | DNC                      | -    | -                       | Do not connect to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

11

# Pin Description (Continued)

| PIN | PIN<br>NAME<br>(Note 13) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                                                                                 |  |  |  |

|-----|--------------------------|------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 43  | IREF                     | Ι    | -                       | Overcurrent reference analog input. Used in setting the overcurrent error detect externally-<br>set threshold. The pin needs to be connected to a $100k\Omega$ resistor to ground to set the<br>overcurrent threshold according to the specified limits.    |  |  |  |

| 44  | VDDHV                    | Р    | +HV                     | High Voltage internal driver supply power. All of the HVDD[A:D] pins and the VDDHV pin<br>connect to the system "HV" power source. The internal +5V supply regulators also opera<br>from this VDDHV input.                                                  |  |  |  |

| 45  | REG5V                    | Р    | 5                       | 5V internal regulator filter connect. A $+5V$ supply is internally generated from the voltage source provided at the VDD pin. REG5V is used for external connection of a decoupling capacitor.                                                              |  |  |  |

| 46  | HVDDB                    | Р    | HV                      | Output stage B high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                                   |  |  |  |

| 47  | HGNDB                    | GND  | HV                      | Output stage B high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 15).                                                    |  |  |  |

| 48  | OUTB                     | 0    | HV                      | PWM power amplifier output, channel B.                                                                                                                                                                                                                      |  |  |  |

| 49  | HSBSB                    | Ι    | HV                      | High-side boot strap input, output channel B. Capacitor couples to OUTB amplifier output.                                                                                                                                                                   |  |  |  |

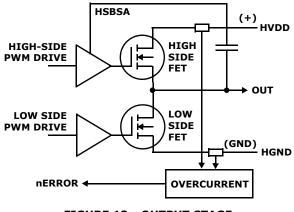

| 50  | HSBSA                    | Ι    | HV                      | High-side boot strap input, output channel A. Capacitor couples to OUTA amplifier output.                                                                                                                                                                   |  |  |  |

| 51  | OUTA                     | 0    | HV                      | PWM power amplifier output, channel A.                                                                                                                                                                                                                      |  |  |  |

| 52  | HGNDA                    | GND  | HV                      | Output stage A high voltage supply ground. A separate ground pin connection is provided for each of the output stages. All of the HGND[A:D] pins connect to system "HV" power ground (also see Note 15).                                                    |  |  |  |

| 53  | HVDDA                    | Р    | HV                      | Output stage A high voltage supply power. A separate power pin connection is provided for each of the output stages. All of the HVDD[A:D] pins and the VDDHV pin connect to the system "HV" power source.                                                   |  |  |  |

| 54  | nPDN                     | I    | 3.3                     | Power-down and mute input. Active low. When this input is low, all 4 outputs become inactive and their output stages float, and their output is muted. Internal logic and other references remain active during this power-down state.                      |  |  |  |

| 55  | LINER                    | 0    | 3.3                     | "Right" channel PWM output, with 16mA drive strength. Connects to filter network for supplying line-level analog output.                                                                                                                                    |  |  |  |

| 56  | LINEL                    | 0    | 3.3                     | "Left" channel PWM output, with 16mA drive strength. Connects to filter network for supplying line-level analog output.                                                                                                                                     |  |  |  |

| 57  | OCFG1                    | I    | 3.3                     | Output configuration control select. OCFG0 and OCFG1 are logic inputs to select the output configuration mode of the output stages. Connects to either PWMGND ground or PWMVDD (+3.3V) through nominal $10k\Omega$ resistor to select output configuration. |  |  |  |

| 58  | OCFG0                    | I    | 3.3                     | Output configuration control select. OCFG0 and OCFG1 are logic inputs to select the output configuration mode of the output stages. Connects to either PWMGND ground or PWMVDD (+3.3V) through nominal $10k\Omega$ resistor to select output configuration. |  |  |  |

| 59  | PWMGND                   | Р    | 3.3                     | PWM output pin ground. Internally connected to RGND.                                                                                                                                                                                                        |  |  |  |

| 60  | PWMVDD                   | Р    | 3.3                     | PWM output pin power. This 3.3V supply is used for the PWM pad drivers. Internally connected to RVDD.                                                                                                                                                       |  |  |  |

| 61  | PLLGND                   | Р    | 1.8                     | PLL Analog ground. Should be tied to low voltage ground (CGND, RGND) through single point connection to isolate ground noise on board and minimizing affecting of PLL.                                                                                      |  |  |  |

| 62  | XTALI                    | Р    | 1.8                     | Crystal oscillator analog input port.                                                                                                                                                                                                                       |  |  |  |

| 63  | XTALO                    | Р    | 1.8                     | Crystal oscillator analog output port. (This output drives the crystal and XTALO does not have a drive strength specification.)                                                                                                                             |  |  |  |

| 64  | PLLVDD                   | Р    | 1.8                     | PLL Analog power, 1.8V.                                                                                                                                                                                                                                     |  |  |  |

|     |                          | -    |                         |                                                                                                                                                                                                                                                                                            |

|-----|--------------------------|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | PIN<br>NAME<br>(Note 13) | ТҮРЕ | VOLTAGE<br>LEVEL<br>(V) | DESCRIPTION                                                                                                                                                                                                                                                                                |

| 65  | VOL0/<br>nSS             | I/O  | 3.3                     | Volume control pulse input and SPI slave select. At de-assertion of device reset, pin operates as SPI slave select input. Then upon internal D2-45057, D2-45157 firmware execution, pin becomes input for monitoring up/down phase pulses from volume control. (1 of 2 volume input pins.) |

| 66  | CGND                     | Р    | 1.8                     | Core ground                                                                                                                                                                                                                                                                                |

| 67  | CVDD                     | Р    | 1.8                     | Core power, +1.8VDC. Used in the chip internal DSP, logic and interfaces.                                                                                                                                                                                                                  |

| 68  | nRSTOUT                  | 0    | 3.3                     | Active low open drain output, with 16mA drive strength. Pin drives low from RVDD 3.3V brownout detector, PWMVDD 3.3V brownout detector, or 1.8V brownout detector going active. This output should be used to initiate a system reset to the nRESET pin upon brownout event detection.     |

## Pin Description (Continued)

NOTES:

13. Unless otherwise specified all pin names are active high. Those that are active low have an "n" prefix, such as nRESET.

- 14. All power and ground pins of same names are to be tied together to all other pins of their same name. (i.e., CVDD pins to be tied together, CGND pins to be tied together, RVDD pins to be tied together, and RGND pins to be tied together.) Also, CGND and RGND are to be tied together on board, and RGND and PWMGND pins are internally connected and are to be tied together on the board.

- 15. Thermal pad is internally connected to all 4 HGND ground pins (HGNDA, HGNDB, HGNDC, HGNDD). Any connection to the thermal pad must be made to the common ground for these 4 ground pins.

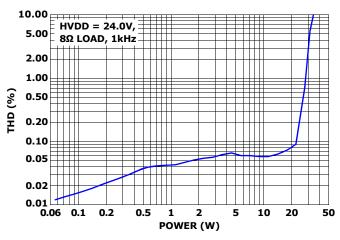

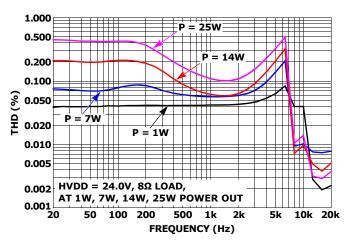

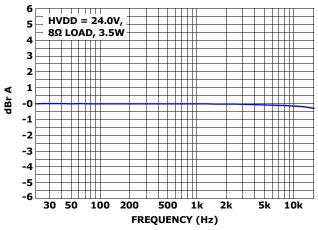

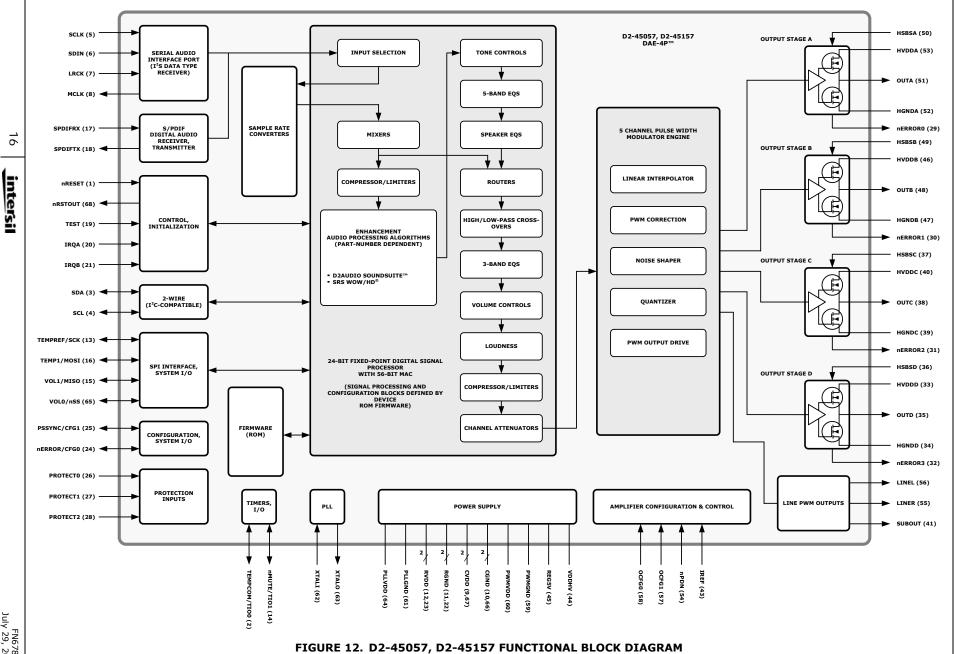

# **Typical Performance Characteristics**

#### **Test Considerations**

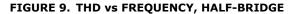

- Typical performance measurements are made using an Audio Precision™ 2700 Series audio analyzer.

- Precision power resistors are used for the  $8\Omega$  loudspeaker loads

- Measurements are done using a +HV supply of +24.0VDC.

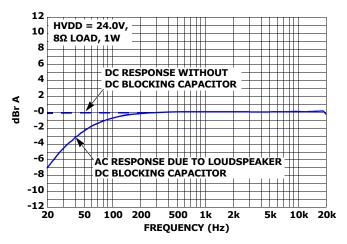

#### **Full-Bridge Typical Performance Curves**

FIGURE 4. THD vs POWER, FULL-BRIDGE

FIGURE 5. THD vs FREQUENCY, FULL-BRIDGE

FIGURE 6. FREQUENCY RESPONSE, FULL-BRIDGE

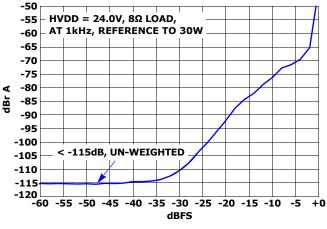

FIGURE 7. NOISE FLOOR, FULL-BRIDGE

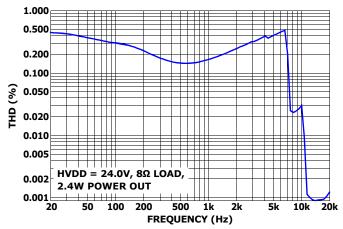

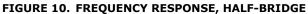

#### Half-Bridge Typical Performance Curves

FIGURE 11. NOISE FLOOR, HALF-BRIDGE

2-45057, 2-4515 Ň

FN6785.0 July 29, 2010

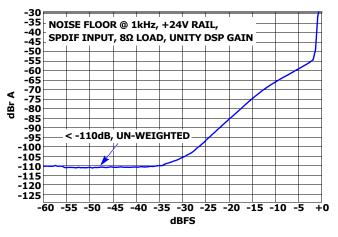

# **Functional Description**

#### Overview

The D2-45057, D2-45157 device, shown in Figure 12, is an integrated System-on-Chip (SoC) audio processor and Class D digital audio amplifier. It includes digital audio input selection, signal routing, complete audio processing, PWM controllers, amplifier and protection control, and integrated power stages. Stereo I<sup>2</sup>S and S/PDIF Digital input support, plus I<sup>2</sup>C and 2-wire SPI control interfaces provide integration compatibility with existing system architectures and solutions.

The four configurable power stages can operate as four separate Half-Bridge outputs, as two Full-Bridge outputs, or in combinations of Half-Bridge plus Full-Bridge outputs. Separate PWM outputs provide additional combinations to drive headphone, or line-level stereo and subwoofer outputs. These application-dependent configurations provide for driving Stereo (2.0) Speaker, 2.1 Speaker, and Stereo (2.2) Bi-Amp Speaker solutions, as well as providing Stereo Line outputs, Headphone outputs, or Subwoofer line outputs.

Audio output implementations are defined by configuration mode select pins, providing four combinations of powered and line amplifier outputs as shown in Table 1. The five independent audio processing paths feed a PWM engine, where its five PWM channels are mapped to the configuration-selected power stages and line outputs.

#### TABLE 1. OUTPUT CONFIGURATION MODES

| CONFIG<br>MODE | NAME                  | FUNCTION                                                                                     |

|----------------|-----------------------|----------------------------------------------------------------------------------------------|

| 0              | 2.0 L/R<br>4-Quadrant | <ul> <li>Powered Left and Right Outputs<br/>With 4-Quadrant, Full Bridge Drivers.</li> </ul> |

|                |                       | <ul> <li>No Line-Level Outputs</li> </ul>                                                    |

| 1              | 2.0 L/R<br>+          | <ul> <li>Powered Left and Right Outputs<br/>With 2-Quadrant, Full Bridge Drivers.</li> </ul> |

|                | L/R/Sub<br>Line       | <ul> <li>Stereo Left + Right Line-Level<br/>Outputs.</li> </ul>                              |

|                |                       | <ul> <li>Subwoofer Line-Level Output</li> </ul>                                              |

| 2              | 2.1<br>L/R/Sub        | <ul> <li>Two Half Bridge Drivers for Powered<br/>Left and Right Outputs.</li> </ul>          |

|                | +<br>L/R Line         | <ul> <li>2-Quadrant, Full Bridge Driver for<br/>Powered Subwoofer Output.</li> </ul>         |

|                |                       | <ul> <li>Two (Stereo Left + Right)<br/>Line-Level Outputs.</li> </ul>                        |

|                |                       | <ul> <li>Crossover Filtering Included Within<br/>Audio Path Signal Flow.</li> </ul>          |

| 3              | 2.2<br>Bi-Amp         | <ul> <li>Four Half Bridge Drivers for Powered<br/>Bi-Amp Left + Right Outputs.</li> </ul>    |

|                |                       | <ul> <li>Crossover Filtering Included Within<br/>Audio Path Signal Flow.</li> </ul>          |

The audio path includes a stereo Sample Rate Converter (SRC), five independent audio processing channels, plus device-specific audio enhancement algorithms.

Programmable parameter settings for audio processing include volume control, path routing and mixing, high/low pass filtering, multi-band equalizers, compressors, and loudness. These parameters can be adjusted using the D2Audio<sup>™</sup> Audio Canvas<sup>™</sup> software, or can be set by a system/amplifier microcontroller through the D2-45057, D2-45157 device's control interface.

#### **Audio Enhancement Features**

The D2-45057, D2-45157 devices include the D2Audio SoundSuite<sup>™</sup> or SRS WOW/HD<sup>™</sup> audio enhancement algorithms. These device-specific functions are integrated within the firmware as part of the standard audio processing signal flow, and are supported per device as:

- D2Audio SoundSuite<sup>™</sup> (WideSound<sup>™</sup>, DeepBass<sup>™</sup>, Audio Align<sup>™</sup>, and ClearVoice<sup>™</sup>) Audio Processing

- Included in the D2-45057 device

- SRS WOW/HD<sup>™</sup>

- Included in the D2-45157 device

Each of these enhancements utilizes its own algorithms, where choice of enhancement is specified by device part number. The D2-45057 includes only D2Audio SoundSuite™ support, and the D2-45157 includes only SRS WOW/HD™ support. These enhancements also have their own unique set of programmable parameters to control operation.

#### Serial Audio Digital Input

The D2-45057, D2-45157 devices include one Serial Audio Interface (SAI) port accommodating two digital audio input channels. This SAI port operates in slave mode only, supports the  $\rm I^2S$  digital audio industry standard, and can carry up to 24-bit Linear PCM audio words.

The digital audio input from the SAI input port routes directly through the Sample Rate Converters (SRC). Either the  $I^2S$  digital input, or the S/PDIF Digital input may be selected as the audio path source.

#### S/PDIF Digital Audio I/O

The D2-45057, D2-45157 contains one IEC60958 compliant S/PDIF Digital receiver input and one IEC60958 compatible S/PDIF Digital transmitter.

The S/PDIF Digital receiver input includes an input transition detector, digital PLL clock recovery, and a decoder to separate the audio data. The receiver meets the jitter tolerance specified in IEC60958-4.

The S/PDIF Digital transmitter complies with the consumer applications defined in IEC60958-3. The transmitter supports 24-bit audio data, but does not support user data and channel status.

Compressed digital formats are not decoded within the D2-45057, D2-45157 devices. But a bit-exact pass-through mode is supported from the SPDIFRX input to the SPDIFTX output, allowing for designs that require IEC61937-compliant original compressed audio input bitstream be made available at the product's S/PDIF Digital output.

#### Sample Rate Converter

The D2-45057, D2-45157 devices contain a 2-channel asynchronous sample rate converter (SRC) within the audio input signal flow path. This SRC is used to convert audio data input sampled at one input sample rate, to a fixed 48kHz output sample rate, aligning asynchronous input audio streams to a single rate for system processing.

Audio data presented to the SRC can be from either the SAI or S/PDIF Digital input sources, with an input sample rate from 16kHz to 192kHz. In addition to converting the input sample rate to the output sample rate, input clock jitter and sampling jitter is attenuated by the SRC, further enhancing audio quality.

#### DSP

A 24-bit fixed-point Digital Signal Processor (DSP) controls the majority of audio processing and system control functions within the D2-45057, D2-45157 devices.

Audio path signal routing, programmable-parameter processing blocks, and control logic are defined within the device's internal firmware. Signal flows through the device are buffered and processed through hardware specific-function blocks, such as the Sample Rate Converter. Internal device registers allow full integration of DSP control with the internal ROM-based firmware, as well as providing for external control of audio processing parameters.

#### **Clock and PLL**

Clock is generated on-chip, using a fundamental-mode crystal connected across the XTALI and XTALO pins. XTALO is an output, but is designed only to drive the crystal, and not connect to any other circuit. XTALI is an input, connecting to the other side of the crystal.

The clock generation contains a low jitter PLL to ensure low noise PWM output, and a precise master clock source for sample rate conversion and the audio processing data paths. The internal PLL's VCO clock operates at 12x the crystal frequency (12 x 24.576MHz) and provides complete device and system timing reference. It is used throughout the device, including clock generators for brown-out detection, system and power-on reset, DSP, S/PDIF Digital transmitter, and PWM engine timing.

Clock and PLL hardware functions are controlled by internal device firmware. They are not programmable and are optimized for device and system operation.

#### Timers

There are two independent timers used for device and system control. One timer is used for internal references for chip-specific operations. The other is used for the system/board temperature sensing control algorithm. There are two I/O pins (TIO0 and TIO1) associated with the timers. Their pin functions are defined by the device firmware. Only TIO0 is actually used in relationship to its timer, Timer 0, and operates the timing-related I/O functions of the temperature monitoring algorithm. Timer 1 is used for internal functions of the device. Its pin (TIO1) is not used for this timing operation and is defined by device firmware as the nMUTE input pin.

# **Audio Outputs**