## Intel® PXA255 Processor

Electrical, Mechanical, and Thermal Specification

#### **Data Sheet**

## **Product Features**

- High Performance Processor

- —Intel® XScale™ Microarchitecture

- -32 KB Instruction Cache

- -32 KB Data Cache

- -2 KB "mini" Data Cache

- —Extensive Data Buffering

- Intel® Media Processing Technology

- -Enhanced 16-bit Multiply

- -40-bit Accumulator

- Flexible Clocking

- —CPU clock from 100 to 400 MHz

- —Flexible memory clock ratios

- —Frequency change modes

- Rich Serial Peripheral Set

- -AC97 Audio Port

- —I<sup>2</sup>S Audio Port

- —USB Client Controller

- —High Speed UART

- —Second UART with flow control

- —UART with hardware flow control

- —FIR and SIR infrared comm ports

- Low Power

- Less than 500 mW Typical Internal Dissipation

- —Supply Voltage may be Reduced to  $1.00~\mathrm{V}$

- —Low Power/Sleep Modes

- High Performance Memory Controller

- -Four Banks of SDRAM up to 100 MHz

- —Five Static Chip Selects

- -Support for PCMCIA or Compact Flash

- —Companion Chip interface

- Additional Peripherals for system connectivity

- -Multimedia Card Controller (MMC)

- —SSP Controller

- -Network SSP controller for baseband

- —I2C Controller

- —Two Pulse Width Modulators (PWMs)

- —All peripheral pins double as GPIOs

- Hardware debug features

- Hardware Performance Monitoring features

Order Number: 278805-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The PXA255 processor EMTS Data Sheet may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2004

\*Other names and brands may be claimed as the property of others.

| 1.0 | About This Document       |                            |                                                  |    |  |  |

|-----|---------------------------|----------------------------|--------------------------------------------------|----|--|--|

| 2.0 | Func                      | tional O                   | verview                                          | 7  |  |  |

| 3.0 | Package Information       |                            |                                                  |    |  |  |

|     | 3.1                       | Packag                     | e Introduction                                   |    |  |  |

|     |                           | 3.1.1                      |                                                  |    |  |  |

|     |                           |                            | 3.1.1.1 PXA255 Processor Signal Pin Descriptions |    |  |  |

|     | 3.2                       | Packag                     | e Power Ratings                                  | 22 |  |  |

| 4.0 | Electrical Specifications |                            |                                                  |    |  |  |

|     | 4.1                       | Absolut                    | te Maximum Ratings                               | 22 |  |  |

|     | 4.2                       |                            | Consumption Specifications                       |    |  |  |

|     | 4.3                       |                            | ng Conditions                                    |    |  |  |

|     | 4.4                       |                            | ed DC Specifications                             |    |  |  |

|     | 4.5                       | Targeted AC Specifications |                                                  |    |  |  |

|     | 4.6                       | Oscillat                   | or Electrical Specifications                     | 28 |  |  |

|     |                           | 4.6.1                      | 32.768-kHz Oscillator Specifications             | 28 |  |  |

|     |                           | 4.6.2                      | 3.6864 MHz Oscillator Specifications             | 29 |  |  |

|     | 4.7                       | Reset a                    | and Power AC Timing Specifications               | 30 |  |  |

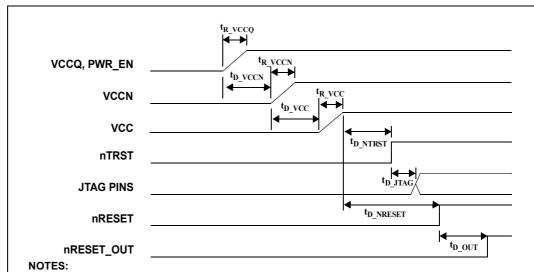

|     |                           | 4.7.1                      | Power-On Timing                                  | 30 |  |  |

|     |                           | 4.7.2                      | Hardware Reset Timing                            | 32 |  |  |

|     |                           | 4.7.3                      | Watchdog Reset Timing                            | 32 |  |  |

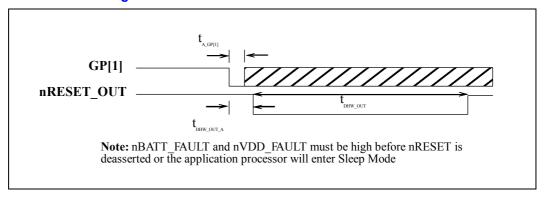

|     |                           | 4.7.4                      | GPIO Reset Timing                                | 32 |  |  |

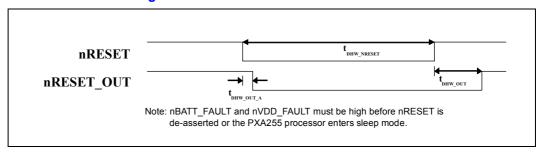

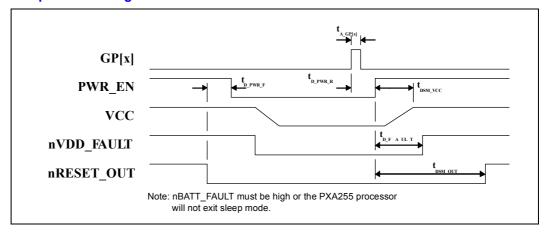

|     |                           | 4.7.5                      | Sleep Mode Timing                                | 33 |  |  |

|     | 4.8                       | Memory                     | y Bus and PCMCIA AC Specifications               | 35 |  |  |

|     | 4.9                       | Periphe                    | eral Module AC Specifications                    | 37 |  |  |

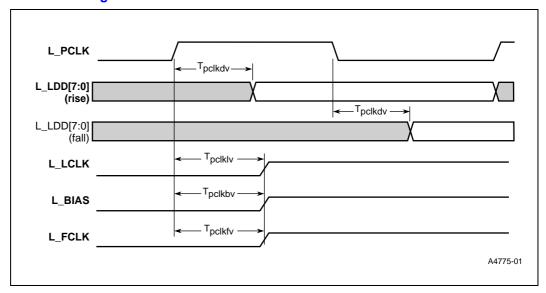

|     |                           | 4.9.1                      | LCD Module AC Timing                             | 37 |  |  |

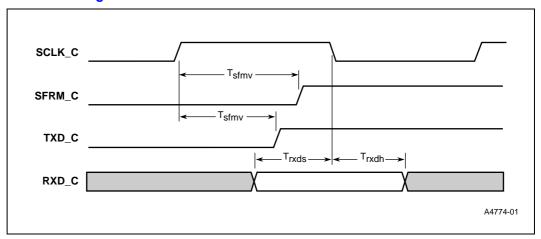

|     |                           | 4.9.2                      | SSP Module AC Timing                             | 37 |  |  |

|     |                           | 4.9.3                      | Boundary Scan Test Signal Timings                | 38 |  |  |

|     | 4 10                      | AC Tes                     | t Conditions                                     | 30 |  |  |

## **Figures**

**Tables**

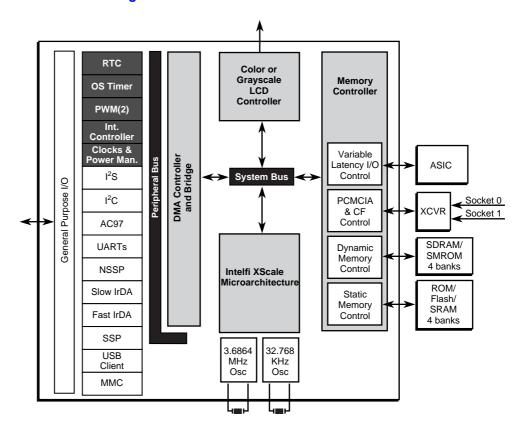

| 1  | Processor Block Diagram                                                  | 8  |

|----|--------------------------------------------------------------------------|----|

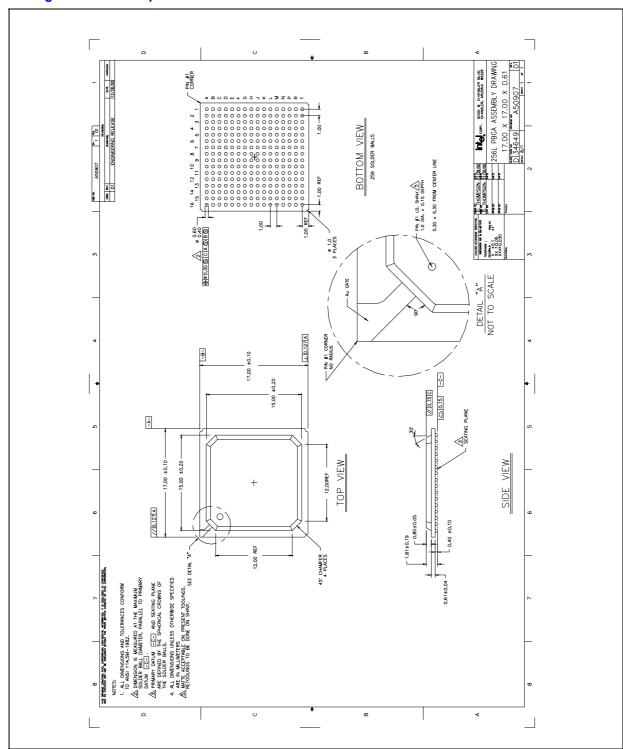

| 2  | PXA255 processor                                                         |    |

| 3  | Power-On Reset Timing                                                    |    |

| 4  | Hardware Reset Timing                                                    |    |

| 5  | GPIO Reset Timing                                                        |    |

| 6  | Sleep Mode Timing                                                        |    |

| 7  | LCD AC Timing Definitions                                                |    |

| 8  | SSP AC Timing Definitions                                                |    |

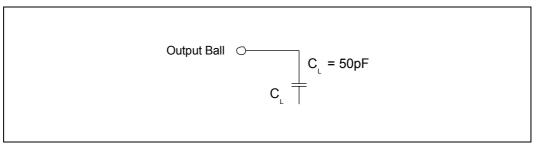

| 9  | AC Test Load                                                             |    |

|    |                                                                          |    |

| 1  | Related Documentation                                                    |    |

| 2  | Processor Pin Types                                                      |    |

| 3  | Pin and Signal Descriptions for the PXA255 Processor                     |    |

| 4  | Pin Description Notes                                                    |    |

| 5  | PXA255 processor 256-Lead 17x17mm mBGA Pinout — Ballpad No. Order        |    |

| 6  | $\theta_{JA}$ and Maximum Power Ratings                                  |    |

| 7  | Absolute Maximum Ratings                                                 |    |

| 8  | Power Consumption Specifications for PXA255 processor                    |    |

| 9  | Voltage, Temperature, and Frequency Electrical Specifications            |    |

| 10 | Standard Input, Output, and I/O Pin DC Operating Conditions              |    |

| 11 | Standard Input, Output, I/O Pin DC Operating Conditions for 2.5-V Memory |    |

| 12 | Standard Input, Output, and I/O Pin AC Operating Conditions              |    |

| 13 | 32.768-kHz Oscillator Specifications                                     | 28 |

| 14 | 3.6864-MHz Oscillator Specifications                                     | 29 |

| 15 | Power-On Timing Specifications                                           | 3  |

| 16 | Hardware Reset Timing Specifications                                     | 32 |

| 17 | GPIO Reset Timing Specifications                                         | 3  |

| 18 | Sleep Mode Timing Specifications                                         |    |

| 19 | SRAM / ROM / Flash / Synchronous Fast Flash AC Specifications            |    |

| 20 | Variable Latency I/O Interface AC Specifications                         |    |

| 21 | Card Interface (PCMCIA or Compact Flash) AC Specifications               |    |

| 22 | Synchronous Memory Interface AC Specifications 1                         |    |

| 23 | LCD AC Timing Specifications                                             |    |

| 24 | SSP AC Timing Specifications                                             |    |

| 25 | Roundary Scan Test Signal Timing                                         | 3  |

## Revision History

| Date          | Revision | Description                      |

|---------------|----------|----------------------------------|

| March 2003    | -001     | First public release of the EMTS |

| February 2004 | -002     | Updated 400 MHz Idle mode power. |

## 1.0 About This Document

This is the electrical, mechanical, and thermal specification data sheet for the Intel® PXA255 Processor. This data sheet contains a functional overview, mechanical data, package signal locations, targeted electrical specifications (simulated), and bus functional waveforms. Detailed functional descriptions other than parametric performance is published in the *Intel® PXA255 Processor Developer's Manual*. Refer to Table 1, "Related Documentation" for a list of documents that support the PXA255 processor.

#### **Table 1. Related Documentation**

| Document Title                                                                                                     | Order / Contact |

|--------------------------------------------------------------------------------------------------------------------|-----------------|

| Intel® PXA255 Processor Developer's Manual                                                                         | 278693          |

| Intel® XScale <sup>TM</sup> Microarchitecture for the PXA250 and PXA210 Applications Processors Developer's Manual | 278525          |

| Intel® PXA255 Processor Design Guide                                                                               | 278694          |

### 2.0 Functional Overview

The PXA255 processor provides high integration, high performance and low power consumption for portable handheld and handset devices. These processors incorporate the Intel® XScale™ Microarchitecture based on the ARM\* V5TE architecture. Refer to the Intel® XScale™ Microarchitecture for the Intel® PXA250 and PXA210 Applications Processors User's Manual for implementation details, extensions, and options implemented by the XScale microarchitecture.

The processor memory interface supports a variety of memory types that allow flexible design requirements. Hooks for connection to two companion chips permit glueless connection to external devices. An integrated LCD display controller supports displays and permits 1, 2, and 4-bit grayscale, and 8- or 16-bit color pixels. A 256-byte palette RAM provides flexible color mapping capabilities.

A rich set of serial devices as well as general-system resources provide enough compute and connectivity capability for many applications. For details on the programming model and theory of operation of each of these units, refer to the *Intel*® *PXA255 Processor Developer's Manual*. For the processor block diagram, refer to Figure 1, "Processor Block Diagram" on page 8.

Figure 1. Processor Block Diagram

## 3.0 Package Information

## 3.1 Package Introduction

The PXA255 processor is offered in a 256-pin mBGA (refer to Figure 2, "PXA255 processor" on page 19).

#### 3.1.1 Functional Signal Definitions

#### 3.1.1.1 PXA255 Processor Signal Pin Descriptions

Table 3, "Pin and Signal Descriptions for the PXA255 Processor" on page 9 describes the signal definitions for the PXA255 processor. Figure 2, "PXA255 processor" on page 19 illustrates the physical characteristics of the PXA255 processor. Table 5, "PXA255 processor 256-Lead 17x17mm mBGA Pinout — Ballpad No. Order" on page 20 describes the pinout for the PXA255 processor.

Some of the processor pins can be connected to multiple signals. The GAFRn\_m registers determine the signal connected to the pin. Some signals can go to multiple pins. The signal must be routed to one pin only by using the GAFRn\_m registers. Because this is true, some pins are listed twice—once in each unit that can use the pin. Not all peripherals can be used simutaneously in one design because different peripherals share the same pins.

**Table 2. Processor Pin Types**

| Туре  | Function                       |

|-------|--------------------------------|

| IC    | CMOS input                     |

| ОС    | CMOS output                    |

| OCZ   | CMOS output, Hi-Z              |

| ICOCZ | CMOS bidirectional, Hi-Z       |

| IA    | Analog Input                   |

| OA    | Analog output                  |

| IAOA  | Analog bidirectional           |

| SUP   | Supply pin (either VCC or VSS) |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 1 of 9)

| Pin Name       | Type                   | Signal Descriptions                                                                                                                                              | Reset State | Sleep State |  |  |  |

|----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--|--|--|

| Memory Control | Memory Controller Pins |                                                                                                                                                                  |             |             |  |  |  |

| MA[25:0]       | ocz                    | <b>Memory address bus.</b> (output) Signals the address requested for memory accesses.                                                                           | Driven Low  | Driven Low  |  |  |  |

| MD[15:0]       | ICOCZ                  | Memory data bus. (input/output) Lower 16 bits of the data bus.                                                                                                   | Hi-Z        | Driven Low  |  |  |  |

| MD[31:16]      | ICOCZ                  | Memory data bus. (input/output) Used for 32-bit memories.                                                                                                        | Hi-Z        | Driven Low  |  |  |  |

| nOE            | OCZ                    | <b>Memory output enable.</b> (output) Connect to the output enables of memory devices to control data bus drivers.                                               | Driven High | Note [4]    |  |  |  |

| nWE            | OCZ                    | Memory write enable. (output) Connect to the write enables of memory devices.                                                                                    | Driven High | Note [4]    |  |  |  |

| nSDCS[3:0]     | OCZ                    | SDRAM CS for banks 3 through 0. (output) Connect to the chip select (CS) pins for SDRAM. For the PXA255 processor processor nSDCS0 can be Hi-Z, nSDCS1-3 cannot. | Driven High | Note [5]    |  |  |  |

| DQM[3:0]       | OCZ                    | SDRAM DQM for data bytes 3 through 0. (output) Connect to the data output mask enables (DQM) for SDRAM.                                                          | Driven Low  | Driven Low  |  |  |  |

| nSDRAS         | OCZ                    | SDRAM RAS. (output) Connect to the row address strobe (RAS) pins for all banks of SDRAM.                                                                         | Driven High | Driven High |  |  |  |

| nSDCAS         | OCZ                    | SDRAM CAS. (output) Connect to the column address strobe (CAS) pins for all banks of SDRAM.                                                                      | Driven High | Driven High |  |  |  |

| SDCKE[0]       | ос                     | Synchronous Static Memory clock enable. (output) Connect to the CKE pins of SMROM. The memory controller provides control register bits for de-assertion.        | Driven Low  | Driven Low  |  |  |  |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 2 of 9)

| Pin Name             | Type  | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset State              | Sleep State      |

|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|

| SDCKE[1]             | ОС    | SDRAM and/or Synchronous Static Memory clock enable. (output) Connect to the clock enable pins of SDRAM. It is deasserted during sleep. SDCKE[1] is always de-asserted upon reset. The memory controller provides control register bits for de-assertion.                                                                                                                                                                                                                                                                                                                                                    | Driven low               | Driven low       |

| SDCLK[0]             | ос    | Synchronous Static Memory clock. (output) Connect to the clock (CLK) pins of SMROM. It is driven by either the internal memory controller clock, or the internal memory controller clock divided by 2. At reset, all clock pins are free running at the divide-by-2 clock speed and may be turned off via free-running control register bits in the memory controller. The memory controller also provides control register bits for clock division and deassertion of each SDCLK pin. SDCLK[0] control register assertion bit defaults to on if the boot-time static memory bank 0 is configured for SMROM. |                          |                  |

| SDCLK[1]             | OCZ   | SDRAM Clocks (output) Connect SDCLK[1] and SDCLK[2] to the clock pins of SDRAM in bank pairs 0/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Driven Low               | Driven Low       |

| SDCLK[2]             | ос    | and 2/3, respectively. They are driven by either the internal memory controller clock, or the internal memory controller clock, or the internal memory controller clock divided by 2. At reset, all clock pins are free running at the divide-by-2 clock speed and may be turned off via free-running control register bits in the memory controller. The memory controller also provides control register bits for clock division and de-assertion of each SDCLK pin. SDCLK[2:1] control register assertion bits are always de-asserted upon reset.                                                         | Driven Low               | Driven Low       |

| nCS[5]/<br>GPIO[33]  | ICOCZ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |                  |

| nCS[4]/<br>GPIO[80]  | ICOCZ | Static chip selects. (output) Chip selects to static                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |                  |

| nCS[3]/<br>GPIO[79]  | ICOCZ | memory devices such as ROM and Flash. Individually programmable in the memory configuration registers. nCS[5:0] can be used with variable latency I/O devices.                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pulled High -<br>Note[1] | Note [4]         |

| nCS[2]/<br>GPIO[78]  | ICOCZ | TICS[5.0] can be used with variable laterity i/O devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                  |

| nCS[1]/<br>GPIO[15]  | ICOCZ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |                  |

| nCS[0]               | ICOCZ | Static chip select 0. (output) Chip select for the boot memory. nCS[0] is a dedicated pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Driven High              | Note [4]         |

| RD/nWR               | OCZ   | Read/Write for static interface. (output) Signals that the current transaction is a read or write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Driven Low               | Holds last state |

| RDY/<br>GPIO[18]     | ICOCZ | Variable latency I/O ready pin. (input) Notifies the memory controller when an external bus device is ready to transfer data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pulled High -<br>Note[1] | Note [3]         |

| L_DD[8]/<br>GPIO[66] | ICOCZ | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  Memory controller alternate bus master request. (input) Allows an external device to request the system bus from the memory controller.                                                                                                                                                                                                                                                                                                                                                           | Pulled High -<br>Note[1] | Note [3]         |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 3 of 9)

| Pin Name                  | Туре       | Signal Descriptions                                                                                                                                                                                                                                                              | Reset State              | Sleep State |

|---------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|

| L_DD[15]/<br>GPIO[73]     | ICOCZ      | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  Memory controller grant. (output) Notifies an external device that it has been granted the system bus.                                                                | Pulled High -<br>Note[1] | Note [3]    |

| MBGNT/<br>GP[13]          | ICOCZ      | Memory controller grant. (output) Notifies an external device that it has been granted the system bus.                                                                                                                                                                           | Pulled High -<br>Note[1] | Note [3]    |

| MBREQ/<br>GP[14]          | ICOCZ      | Memory controller alternate bus master request. (input) Allows an external device to request the system bus from the memory controller.                                                                                                                                          | Pulled High -<br>Note[1] | Note [3]    |

| PCMCIA/CF Con             | ntrol Pins |                                                                                                                                                                                                                                                                                  |                          |             |

| nPOE/<br>GPIO[48]         | ICOCZ      | PCMCIA output enable. (output) Reads from PCMCIA memory and to PCMCIA attribute space.                                                                                                                                                                                           | Pulled High -<br>Note[1] | Note [5]    |

| nPWE/<br>GPIO[49]         | ICOCZ      | PCMCIA write enable. (output) Performs writes to PCMCIA memory and to PCMCIA attribute space. Also used as the write enable signal for variable latency I/O.                                                                                                                     | Pulled High -<br>Note[1] | Note [5]    |

| nPIOW/<br>GPIO[51]        | ICOCZ      | PCMCIA I/O write. (output) Performs write transactions to PCMCIA I/O space.                                                                                                                                                                                                      | Pulled High -<br>Note[1] | Note [5]    |

| nPIOR/<br>GPIO[50]        | ICOCZ      | PCMCIA I/O read. (output) Performs read transactions from PCMCIA I/O space.                                                                                                                                                                                                      | Pulled High -<br>Note[1] | Note [5]    |

| nPCE[2]/<br>GPIO[53]      | ICOCZ      | PCMCIA card enable 2. (output) Selects a PCMCIA card. nPCE[2] enables the high byte lane and nPCE[1] enables the low byte lane.  MMC clock. (output) Clock signal for the MMC controller.                                                                                        | Pulled High -<br>Note[1] | Note [5]    |

| nPCE[1]/<br>GPIO[52]      | ICOCZ      | PCMCIA card enable 1. (outputs) Selects a PCMCIA card. nPCE[2] enables the high byte lane and nPCE[1] enables the low byte lane.                                                                                                                                                 | Pulled High -<br>Note[1] | Note [5]    |

| nIOIS16/<br>GPIO[57]      | ICOCZ      | IO Select 16. (input) Acknowledge from the PCMCIA card that the current address is a valid 16 bit wide I/O address.                                                                                                                                                              | Pulled High -<br>Note[1] | Note [5]    |

| nPWAIT/<br>GPIO[56]       | ICOCZ      | <b>PCMCIA wait.</b> (input) Driven low by the PCMCIA card to extend the length of the transfers to/from the PXA255 processor processor.                                                                                                                                          | Pulled High -<br>Note[1] | Note [5]    |

| PSKTSEL/<br>GPIO[54]      | ICOCZ      | PCMCIA socket select. (output) Used by external steering logic to route control, address, and data signals to one of the two PCMCIA sockets. When PSKTSEL is low, socket zero is selected. When PSKTSEL is high, socket one is selected. Has the same timing as the address bus. | Pulled High -<br>Note[1] | Note [5]    |

| nPREG/<br>GPIO[55]        | ICOCZ      | PCMCIA register select. (output) Indicates that the target address on a memory transaction is attribute space. Has the same timing as the address bus.                                                                                                                           | Pulled High -<br>Note[1] | Note [5]    |

| LCD Controller F          | Pins       |                                                                                                                                                                                                                                                                                  |                          |             |

| L_DD(7:0)/<br>GPIO[65:58] | ICOCZ      | LCD display data. (outputs) Transfers pixel information from the LCD Controller to the external LCD panel.                                                                                                                                                                       | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[8]/<br>GPIO[66]      | ICOCZ      | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  Memory controller alternate bus master request. (input) Allows an external device to request the system bus from the Memory Controller.                               | Pulled High -<br>Note[1] | Note [3]    |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 4 of 9)

| Pin Name              | Type    | Signal Descriptions                                                                                                                                                                                          | Reset State              | Sleep State |

|-----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|

| L_DD[9]/<br>GPIO[67]  | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC chip select 0. (output) Chip select 0 for the MMC controller.                                 | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[10]/<br>GPIO[68] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC chip select 1. (output) Chip select 1 for the MMC controller.                                 | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[11]/<br>GPIO[69] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC clock. (output) Clock for the MMC controller.                                                 | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[12]/<br>GPIO[70] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  RTC clock. (output) Real-time clock 1 Hz tick.                                                    | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[13]/<br>GPIO[71] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  3.6864 MHz clock. (output) Output from 3.6864 MHz oscillator.                                     | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[14]/<br>GPIO[72] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  32 kHz clock. (output) Output from the 32 kHz oscillator.                                         | Pulled High -<br>Note[1] | Note [3]    |

| L_DD[15]/<br>GPIO[73] | ICOCZ   | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  Memory Controller grant. (output) Notifies an external device it has been granted the system bus. | Pulled High -<br>Note[1] | Note [3]    |

| L_FCLK/<br>GPIO[74]   | ICOCZ   | LCD frame clock. (output) Indicates the start of a new frame. Also referred to as Vsync.                                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |

| L_LCLK/<br>GPIO[75]   | ICOCZ   | LCD line clock. (output) Indicates the start of a new line. Also referred to as Hsync.                                                                                                                       | Pulled High -<br>Note[1] | Note [3]    |

| L_PCLK/<br>GPIO[76]   | ICOCZ   | LCD pixel clock. (output) Clocks valid pixel data into the LCD line-shift buffer.                                                                                                                            | Pulled High -<br>Note[1] | Note [3]    |

| L_BIAS/<br>GPIO[77]   | ICOCZ   | AC bias drive. (output) Notifies the panel to change the polarity for some passive LCD panel. For TFT panels, this signal indicates valid pixel data.                                                        | Pulled High -<br>Note[1] | Note [3]    |

| Full Function UA      | RT Pins |                                                                                                                                                                                                              |                          |             |

| FFRXD/<br>GPIO[34]    | ICOCZ   | Full function UART receive. (input)  MMC chip select 0. (output) Chip select 0 for the MMC Controller.                                                                                                       | Pulled High -<br>Note[1] | Note [3]    |

| FFTXD/<br>GPIO[39]    | ICOCZ   | Full Function UART transmit. (output)  MMC chip select 1. (output) Chip select 1 for the MMC Controller.                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |

| FFCTS/<br>GPIO[35]    | ICOCZ   | Full function UART clear-to-send. (input)                                                                                                                                                                    | Pulled High -<br>Note[1] | Note [3]    |

| FFDCD/<br>GPIO[36]    | ICOCZ   | Full function UART data-carrier-detect. (input)                                                                                                                                                              | Pulled High -<br>Note[1] | Note [3]    |

| FFDSR/<br>GPIO[37]    | ICOCZ   | Full function UART data-set-ready. (input)                                                                                                                                                                   | Pulled High -<br>Note[1] | Note [3]    |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 5 of 9)

| Pin Name              | Туре      | Signal Descriptions                                                                                                                                                                         | Reset State              | Sleep State |

|-----------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|

| FFRI/<br>GPIO[38]     | ICOCZ     | Full function UART ring indicator. (input)                                                                                                                                                  | Pulled High -<br>Note[1] | Note [3]    |

| FFDTR/<br>GPIO[40]    | ICOCZ     | Full function UART data-terminal-ready. (output)                                                                                                                                            | Pulled High -<br>Note[1] | Note [3]    |

| FFRTS/<br>GPIO[41]    | ICOCZ     | Full function UART request-to-send. (output)                                                                                                                                                | Pulled High -<br>Note[1] | Note [3]    |

| Bluetooth UART        | Pins      |                                                                                                                                                                                             |                          |             |

| BTRXD/<br>GPIO[42]    | ICOCZ     | Bluetooth UART receive. (input)                                                                                                                                                             | Pulled High -<br>Note[1] | Note [3]    |

| BTTXD/<br>GPIO[43]    | ICOCZ     | Bluetooth UART transmit. (output)                                                                                                                                                           | Pulled High -<br>Note[1] | Note [3]    |

| BTCTS/<br>GPIO[44]    | ICOCZ     | Bluetooth UART clear-to-send. (input)                                                                                                                                                       | Pulled High -<br>Note[1] | Note [3]    |

| BTRTS/<br>GPIO[45]    | ICOCZ     | Bluetooth UART request-to-send. (output)                                                                                                                                                    | Pulled High -<br>Note[1] | Note [3]    |

| Standard UART         | and ICP P | ins                                                                                                                                                                                         |                          |             |

| IRRXD/<br>GPIO[46]    | ICOCZ     | IrDA receive signal. (input) Receive pin for the FIR function.  Standard UART receive. (input)                                                                                              | Pulled High -<br>Note[1] | Note [3]    |

| IRTXD/<br>GPIO[47]    | ICOCZ     | IrDA transmit signal. (output) Transmit pin for the Standard UART, SIR and FIR functions.  Standard UART transmit. (output)                                                                 | Pulled High -<br>Note[1] | Note [3]    |

| Hardware UART         | Pins      |                                                                                                                                                                                             |                          |             |

| HWRXD/<br>GPIO[42/49] | ICOCZ     | Hardware UART receive. (input)                                                                                                                                                              | Pulled High -<br>Note[1] | Note [3]    |

| HWTXD/<br>GPIO[43/48] | ICOCZ     | Hardware UART transmit. (output)                                                                                                                                                            | Pulled High -<br>Note[1] | Note [3]    |

| HWCTS/<br>GPIO[44/50] | ICOCZ     | Hardware UART clear-to-send. (input)                                                                                                                                                        | Pulled High -<br>Note[1] | Note [3]    |

| HWRTS/<br>GPIO[45/51] | ICOCZ     | Hardware UART data-terminal-ready. (output)                                                                                                                                                 | Pulled High -<br>Note[1] | Note [3]    |

| MMC Controller        | Pins      |                                                                                                                                                                                             |                          |             |

| MMCMD                 | ICOCZ     | Multimedia card command. (bidirectional)                                                                                                                                                    | Hi-Z                     | Hi-Z        |

| MMDAT                 | ICOCZ     | Multimedia card data. (bidirectional)                                                                                                                                                       | Hi-Z                     | Hi-Z        |

| nPCE[2]/<br>GPIO[53]  | ICOCZ     | PCMCIA card enable 2. (outputs) Selects a PCMCIA card. Bit one enables the high byte lane and bit zero enables the low byte lane.  MMC clock. (output) Clock signal for the MMC controller. | Pulled High -<br>Note[1] | Note [5]    |

| L_DD[9]/<br>GPIO[67]  | ICOCZ     | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC chip select 0. (output) Chip select 0 for the MMC controller.                | Pulled High -<br>Note[1] | Note [3]    |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 6 of 9)

| Pin Name               | Type  | Signal Descriptions                                                                                                                                                          | Reset State              | Sleep State |  |

|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--|

| L_DD[10]/<br>GPIO[68]  | ICOCZ | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC chip select 1. (output) Chip select 1 for the MMC controller. | Pulled High -<br>Note[1] | Note [3]    |  |

| L_DD[11]/<br>GPIO[69]  | ICOCZ | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  MMC clock. (output) Clock for the MMC controller.                 | Pulled High -<br>Note[1] | Note [3]    |  |

| FFRXD/<br>GPIO[34]     | ICOCZ | Full function UART receive. (input)  MMC chip select 0. (output) Chip select 0 for the MMC controller.                                                                       | Pulled High -<br>Note[1] | Note [3]    |  |

| FFTXD/<br>GPIO[39]     | ICOCZ | Full function UART transmit. (output)  MMC chip select 1. (output) Chip select 1 for the MMC controller.                                                                     | Pulled High -<br>Note[1] | Note [3]    |  |

| MMCCLK/<br>GP[6]       | ICOCZ | MMC clock. (output) Clock signal for the MMC controller.                                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |  |

| MMCCS0/<br>GP[8]       | ICOCZ | <b>MMC</b> chip select 0. (output) Chip select 0 for the MMC controller.                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |  |

| MMCCS1/<br>GP[9]       | ICOCZ | <b>MMC</b> chip select 1. (output) Chip select 1 for the MMC controller.                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |  |

| SSP Pins               |       |                                                                                                                                                                              |                          |             |  |

| SSPSCLK/<br>GPIO[23]   | ICOCZ | Synchronous serial port clock. (output)                                                                                                                                      | Pulled High -<br>Note[1] | Note [3]    |  |

| SSPSFRM/<br>GPIO[24]   | ICOCZ | Synchronous serial port frame. (output)                                                                                                                                      | Pulled High -<br>Note[1] | Note [3]    |  |

| SSPTXD/<br>GPIO[25]    | ICOCZ | Synchronous serial port transmit. (output)                                                                                                                                   | Pulled High -<br>Note[1] | Note [3]    |  |

| SSPRXD/<br>GPIO[26]    | ICOCZ | Synchronous serial port receive. (input)                                                                                                                                     | Pulled High -<br>Note[1] | Note [3]    |  |

| SSPEXTCLK/<br>GPIO[27] | ICOCZ | Synchronous serial port external clock. (input)                                                                                                                              | Pulled High -<br>Note[1] | Note [3]    |  |

| NSSP Pins              |       |                                                                                                                                                                              |                          |             |  |

| NSSPSCLK/<br>GPIO[81]  | ICOCZ | Network synchronous serial port clock. (output/input)                                                                                                                        | Pulled High -<br>Note[1] | Note [3]    |  |

| NSSPSFRM/<br>GPIO[82]  | ICOCZ | Network synchronous serial port frame. (output/input)                                                                                                                        | Pulled High -<br>Note[1] | Note [3]    |  |

| NSSPTXD/<br>GPIO[83]   | ICOCZ | Network synchronous serial port transmit/recieve. (output/input)                                                                                                             | Pulled High -<br>Note[1] | Note [3]    |  |

| NSSPRXD/<br>GPIO[84]   | ICOCZ | Network synchronous serial port transmit/receive. (output/input)                                                                                                             | Pulled High -<br>Note[1] | Note [3]    |  |

| USB Client Pins        |       |                                                                                                                                                                              |                          |             |  |

| USB_P                  | IAOAZ | USB client positive. (bidirectional)                                                                                                                                         | Hi-Z                     | Hi-Z        |  |

| USB_N                  | IAOAZ | USB client negative pin. (bidirectional)                                                                                                                                     | Hi-Z                     | Hi-Z        |  |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 7 of 9)

| Pin Name                                             | Type  | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                         | Reset State              | Sleep State |  |  |

|------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--|--|

| AC97 Controller and I <sup>2</sup> S Controller Pins |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| BITCLK/<br>GPIO[28]                                  | ICOCZ | AC97 audio port bit clock. (input) AC97 clock is generated by Codec 0 and fed into the PXA255 processor processor and Codec 1.  AC97 Aaudio port bit clock. (output) AC97 clock is generated by the PXA255 processor.  I <sup>2</sup> S bit clock. (input) I <sup>2</sup> S clock is generated externally and fed into PXA255 processor.  I <sup>2</sup> S bit clock. (output) I <sup>2</sup> S clock is generated by the PXA255 processor. | Pulled High -<br>Note[1] | Note [3]    |  |  |

| SDATA_IN0/<br>GPIO[29]                               | ICOCZ | AC97 audio port data in. (input) Input line for Codec 0. I <sup>2</sup> S data in. (input) Input line for the I <sup>2</sup> S controller.                                                                                                                                                                                                                                                                                                  | Pulled High -<br>Note[1] | Note [3]    |  |  |

| SDATA_IN1/<br>GPIO[32]                               | ICOCZ | AC97 audio port data in. (input) Input line for Codec 1. I <sup>2</sup> S system clock. (output) System clock from I <sup>2</sup> S controller.                                                                                                                                                                                                                                                                                             | Pulled High -<br>Note[1] | Note [3]    |  |  |

| SDATA_OUT/<br>GPIO[30]                               | ICOCZ | AC97 audio port data out. (output) Output from the PXA255 processor to Codecs 0 and 1.  12S data out. (output) Output line for the I2S controller.                                                                                                                                                                                                                                                                                          | Pulled High -<br>Note[1] | Note [3]    |  |  |

| SYNC/<br>GPIO[31]                                    | ICOCZ | AC97 audio port sync signal. (output) Frame sync signal for the AC97 controller.  I <sup>2</sup> S sync. (output) Frame sync signal for the I <sup>2</sup> S controller.                                                                                                                                                                                                                                                                    | Pulled High -<br>Note[1] | Note [3]    |  |  |

| nACRESET                                             | ОС    | AC97 audio port reset signal. (output)                                                                                                                                                                                                                                                                                                                                                                                                      | Driven Low               | Driven Low  |  |  |

| I <sup>2</sup> C Controller P                        | ins   |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| SCL                                                  | ICOCZ | I <sup>2</sup> C clock. (bidirectional)                                                                                                                                                                                                                                                                                                                                                                                                     | Hi-Z                     | Hi-Z        |  |  |

| SDA                                                  | ICOCZ | I <sup>2</sup> C data. (bidirectional).                                                                                                                                                                                                                                                                                                                                                                                                     | Hi-Z                     | Hi-Z        |  |  |

| PWM Pins                                             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| PWM[1:0]/<br>GPIO[17:16]                             | ICOCZ | Pulse width modulation channels 0 and 1. (outputs)                                                                                                                                                                                                                                                                                                                                                                                          | Pulled High -<br>Note[1] | Note [3]    |  |  |

| DMA Pins                                             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| DREQ[1:0]/<br>GPIO[19:20]                            | ICOCZ | <b>DMA request.</b> (input) Notifies the DMA Controller that an external device requires a DMA transaction. DREQ[1] is GPIO[19]. DREQ[0] is GPIO[20].                                                                                                                                                                                                                                                                                       | Pulled High -<br>Note[1] | Note [3]    |  |  |

| GPIO Pins                                            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| GPIO[1:0]                                            | ICOCZ | <b>General purpose I/O.</b> Wakeup sources on both rising and falling edges on nRESET.                                                                                                                                                                                                                                                                                                                                                      | Pulled High -<br>Note[1] | Note [3]    |  |  |

| GPIO[14:2]                                           | ICOCZ | <b>General purpose I/O.</b> More wakeup sources for sleep mode.                                                                                                                                                                                                                                                                                                                                                                             | Pulled High -<br>Note[1] | Note [3]    |  |  |

| GPIO[22:21]                                          | ICOCZ | <b>General purpose I/O.</b> Additional General Purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                            | Pulled High -<br>Note[1] | Note [3]    |  |  |

| Crystal and Clock Pins                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| PXTAL                                                | ОА    | <b>3.6864 MHz crystal input.</b> No external caps are required.                                                                                                                                                                                                                                                                                                                                                                             | Note [2]                 | Note [2]    |  |  |

| PEXTAL                                               | IA    | <b>3.6864 MHz crystal output.</b> No external caps are required.                                                                                                                                                                                                                                                                                                                                                                            | Note [2]                 | Note [2]    |  |  |

| TXTAL                                                | OA    | 32 KHz crystal input. No external caps are required.                                                                                                                                                                                                                                                                                                                                                                                        | Note [2]                 | Note [2]    |  |  |

|                                                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 8 of 9)

| Pin Name              | Туре  | Signal Descriptions Reset State                                                                                                                                                                                                                                                                                                                                     |                          | Sleep State                                                                                               |

|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------|

| TEXTAL                | IA    | 32 kHz crystal output. No external caps are required.                                                                                                                                                                                                                                                                                                               | Note [2]                 | Note [2]                                                                                                  |

| L_DD[12]/<br>GPIO[70] | ICOCZ | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  RTC clock. (output) Real time clock 1 Hz tick.                                                                                                                                                                                                           | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| L_DD[13]/<br>GPIO[71] | ICOCZ | LCD display data. (output) Transfers the pixel information from the LCD controller to the external LCD panel.  3.6864 MHz clock. (output) Output from 3.6864 MHz oscillator.                                                                                                                                                                                        | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| L_DD[14]/<br>GPIO[72] | ICOCZ | LCD display data. (output) Transfers pixel information from the LCD controller to the external LCD panel.  32 kHz clock. (output) Output from the 32 kHz oscillator.                                                                                                                                                                                                | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| 48MHz/GP[7]           | ICOCZ | 48 MHz clock. (output) Peripheral clock output derived from the PLL.  NOTE: This clock is only generated when the USB unit clock enable is set.                                                                                                                                                                                                                     | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| RTCCLK/<br>GP[10]     | ICOCZ | <b>Real time clock.</b> (output) 1 Hz output derived from the 32 kHz or 3.6864 MHz output.                                                                                                                                                                                                                                                                          | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| 3.6MHz/GP[11]         | ICOCZ | B.6864 MHz clock. (output) Output from 3.6864 MHz Pulled High - Note[1]                                                                                                                                                                                                                                                                                             |                          | Note [3]                                                                                                  |

| 32kHz/GP[12]          | ICOCZ | 32 kHz clock. (output) Output from the 32 kHz oscillator.                                                                                                                                                                                                                                                                                                           | Pulled High -<br>Note[1] | Note [3]                                                                                                  |

| Miscellaneous P       | ins   |                                                                                                                                                                                                                                                                                                                                                                     |                          |                                                                                                           |

| BOOT_SEL<br>[2:0]     | IC    | Boot select pins. (input) Indicates type of boot device.                                                                                                                                                                                                                                                                                                            | Input                    | Input                                                                                                     |

| PWR_EN                | ос    | Power Enable for the power supply. (output) When negated, it signals the power supply to remove power to the core because the system is entering sleep mode.                                                                                                                                                                                                        | Driven High              | Driven low while<br>entering sleep<br>mode. Driven high<br>when sleep exit<br>sequence begins.            |

| nBATT_FAULT           | IC    | Main Battery Fault. (input) Signals that main battery is low or removed. Assertion causes PXA255 processor processor to enter sleep mode or force an imprecise data exception, which cannot be masked. PXA255 processor will not recognize a wake-up event while this signal is asserted. Minimum assertion time for nBATT_FAULT is 1 ms.                           | Input                    | Input                                                                                                     |

| nVDD_FAULT            | IC    | VDD Fault. (input) Signals that the main power source is going out of regulation. nVDD_FAULT causes the PXA255 processor to enter sleep mode or force an imprecise data exception, which cannot be masked. nVDD_FAULT is ignored after a wake-up event until the power supply timer completes (approximately 10 ms). Minimum assertion time for nVDD_FAULT is 1 ms. | Input                    | Input                                                                                                     |

| nRESET                | IC    | Hard reset. (input) Level -sensitive input used to start the processor from a known address. Assertion terminates the current instruction abnormally and causes a reset. When nRESET is driven high, the processor starts execution from address 0. nRESET must remain low until the power supply is stable and the internal 3.6864 MHz oscillator has stabilized.  | Input                    | Input. Driving low<br>during sleep will<br>cause normal<br>reset sequence<br>and exit from sleep<br>mode. |

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 9 of 9)

| Pin Name        | Туре    | Signal Descriptions                                                                                                                                                                                                               | Reset State                                                                       | Sleep State |

|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------|

| nRESET_OUT      | ОС      | Reset out. (output) Asserted when nRESET is asserted and deasserts after nRESET is de-asserted but before the first instruction fetch. nRESET_OUT is also asserted for "soft" reset events: sleep, watchdog reset, or GPIO reset. | Driven low during<br>any reset sequence<br>- driven high prior to<br>first fetch. | Driven Low  |

| JTAG and Test F | Pins    |                                                                                                                                                                                                                                   |                                                                                   |             |

| nTRST           | IC      | JTAG test interface reset. Resets the JTAG/debug port. If JTAG/debug is used, drive nTRST from low to high either before or at the same time as nRESET. If JTAG is not used, nTRST must be either tied to nRESET or tied low.     | Input                                                                             | Input       |

| TDI             | IC      | JTAG test data input. (input) Data from the JTAG controller is sent to the PXA255 processor using this pin. This pin has an internal pull-up resistor.                                                                            | Input                                                                             | Input       |

| TDO             | OCZ     | JTAG test data output. (output) Data from the PXA255 processor is returned to the JTAG controller using this pin.                                                                                                                 | Hi-Z                                                                              | Hi-Z        |

| TMS             | IC      | JTAG test mode select. (input) Selects the test mode required from the JTAG controller. This pin has an internal pull-up resistor.                                                                                                | Input                                                                             | Input       |

| тск             | IC      | JTAG test clock. (input) Clock for all transfers on the JTAG test interface.                                                                                                                                                      | Input                                                                             | Input       |