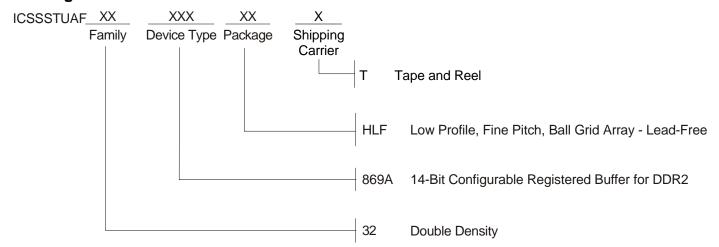

#### 14-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

### **ICSSSTUAF32869A**

### **Description**

The ICSSSTUAF32869A is 14-bit 1:2 registered buffer with parity, designed for 1.7 V to 1.9 V VDD operation.

All clock and data inputs are compatible with the JEDEC standard for SSTL\_18. The control inputs are LVCMOS. All outputs are 1.8V CMOS drivers optimized to drive the DDR2 DIMM load. They provide 50% more dynamic driver strength than the standard SSTU32864 outputs.

The ICSSSTUAF32869A operates from a differential clock (CLK and  $\overline{\text{CLK}}$ ). Data are registered at the crossing of CLK going high, and  $\overline{\text{CLK}}$  going low.

The device supports low-power standby operation. When the reset input (RESET) is low, the differential input receivers are disabled, and undriven (floating) data, clock and reference voltage (VREF) inputs are allowed. In addition, when RESET is low all registers are reset, and all outputs except PTYERR are forced low. The LVCMOS RESET input must always be held at a valid logic high or low level.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the low state during power up.

In the DDR2 RDIMM application, RESET is specified to be completely asynchronous with respect to CLK and CLK. Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be cleared and the outputs will be driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of reset, the register will become active quickly, relative to the time to enable the differential input receivers. ICSSSTUAF32869A must ensure that the outputs remain low as long as the data inputs are low, the clock is stable during the time from the low-to-high transition of RESET and the input receivers are fully enabled. This will ensures that there are no glitches on the output.

The device monitors both  $\overline{DCS}$  and  $\overline{CSR}$  inputs and will gate the Qn, PPO (Paritial-Parity-Out) and  $\overline{PTYERR}$  (Parity Error) Parity outputs from changing states when both  $\overline{DCS}$  and  $\overline{CSR}$  are high. If either  $\overline{DCS}$  and  $\overline{CSR}$  input is low, the Qn, PPO and  $\overline{PTYERR}$  outputs will function normally. The RESET input has priority over the  $\overline{DCS}$  and  $\overline{CSR}$  controls and will force the Qn and PPO outputs low and the  $\overline{PTYERR}$  high.

The ICSSTUAF32869A includes a parity checking function. The ICSSTUAF32869A accepts a parity bit from the memory controller at its input pin PARIN one or two cycles after the corresponding data input, compares it with the data received on the D-inputs and indicates on its opendrain PTYERR pin (active low) whether a parity error has occurred. The number of cycles depends on the setting of C1.

When used as a single device, the C1 input is tied low. When used in pairs, the C1 inputs is tied low for the first register (front) and the C1 input is tied high for the second register. When used as a single register, the PPO and PTYERR signals are produced two clock cycles after the corresponding data input. When used in pairs, the PTYERR signals of the first register are left floating. The PPO outputs of the first register are cascaded to the PARIN signas on the second register (back). The PPO and PTYERR signals of the second register are produced three clock cycles after the corresponding data input. Parity implimentation and device wiring for single and dual die is described in the diagram below.

If an error occurs, and the PTYERR is driven low, it stays low for two clock cycles or until RESET is driven low. The DIMM-dependent signals (DCKE, DCS, CSR and DODT) are not included in the parity check computations.

All registers used on an individual DIMM must be of the same configuration, i.e single or dual die.

### **Features**

- 14-bit 1:2 registered buffer with parity check functionality

- Supports SSTL\_18 JEDEC specification on data inputs and outputs

- 50% more dynamic driver strength than standard SSTU32864

- Supports LVCMOS switching levels on C1 and RESET inputs

- Low voltage operation: VDD = 1.7V to 1.9V

- Available in 150 BGA package

## **Applications**

- DDR2 Memory Modules

- Provides complete DDR DIMM solution with ICS98ULPA877A or IDTCSPUA877A

- Ideal for DDR2 400, 533, and 667

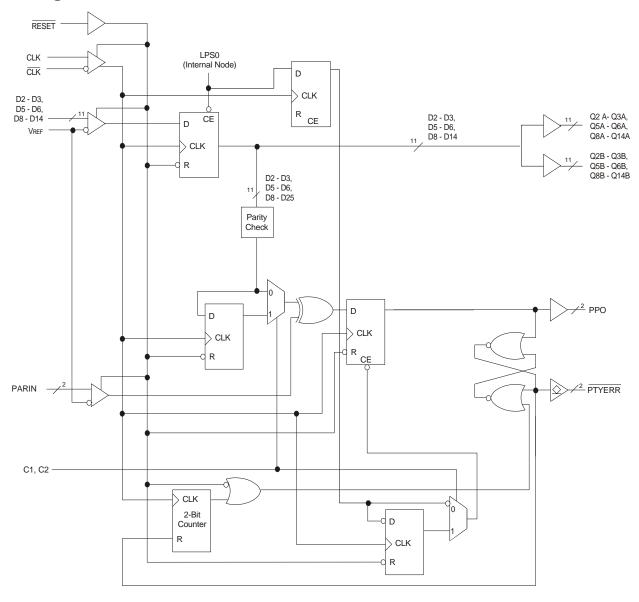

## **Parity Implementation and Device Wiring**

Set C=0 for Register 1, and C=1 for Register 2

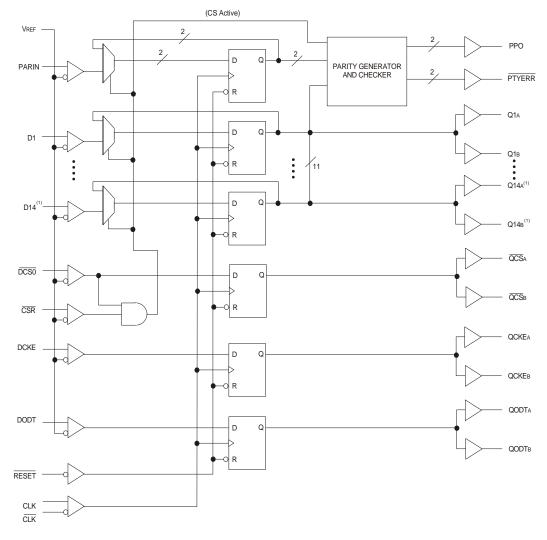

## **Block Diagram**

### NOTE:

1. This range does not include D1, D4, and D7, and their corresponding outputs.

# **Block Diagram**

### NOTE:

1.PARIN is used to generate PPO and PTYERR.

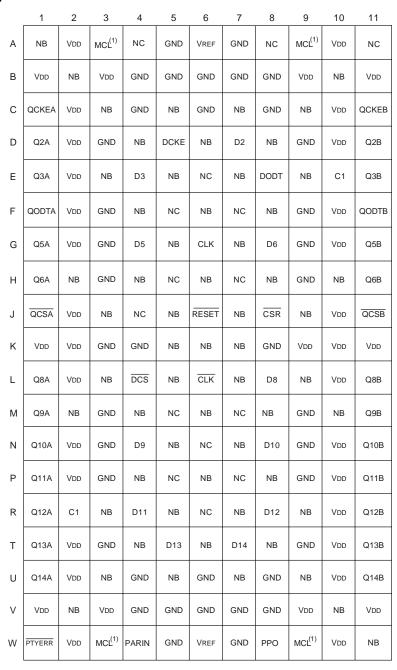

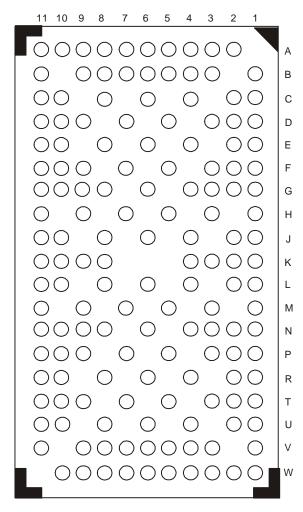

## **Pin Configuration**

## 150-Ball BGA TOP VIEW

### NOTE:

1.NC denotes a no-connect (ball present but not connected to the die). NB indicates no ball is populated at that gridpoint.

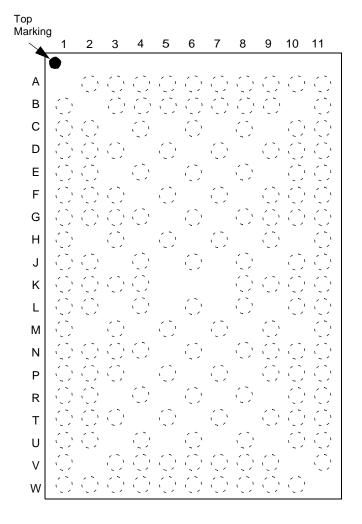

## 150 Ball CTBGA Package Attributes

**TOP VIEW**

**BOTTOM VIEW**

### **Function Table**

|       | Inputs <sup>1</sup> |                  |                  |                  |                |         | Out     | puts       |

|-------|---------------------|------------------|------------------|------------------|----------------|---------|---------|------------|

| RESET | DCS                 | CSR              | CLK              | CLK              | Dn, DODT, DCKE | Qn      | QCS     | QODT, QCKE |

| Н     | L                   | L                | 1                | $\downarrow$     | L              | L       | L       | L          |

| Н     | L                   | L                | 1                | <b>\</b>         | Н              | Н       | L       | Н          |

| Н     | L                   | L                | L or H           | L or H           | Х              | $Q_0^2$ | $Q_0^2$ | $Q_0^2$    |

| Н     | L                   | Н                | 1                | <b>\</b>         | L              | L       | L       | L          |

| Н     | L                   | Н                | 1                | <b>\</b>         | Н              | Н       | L       | Н          |

| Н     | L                   | Н                | L or H           | L or H           | Х              | $Q_0^2$ | $Q_0^2$ | $Q_0^2$    |

| Н     | Н                   | L                | 1                | <b>\</b>         | L              | L       | Н       | L          |

| Н     | Н                   | L                | 1                | <b>\</b>         | Н              | Н       | Н       | Н          |

| Н     | Н                   | L                | L or H           | L or H           | X              | $Q_0^2$ | $Q_0^2$ | $Q_0^2$    |

| Н     | Н                   | Н                | 1                | <b>\</b>         | L              | $Q_0^2$ | Н       | L          |

| Н     | Н                   | Н                | 1                | <b>\</b>         | Н              | $Q_0^2$ | Н       | Н          |

| Н     | Н                   | Н                | L or H           | L or H           | X              | $Q_0^2$ | $Q_0^2$ | $Q_0^2$    |

| L     | X or<br>Floating    | X or<br>Floating | X or<br>Floating | X or<br>Floating | X or Floating  | L       | L       | L          |

<sup>1</sup> H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

$\uparrow$  = LOW to HIGH

$\downarrow$  = HIGH to LOW

2 Output Level before the indicated steady-state conditions were established.

### **Terminal Functions**

| Signal<br>Group             | Terminal<br>Name                                                                       | Туре             | Description                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|----------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ungated<br>Inputs           | DCKE, DODT                                                                             | SSTL_18          | DRAM function pins not associated with Chip Select                                                                                                                                                                                                                                                                                   |

| Chip Select<br>Gated Inputs | D1D14 <sup>1</sup>                                                                     | SSTL_18          | DRAM inputs, re-driven only when Chip Select is LOW                                                                                                                                                                                                                                                                                  |

| Chip Select<br>Inputs       | $\overline{\text{DCS}}, \overline{\text{CSR}}$                                         | SSTL_18          | DRAM Chip Select signals. These pins initiate DRAM address/command decodes, and as such at least one will be LOW when a valid address/command is present.                                                                                                                                                                            |

| Re-Driven<br>Outputs        | Q1AQ14A <sup>1</sup> ,<br>Q1BQ14B <sup>1</sup> ,<br>QCSnA, B<br>QCKEnA, B<br>QODTnA, B | SSTL_18          | Outputs of the register, valid after the specified clock count and immediately following a rising edge of the clock                                                                                                                                                                                                                  |

| Parity Input                | PARIN                                                                                  | SSTL_18          | Input parity is received on pin PARIN, and should maintain odd parity across the D1:D14 inputs, at the rising edge of the clock, one cycle after Chip Select is LOW.                                                                                                                                                                 |

| Parity Output               | PPO                                                                                    | SSTL_18          | Partial Parity Output. Indicates parity out of D1-D14.                                                                                                                                                                                                                                                                               |

| Parity Error<br>Output      | PTYERR                                                                                 | Open Drain       | When LOW, this output indicates that a parity error was identified associated with the address and/or command inputs.  PTYERR will be active for two clock cycles, and delayed by in total two clock cycles for compatibility with final parity out timing on the industry-standard DDR2 register with parity (in JEDEC definition). |

| Configuration Inputs        | C1                                                                                     | SSTL_18          | When LOW, the register is configured as Register 1. When HIGH, the register is configured as Register 2.                                                                                                                                                                                                                             |

| Clock Inputs                | CLK, CLK                                                                               | SSTL_18          | Differential master clock input pair to the register. The register operation is triggered by a rising edge on the positive clock input (CLK).                                                                                                                                                                                        |

|                             | RESET                                                                                  | SSTL_18<br>Input | Asynchronous Reset Input. When LOW, it causes a reset of the internal latches, thereby forcing the outputs LOW. RESET also resets the PTYERR signal.                                                                                                                                                                                 |

| Miscellaneous<br>Inputs     | VREF                                                                                   | 0.9V nominal     | Input reference voltage for SSTL_18 inputs. Two pins (internally tied together) are used for increased Inputsreliability.                                                                                                                                                                                                            |

|                             | VDD                                                                                    | Power Input      | Power Supply Voltage                                                                                                                                                                                                                                                                                                                 |

|                             | GND                                                                                    | Ground Input     | Ground                                                                                                                                                                                                                                                                                                                               |

<sup>1</sup> This range does not include D1, D4, and D7, and their corresponding outputs.

## **Parity and Standby Function Table**

|       | Inputs <sup>1</sup> |                  |                  |                  |                                                |                    | Οι                | itputs               |

|-------|---------------------|------------------|------------------|------------------|------------------------------------------------|--------------------|-------------------|----------------------|

| RESET | DCS                 | CSR              | CLK              | CLK              | $\Sigma$ of Inputs = H (D1 - D14) <sup>2</sup> | PARIN <sup>3</sup> | PPO               | PTYERR <sup>4</sup>  |

| Н     | L                   | Х                | 1                | $\downarrow$     | Even                                           | L                  | L                 | Н                    |

| Н     | L                   | Х                | 1                | <b>\</b>         | Odd                                            | L                  | Н                 | L                    |

| Н     | L                   | Х                | 1                | <b>\</b>         | Even                                           | Н                  | Н                 | L                    |

| Н     | L                   | Х                | 1                | $\downarrow$     | Odd                                            | Н                  | L                 | Н                    |

| Н     | L                   | L                | 1                | $\downarrow$     | Even                                           | L                  | L                 | Н                    |

| Н     | L                   | L                | 1                | <b>\</b>         | Odd                                            | L                  | Н                 | L                    |

| Н     | L                   | L                | 1                | $\downarrow$     | Even                                           | Н                  | Н                 | L                    |

| Н     | L                   | L                | 1                | <b>\</b>         | Odd                                            | Н                  | L                 | Н                    |

| Н     | Н                   | Н                | 1                | <b>\</b>         | X                                              | Х                  | PPOn <sub>0</sub> | PTYERRn <sub>0</sub> |

| Н     | Х                   | Х                | L or H           | L or H           | X                                              | X                  | PPOn <sub>0</sub> | PTYERRn <sub>0</sub> |

| L     | X or<br>Floating    | X or<br>Floating | X or<br>Floating | X or<br>Floating | X or Floating                                  | X or Floating      | L                 | Н                    |

- 1 H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- $\uparrow$  = LOW to HIGH

- ↓= HIGH to LOW

- 2 This range does not include D1, D4, and D7.

- 3 PARIN arrives one clock cycle (C1 = 0), or two clock cycles (C1 = 1), after the data to which it applies.

- 4 This transition assumes PTYERR is HIGH at the crossing of CLK going HIGH and CLK going LOW. If PTYERR is LOW, it stays latched LOW for two clock cycles or until RESET is driven LOW. PARIN is used to generate PPO and PTYERR.

### **Absolute Maximum Ratings**

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Item                                         | Rating        |                      |  |

|----------------------------------------------|---------------|----------------------|--|

| Supply Voltage, VDD                          | -0.5V to 2.5V |                      |  |

| Input Voltage Range, VI <sup>1</sup>         |               | -0.5V to VDD + 2.5V  |  |

| Output Voltage Range, Vo <sup>1,2</sup>      |               | -0.5V to VDDQ + 0.5V |  |

| Input Clamp Current, lik                     |               | ±50mA                |  |

| Output Clamp Current, IOк                    |               | ±50mA                |  |

| Continuous Output Clamp Current, Io          |               | ±50mA                |  |

| Continuous Current through each VDD o        | or GND        | ±100mA               |  |

| Package Thermal Impedance (θja) <sup>3</sup> | 0m/s Airflow  | 40° C/W              |  |

| Package Thermal impedance (8ja)              | 1m/s Airflow  | 29° C/W              |  |

| Storage Temperature                          | 1             | -65 to +150° C       |  |

- 1 The input and output negative voltage ratings may be exceeded if the ratings of the I/P and O/P clamp current are observed.

- 2 This current will flow only when the output is in the high state level Vo > VDDQ.

- 3 The package thermal impedance is calculated in accordance with JESD 51.

### **Mode Select**

| C1 | Device Mode                 |

|----|-----------------------------|

| 0  | First device in pair, Front |

| 1  | Second device in pair, Back |

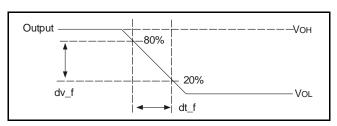

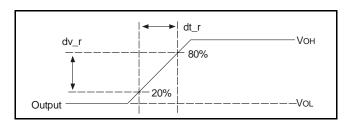

## **Output Buffer Characteristics**

Output edge rates over recommended operating free-air temperature range

|                      | $VDD = 1.8V \pm 0.1V$ |      |       |

|----------------------|-----------------------|------|-------|

| Parameter            | Min.                  | Max. | Units |

| dV/dt_r              | 1                     | 4    | V/ns  |

| dV/dt_f              | 1                     | 4    | V/ns  |

| $dV/dt_{\Delta}^{1}$ |                       | 1    | V/ns  |

<sup>1</sup> Difference between dV/dt\_r (rising edge rate) and dV/dt\_f (falling edge rate).

# Operating Characteristics, TA = 25° C

The RESET and Cn inputs of the device must be held at valid levels (not floating) to ensure proper device operation. The differential inputs must not be floating unless RESET is LOW.

| Symbol | Parameter                    |            | Min.         | Тур.      | Max.         | Units |

|--------|------------------------------|------------|--------------|-----------|--------------|-------|

| Vdd    | I/O Supply Voltage           |            | 1.7          | 1.8       | 1.9          | V     |

| VREF   | Reference Voltage            |            | 0.49 * VDD   | 0.5 * VDD | 0.51 * VDD   | V     |

| VTT    | Termination Voltage          |            | VREF - 0.04  | VREF      | VREF + 0.04  | V     |

| Vı     | Input Voltage                |            | 0            |           | VDD          | V     |

| VIH    | AC High-Level Input Voltage  | Dn, PARIN, | VREF + 0.25  |           |              |       |

| VIL    | AC Low-Level Input Voltage   | DCS, CSR,  |              |           | VREF - 0.25  | \ /   |

| VIH    | DC High-Level Input Voltage  | DCKEn,     | VREF + 0.125 |           |              | V     |

| VIL    | DC Low-Level Input Voltage   | DODTn      |              |           | VREF - 0.125 |       |

| VIH    | High-Level Input Voltage     | RESET, C1  | 0.65 * VDDQ  |           |              | V     |

| VIL    | Low-Level Input Voltage      | RESEI, CI  |              |           | 0.35 * VDDQ  | V     |

| VICR   | Common Mode Input Range      | CLK, CLK   | 0.675        |           | 1.125        | V     |

| VID    | Differential Input Voltage   | CLN, CLN   | 600          |           |              | mV    |

| Іон    | High-Level Output Current    |            |              |           | -12          | m Λ   |

| lol    | Low-Level Output Current     |            |              |           | 12           | mA    |

| IERROL | PTYERR Low-Level Output C    | 25         |              |           | mA           |       |

| TA     | Operating Free-Air Temperatu | ıre        | 0            |           | +70          | °C    |

## **DC Electrical Characteristics Over Operating Range**

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA =  $0^{\circ}$ C to +70°C, VDDQ/VDD = 1.8V ± 0.1V.

| Symbol | Parameter                                     | Test Conditions                                                                                                                                                   | Min.     | Тур. | Max. | Units                    |

|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|--------------------------|

| Vik    |                                               | II = -18mA                                                                                                                                                        |          |      | -1.2 | V                        |

| Vou    |                                               | VDDQ = 1.7V, IOH = -100μA                                                                                                                                         | VDDQ-0.2 |      |      | V                        |

| Voн    |                                               | VDDQ = 1.7V, IOH = -12mA                                                                                                                                          | 1.2      |      |      | V                        |

| 1/01   |                                               | VDDQ = 1.7V, IOL = 100μA                                                                                                                                          |          |      | 0.2  | V                        |

| Vol    |                                               | VDDQ = 1.7V, IOL = 12mA                                                                                                                                           |          |      | 0.5  | V                        |

| VERROL | PTYERR Output<br>Low Voltage                  | IERROL = 25mA; VDD = 1.7V                                                                                                                                         |          |      | 0.5  | V                        |

| lıL    | All Inputs                                    | VI = VDD or GND                                                                                                                                                   | -5       |      | +5   | μΑ                       |

|        | Static Standby                                | IO = 0, VDD = 1.9V, RESET = GND                                                                                                                                   |          |      | 200  | μΑ                       |

| ldd    | Static Operating                              | IO = 0, VDD = 1.9V, RESET = VDD, VI = VIH(AC) or VIL(AC), CLK = CLK = VIH(AC) or VIL(AC)                                                                          |          |      | 10   | - mA                     |

|        |                                               | IO = 0, VDD = 1.9V, RESET = VDD, VI = VIH(AC) or VIL(AC), CLK = VIH(AC), CLK = VIL(AC)                                                                            |          | 120  |      |                          |

|        | Dynamic<br>Operating (clock<br>only)          | IO = 0, VDD = 1.8V, RESET = VDD, VI = VIH(AC) or VIL(AC), CLK and CLK switching 50% duty cycle                                                                    |          | 247  |      | μΑ/Clock<br>MHz          |

| IDDD   | Dynamic<br>Operating (per<br>each data input) | IO = 0, VDD = 1.8V, RESET = VDD, VI = VIH(AC) or VIL(AC), CLK and CLK switching 50% duty cycle. One data input switching at half clock frequency, 50% duty cycle. |          | 52   |      | μΑ/Clock<br>MHz/<br>Data |

|        | Dn, PARIN, DSCn inputs                        | VI = VREF ± 250mV                                                                                                                                                 | 2        |      | 3    |                          |

| CIN    | CLK and CLK inputs                            | VICR = 0.9V, VIPP = 600mV                                                                                                                                         | 3.5      |      | 4.5  | pF                       |

|        | RESET                                         | VI = VDD or GND                                                                                                                                                   |          | 5    |      |                          |

# Timing Requirements Over Recommended Operating Free-Air Temperature Range

|                     |               |                                                                                                                                                                                                                  | VDD = 1.8 | 8V ± 0.1V |       |

|---------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|

| Symbol              | Parame        | eter                                                                                                                                                                                                             | Min.      | Max.      | Units |

| fclock              | Clock Fre     | equency                                                                                                                                                                                                          |           | 410       | MHz   |

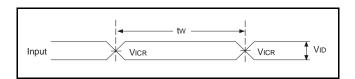

| tw                  | Pulse Du      | uration, CLK, CLK HIGH or LOW                                                                                                                                                                                    | 1         |           | ns    |

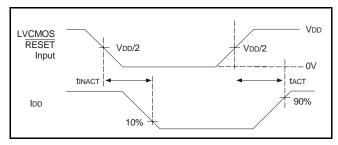

| tACT <sup>1</sup>   | Different     | ial Inputs Active Time                                                                                                                                                                                           |           | 10        | ns    |

| tinact <sup>2</sup> | Different     | ial Inputs Inactive Time                                                                                                                                                                                         |           | 15        | ns    |

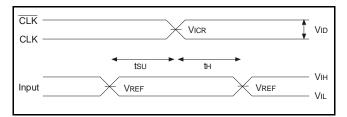

|                     |               | $\overline{\rm DCS}$ before CLK $\uparrow$ , $\overline{\rm CLK}\downarrow$ , $\overline{\rm CSR}$ HIGH; $\overline{\rm CSR}$ before CLK $\uparrow$ , $\overline{\rm CLK}\downarrow$ , $\overline{\rm DCS}$ HIGH | 0.7       |           |       |

| tsu                 | Setup<br>Time | DCS before CLK↑, CLK↓, CSR LOW                                                                                                                                                                                   | 0.5       |           | ns    |

|                     | Time          | DODT, DOCKE, and data before CLK↑, CLK↓                                                                                                                                                                          | 0.5       |           |       |

|                     |               | PAR_IN before CLK↑ , CLK↓                                                                                                                                                                                        | 0.5       |           |       |

| tH                  | Hold          | $\overline{ m DCS}$ , DODT, DCKE, and data after CLK $\uparrow$ , $\overline{ m CLK} \downarrow$                                                                                                                 | 0.5       |           | 20    |

| ιH                  | Time          | PAR_IN after CLK↑, CLK↓                                                                                                                                                                                          | 0.5       |           | ns    |

<sup>1</sup> VREF must be held at a valid input voltage level and data inputs must be held at valid logic levels for a minimum time of tACT(max) after RESET is taken HIGH.

# Switching Characteristics Over Recommended Free Air Operating Range (unless otherwise noted)

|        |                                                             | $VDD = 1.8V \pm 0.1V$ |      |       |

|--------|-------------------------------------------------------------|-----------------------|------|-------|

| Symbol | Parameter                                                   | Min.                  | Max. | Units |

| fMAX   | Max Input Clock Frequency                                   | 340                   |      | MHz   |

| tPDM   | Propagation Delay, single-bit switching, CLK↑ / CLK↓to Qn   | 1.1                   | 1.9  | ns    |

| tPDMSS | Propagation Delay, simultaneous switching, CLK↑ / CLK↓to Qn |                       | 2    | ns    |

| tLH    | LOW to HIGH Propagation Delay, CLK↑ / CLK↓to PTYERR         | 0.9                   | 3    | ns    |

| tHL    | HIGH to LOW Propagation Delay, CLK↑ / CLK↓to PTYERR         | 0.4                   | 2.4  | ns    |

| tPD    | Propagation Delay from CLK↑ / CLK↓to PPO                    | 0.3                   | 1.6  | ns    |

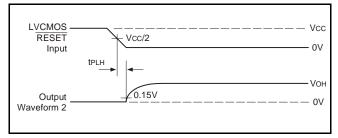

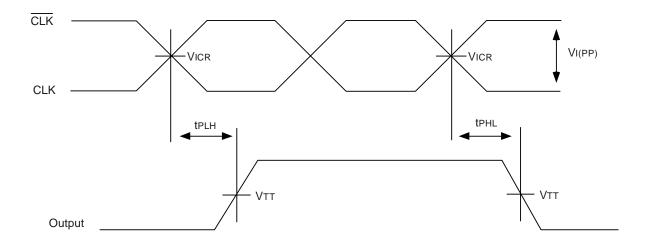

| tPHL   | HIGH to LOW Propagation Delay, RESET ↓ to Qn↓               |                       | 3    | ns    |

| tPLH   | LOW to HIGH Propagation Delay, RESET↓to PTYERR↑             |                       | 3    | ns    |

<sup>2</sup> VREF, data, and clock inputs must be held at a valid input voltage levels (not floating) for a minimum time of tinact(max) after RESET is taken LOW.

# **Output Buffer Characteristics**

Output edge rates over recommended operating free-air temperature range

|                      | $VDD = 1.8V \pm 0.1V$ |      |       |

|----------------------|-----------------------|------|-------|

| Parameter            | Min.                  | Max. | Units |

| dV/dt_r              | 1                     | 4    | V/ns  |

| dV/dt_f              | 1                     | 4    | V/ns  |

| $dV/dt_{\Delta}^{1}$ |                       | 1    | V/ns  |

<sup>1</sup> Difference between dV/dt\_r (rising edge rate) and dV/dt\_f (falling edge rate).

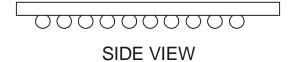

## **Register Timing**

- 1. This range does not include D1, D4, and D7, and their corresponding outputs.

- 2.PARIN is used to generate PPO and PTYERR.

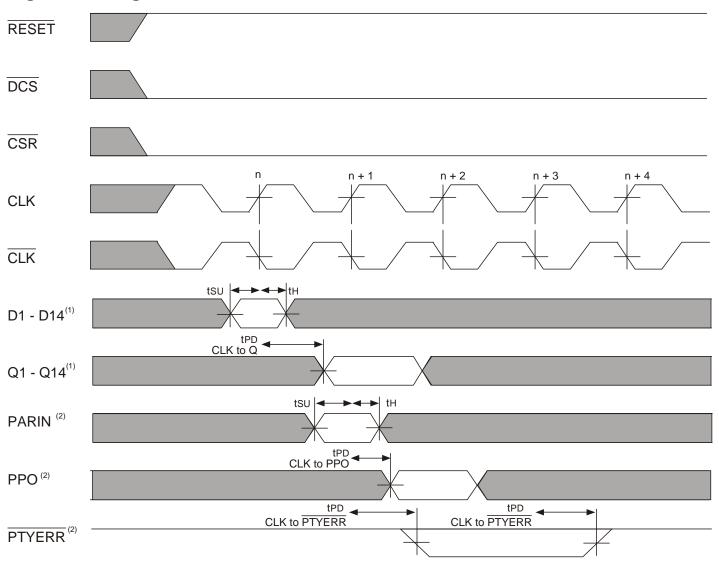

## **Register Timing**

- 1. This range does not include D1, D4, and D7, and their corresponding outputs.

- 2.PARIN is used to generate PPO and PTYERR.

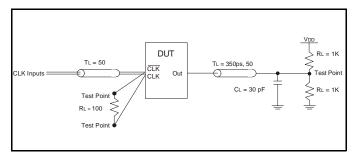

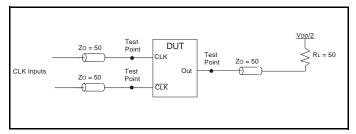

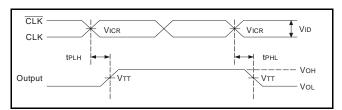

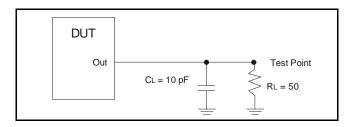

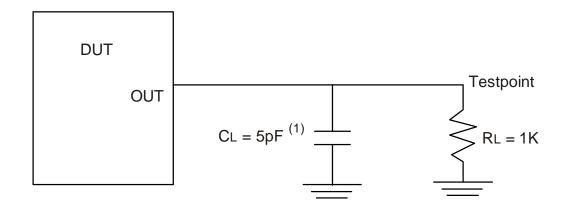

## Test Circuits and Waveforms (VDD = $1.8V \pm 0.1V$ )

**Simulation Load Circuit**

Voltage and Current Waveforms Inputs Active and Inactive

Times

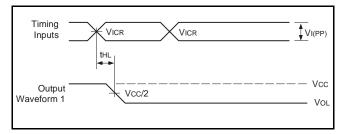

**Voltage Waveforms - Pulse Duration**

**Voltage Waveforms - Setup and Hold Times**

**Production-Test Load Circuit**

**Voltage Waveforms - Propagation Delay Times**

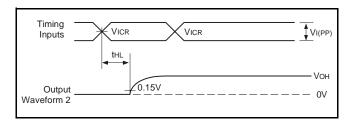

**Voltage Waveforms - Propagation Delay Times**

- 1. CL includes probe and jig capacitance.

- 2. IDD tested with clock and data inputs held at VDD or GND, and Io = 0mA

- 3. All input pulses are supplied by generators having the following characteristics: PRR  $\le 0$ MHz, Zo =  $50\Omega$  input slew rate = 1 V/ns  $\pm 20\%$  (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- 5. VTT = VREF = VDD/2

- 6. VIH = VREF + 250mV (AC voltage levels) for differential inputs. VIH = VDD for LVCMOS input.

- 7. VIL = VREF 250mV (AC voltage levels) for differential inputs. VIL = GND for LVCMOS input.

- 8. VID = 600mV.

- 9. tplh and tphl are the same as tppm.

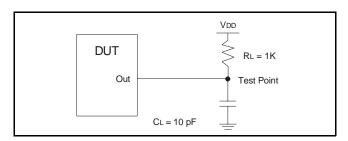

### Test Circuits and Waveforms (VDD = 1.8V ± 0.1V)

Load Circuit: High-to-Low Slew-Rate Adjustment

Voltage Waveforms: High-to-Low Slew-Rate Adjustment

Load Circuit: Low-to-High Slew-Rate Adjustment

Voltage Waveforms: Low-to-High Slew-Rate Adjustment

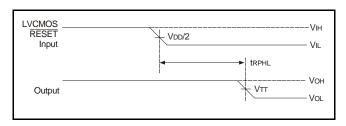

**Load Circuit: Error Output Measurements**

Voltage Waveforms: Open Drain Output Low-to-High Transition Time (with respect to RESET input)

Voltage Waveforms: Open Drain Output High-to-Low Transition Time (with respect to clock inputs)

Voltage Waveforms: Open Drain Output Low-to-High Transition Time (with respect to clock inputs)

- 1. CL includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq 0$ MHz, Zo =  $50\Omega$  input slew rate = 1 V/ns  $\pm 20\%$  (unless otherwise specified).

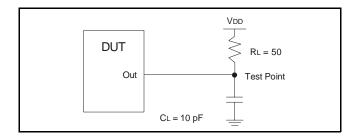

## Test Circuits and Waveforms (VDD = $1.8V \pm 0.1V$ )

### **Partial Parity Out Load Circuit**

Partial Parity Out Voltage Waveform, Propagation Delay Time with Respect to CLK Input

$\label{eq:VTT} $$VTT = VTT/2$$ VICR Cross Point Voltage $$VI(PP) = 600mV$$ $$tPLH and tPHL are the same as tPD.$

### **Ordering Information**

## Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

### **For Sales**

800-345-7015 408-284-8200 Fax: 408-284-2775

### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

IDT (Integrated Device Technology): SSTUAF32869AHLFT