## **LOW-COST, 3.3V ZERO DELAY BUFFER**

MPC962305

The MPC962309 is a zero delay buffer designed to distribute high-speed clocks. Available in a 16-pin SOIC or TSSOP package, the device accepts one reference input and drives nine low-skew clocks. The MPC962305 is the 8-pin version of the MPC962309 which drives five outputs with one reference input. The -1H versions of these devices have higher drive than the -1 devices and can operate up to 100/-133 MHz frequencies. These parts have on-chip PLLs which lock to an input clock presented on the REF pin. The PLL feedback is on-chip and is obtained from the CLOCKOUT pad.

#### **Features**

- 1:5 LVCMOS zero-delay buffer (MPC962305)

- 1:9 LVCMOS zero-delay buffer (MPC962309)

- Zero input-output propagation delay

- · Multiple low-skew outputs

- 250 ps max output-output skew

- 700 ps max device-device skew

- Supports a clock I/O frequency range of 10 MHz to 133 MHz, compatible with CPU and PCI bus frequencies

- Low jitter, 200 ps max cycle-cycle, and compatible with Pentium<sup>®</sup> based systems

- Test Mode to bypass PLL (MPC962309 only. See Table 3)

- 8-pin SOIC or 8-pin TSSOP package (MPC962305);16-pin SOIC or 16-pin TSSOP package (MPC962309)

- Single 3.3 V supply

- Ambient temperature range: –40°C to +85°C

- Compatible with the CY2305, CY23S05, CY2309, CY23S09

- Spread spectrum compatible

- Pb-free packages available

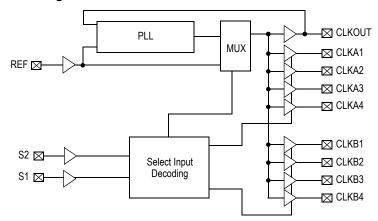

#### **Functional Description**

The MPC962309 has two banks of four outputs each, which can be controlled by the Select Inputs as shown in Table 3. Bank B can be tri-stated if all of the outputs are not required. Select inputs also allow the input clock to be directly applied to the outputs for chip and system testing purposes.

The MPC962305 and MPC962309 PLLs enters a power down state when there are no rising edges on the REF input. During this state, all of the outputs are in tristate, the PLL is turned off, and there is less than 25.0  $\mu$ A of current draw for the device. The PLL shuts down in one additional case as shown in Table 3.

Multiple MPC962305 and MPC962309 devices can accept the same input

clock and distribute it throughout the system. In this situation, the difference between the output skews of two devices will be less than 700 ps.

All outputs have less than 200 ps of cycle-cycle jitter. The input-to-output propagation delay on both devices is guaranteed to be less than 350 ps and the output-to-output skew is guaranteed to be less than 250 ps.

The MPC962305 and MPC962309 are available in two/three different configurations, as shown on the ordering information page. The MPC962305-1/MPC962309-1 are the base parts. High drive versions of those devices, MPC962305-1H and MPC962309-1H, are available to provide faster rise and fall times of the base device.

Pentium II is a trademark of Intel Corporation.

## MPC962305 MPC962309

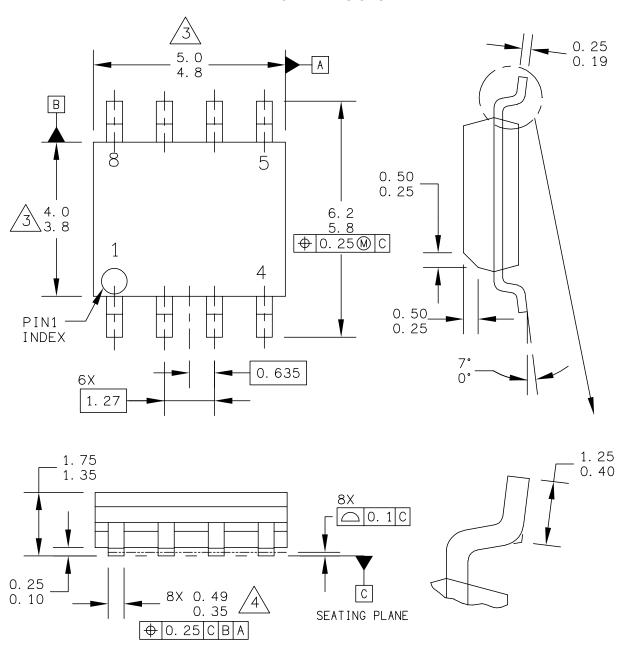

D SUFFIX 8-LEAD SOIC PACKAGE CASE 751-06

EF SUFFIX 8-LEAD SOIC PACKAGE Pb-FREE PACKAGE CASE 751-06

DT SUFFIX 8-LEAD TSSOP PACKAGE CASE 948J-01

EJ SUFFIX 8-LEAD TSSOP PACKAGE Pb-FREE PACKAGE CASE 948J-01

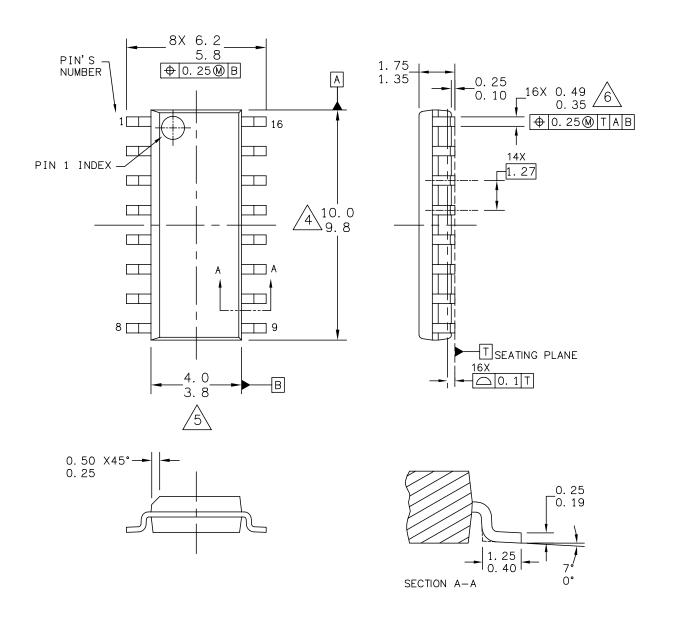

D SUFFIX 16-LEAD SOIC PACKAGE CASE 751B-05

EF SUFFIX 16-LEAD SOIC PACKAGE Pb-FREE PACKAGE CASE 751B-05

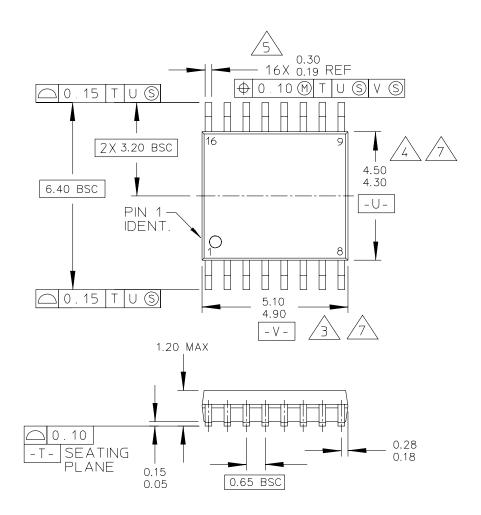

DT SUFFIX

16-LEAD TSSOP PACKAGE

CASE 948F-01

EJ SUFFIX

16-LEAD TSSOP PACKAGE

Pb-FREE PACKAGE

CASE 948F-01

#### **Block Diagram**

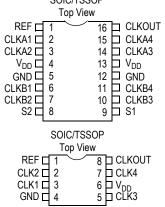

# Pin Configuration SOIC/TSSOP

Table 1. Pin Description for MPC962309

| Pin | Signal                | Description                                    |

|-----|-----------------------|------------------------------------------------|

| 1   | REF <sup>(1)</sup>    | Input reference frequency, 5 V-tolerant input  |

| 2   | CLKA1 <sup>(2)</sup>  | Buffered clock output, Bank A                  |

| 3   | CLKA2 <sup>(2)</sup>  | Buffered clock output, Bank A                  |

| 4   | V <sub>DD</sub>       | 3.3 V supply                                   |

| 5   | GND                   | Ground                                         |

| 6   | CLKB1 <sup>(2)</sup>  | Buffered clock output, Bank B                  |

| 7   | CLKB2 <sup>(2)</sup>  | Buffered clock output, Bank B                  |

| 8   | S2 <sup>(3)</sup>     | Select input, bit 2                            |

| 9   | S1 <sup>(3)</sup>     | Select input, bit 1                            |

| 10  | CLKB3 <sup>(2)</sup>  | Buffered clock output, Bank B                  |

| 11  | CLKB4 <sup>(2)</sup>  | Buffered clock output, Bank B                  |

| 12  | GND                   | Ground                                         |

| 13  | V <sub>DD</sub>       | 3.3 V supply                                   |

| 14  | CLKA3 <sup>(2)</sup>  | Buffered clock output, Bank A                  |

| 15  | CLKA4 <sup>(2)</sup>  | Buffered clock output, Bank A                  |

| 16  | CLKOUT <sup>(2)</sup> | Buffered output, internal feedback on this pin |

- 1. Weak pull-down.

- 2. Weak pull-down on all outputs.

- 3. Weak pull-ups on these inputs.

Table 2. Pin Description for MPC962305

| Pin | Signal                | Description                                          |  |  |  |

|-----|-----------------------|------------------------------------------------------|--|--|--|

| 1   | REF <sup>(1)</sup>    | Input reference frequency, 5 V-tolerant input        |  |  |  |

| 2   | CLK2 <sup>(2)</sup>   | uffered clock output                                 |  |  |  |

| 3   | CLK1 <sup>(2)</sup>   | Buffered clock output                                |  |  |  |

| 4   | GND                   | Ground                                               |  |  |  |

| 5   | CLK3 <sup>(2)</sup>   | Buffered clock output                                |  |  |  |

| 6   | V <sub>DD</sub>       | 3.3 V supply                                         |  |  |  |

| 7   | CLK4 <sup>(2)</sup>   | Buffered clock output                                |  |  |  |

| 8   | CLKOUT <sup>(2)</sup> | Buffered clock output, internal feedback on this pin |  |  |  |

- 1. Weak pull-down.

- 2. Weak pull-down on all outputs.

Table 3. Select Input Decoding for MPC962309

| S2 | S1 | CLOCK A1-A4 | CLOCK B1-B4 | CLKOUT <sup>(1)</sup> | Output Source | PLL Shutdown |

|----|----|-------------|-------------|-----------------------|---------------|--------------|

| 0  | 0  | Three-State | Three-State | Driven                | PLL           | N            |

| 0  | 1  | Driven      | Three-State | Driven                | PLL           | N            |

| 1  | 0  | Driven      | Driven      | Driven                | Reference     | Y            |

| 1  | 1  | Driven      | Driven      | Driven                | PLL           | N            |

<sup>1.</sup> This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the reference and output.

#### **Table 4. Maximum Ratings**

| Characteristics                                         | Value                        | Unit |

|---------------------------------------------------------|------------------------------|------|

| Supply Voltage to Ground Potential                      | -0.5 to +3.9                 | V    |

| DC Input Voltage (Except Ref)                           | -0.5 to V <sub>DD</sub> +0.5 | V    |

| DC Input Voltage REF                                    | -0.5 to 5.5                  | V    |

| Storage Temperature                                     | -65 to +150                  | °C   |

| Junction Temperature                                    | 150                          | °C   |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | >2000                        | V    |

#### Table 5. Operating Conditions for MPC962305-X and MPC962309-X Industrial Temperature Devices

| Parameter       | Description                                 | Min | Max | Unit |

|-----------------|---------------------------------------------|-----|-----|------|

| V <sub>DD</sub> | Supply Voltage                              | 3.0 | 3.6 | V    |

| T <sub>A</sub>  | Operating Temperature (Ambient Temperature) | -40 | 85  | °C   |

| C <sub>L</sub>  | Load Capacitance, below 100 MHz             |     | 30  | pF   |

| C <sub>L</sub>  | Load Capacitance, from 100 MHz to 133 MHz   |     | 10  | pF   |

| C <sub>IN</sub> | Input Capacitance                           |     | 7   | pF   |

#### Table 6. Electrical Characteristics for MPC962305-X and MPC962309-X Industrial Temperature Devices<sup>(1)</sup>

| Parameter                 | Description                        | Test Conditions                                                 | Min | Max   | Unit |

|---------------------------|------------------------------------|-----------------------------------------------------------------|-----|-------|------|

| V <sub>IL</sub>           | Input LOW Voltage <sup>(2)</sup>   |                                                                 |     | 0.8   | V    |

| $V_{IH}$                  | Input HIGH Voltage <sup>(2)</sup>  |                                                                 | 2.0 |       | V    |

| I <sub>IL</sub>           | Input LOW Current                  | V <sub>IN</sub> = 0 V                                           |     | 50.0  | μА   |

| I <sub>IH</sub>           | Input HIGH Current                 | $V_{IN} = V_{DD}$                                               |     | 100.0 | μА   |

| V <sub>OL</sub>           | Output LOW Voltage <sup>(3)</sup>  | I <sub>OL</sub> = 8 mA (-1)<br>I <sub>OH</sub> = 12 mA (-1H)    |     | 0.4   | V    |

| V <sub>OH</sub>           | Output HIGH Voltage <sup>(3)</sup> | I <sub>OH</sub> = -8 mA (-1)<br>I <sub>OL</sub> = -12 mA (-1H)  | 2.4 |       | V    |

| I <sub>DD</sub> (PD mode) | Power Down Supply Current          | REF = 0 MHz                                                     |     | 25.0  | μА   |

| I <sub>DD</sub>           | Supply Current                     | Unloaded outputs at 66.67 MHz,<br>SEL inputs at V <sub>DD</sub> |     | 35.0  | mA   |

<sup>1.</sup> All parameters are specified with loaded outputs.

<sup>2.</sup> REF input has a threshold voltage of V<sub>PP</sub>/2.

<sup>3.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

Table 7. Switching Characteristics for MPC962305-1 and MPC962309-1 Industrial Temperature Devices<sup>(1)</sup>

| Parameter         | Name                                                        | Test Conditions                                                                    | Min      | Тур  | Max           | Unit       |

|-------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|----------|------|---------------|------------|

| t <sub>1</sub>    | Output Frequency                                            | 30-pF load<br>10-pF load                                                           | 10<br>10 |      | 100<br>133.33 | MHz<br>MHz |

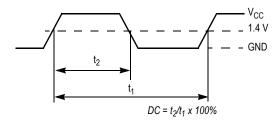

|                   | Duty Cycle <sup>(2)</sup> = $t_2 \div t_1$                  | Measured at 1.4 V, F <sub>OUT</sub> = 66.67 MHz                                    | 40.0     | 50.0 | 60.0          | %          |

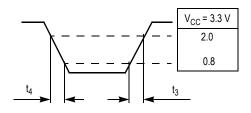

| t <sub>3</sub>    | Rise Time <sup>(2)</sup>                                    | Measured between 0.8 V and 2.0 V                                                   |          |      | 2.50          | ns         |

| t <sub>4</sub>    | Fall Time <sup>(2)</sup>                                    | Measured between 0.8 V and 2.0 V                                                   |          |      | 2.50          | ns         |

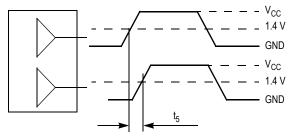

| t <sub>5</sub>    | Output to Output Skew <sup>(2)</sup>                        | All outputs equally loaded                                                         |          |      | 250           | ps         |

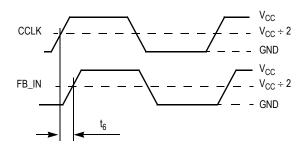

| t <sub>6A</sub>   | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at V <sub>DD</sub> /2                                                     |          | 0    | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at V <sub>DD</sub> /2. Measured in PLL Bypass Mode, MPC962309 device only | 1        | 5    | 8.7           | ns         |

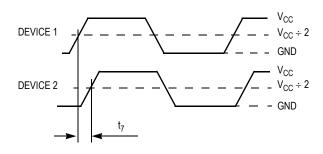

| t <sub>7</sub>    | Device to Device Skew <sup>(2)</sup>                        | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices                       |          | 0    | 700           | ps         |

| tJ                | Cycle to Cycle Jitter <sup>(2)</sup>                        | Measured at 66.67 MHz, loaded outputs                                              |          |      | 200           | ps         |

| t <sub>LOCK</sub> | PLL Lock Time <sup>(2)</sup>                                | Stable power supply, valid clock presented on REF pin                              |          |      | 1.0           | ms         |

<sup>1.</sup> All parameters are specified with loaded outputs.

Table 8. Switching Characteristics for MPC962305-1H and MPC962309-1H Industrial Temperature Devices<sup>(1)</sup>

| Parameter         | Name                                                        | Test Conditions                                                                    | Min      | Тур  | Max           | Unit       |

|-------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|----------|------|---------------|------------|

| t <sub>1</sub>    | Output Frequency                                            | 30-pF load<br>10-pF load                                                           | 10<br>10 |      | 100<br>133.33 | MHz<br>MHz |

|                   | Duty Cycle <sup>(2)</sup> = t2 ÷ t1                         | Measured at 1.4 V, F <sub>OUT</sub> = 66.67 MHz                                    | 40.0     | 50.0 | 60.0          | %          |

|                   | Duty Cycle <sup>(2)</sup> = t2 ÷ t1                         | Measured at 1.4 V, F <sub>OUT</sub> < 50 MHz                                       | 45.0     | 55.0 | 55.0          | %          |

| t <sub>3</sub>    | Rise Time <sup>(2)</sup>                                    | Measured between 0.8 V and 2.0 V                                                   |          |      | 1.50          | ns         |

| t <sub>4</sub>    | Fall Time <sup>(2)</sup>                                    | Measured between 0.8 V and 2.0 V                                                   |          |      | 1.50          | ns         |

| t <sub>5</sub>    | Output to Output Skew <sup>(2)</sup>                        | All outputs equally loaded                                                         |          |      | 250           | ps         |

| t <sub>6A</sub>   | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at V <sub>DD</sub> /2                                                     |          | 0    | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at V <sub>DD</sub> /2. Measured in PLL Bypass Mode, MPC962309 device only | 1        | 5    | 8.7           | ns         |

| t <sub>7</sub>    | Device to Device Skew <sup>(2)</sup>                        | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices                       |          | 0    | 700           | ps         |

| t <sub>8</sub>    | Output Slew Rate <sup>(2)</sup>                             | Measured between 0.8 V and 2.0 V using Test Circuit #2                             | 1        |      |               | V/ns       |

| tJ                | Cycle to Cycle Jitter <sup>(2)</sup>                        | Measured at 66.67 MHz, loaded outputs                                              |          |      | 200           | ps         |

| t <sub>LOCK</sub> | PLL Lock Time <sup>(2)</sup>                                | Stable power supply, valid clock presented on REF pin                              |          |      | 1.0           | ms         |

<sup>1.</sup> All parameters are specified with loaded outputs.

<sup>2.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

<sup>2.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

#### **APPLICATIONS INFORMATION**

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

Figure 1. Output-to-Output Skew t<sub>SK(O)</sub>

The time from the PLL controlled edge to the non-controlled edge, divided by the time between PLL controlled edges, expressed as a percentage

Figure 3. Output Duty Cycle (DC)

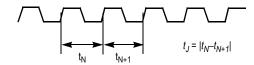

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

Figure 5. Cycle-to-Cycle Jitter

Figure 2. Static Phase Offset Test Reference

Figure 4. Device-to-Device Skew

Figure 6. Output Transition Time Test Reference

# $\begin{array}{c|c} & \text{Test Circuit \#1} \\ \hline 0.1 \ \mu\text{F} & & & \\ \hline & & \\ \hline & & & \\ \hline &$

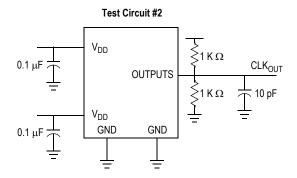

Test Circuit for all parameters except t<sub>8</sub>

Test Circuit for  $t_8$ , Output slew rate on -1H, -5 device

Table 9. Ordering Information

| Ordering Code    | Package Type                                  |

|------------------|-----------------------------------------------|

| MPC962305D-1     | 8-pin 150-mil SOIC                            |

| MPC962305D-1R2   | 8-pin 150-mil SOIC - Tape and Reel            |

| MPC962305EF-1    | 8-pin 150-mil SOIC (Pb-free)                  |

| MPC962305EF-1R2  | 8-pin 150-mil SOIC (Pb-free) - Tape and Reel  |

| MPC962305D-1H    | 8-pin 150-mil SOIC                            |

| MPC962305D-1HR2  | 8-pin 150-mil SOIC - Tape and Reel            |

| MPC962305EF-1H   | 8-pin 150-mil SOIC (Pb-free)                  |

| MPC962305EF-1HR2 | 8-pin 150-mil SOIC (Pb-free) - Tape and Reel  |

| MPC962305DT-1H   | 8-pin 150-mil TSSOP                           |

| MPC962305DT-1HR2 | 8-pin 150-mil TSSOP - Tape and Reel           |

| MPC962305EJ-1H   | 8-pin 150-mil TSSOP (Pb-free)                 |

| MPC962305EJ-1HR2 | 8-pin 150-mil TSSOP (Pb-free) - Tape and Reel |

| MPC962309D-1     | 16-pin 150-mil SOIC                           |

| MPC962309D-1R2   | 16-pin 150-mil SOIC - Tape and Reel           |

| MPC962309EF-1    | 16-pin 150-mil SOIC (Pb-free)                 |

| MPC962309EF-1R2  | 16-pin 150-mil SOIC (Pb-free) - Tape and Reel |

| MPC962309D-1H    | 16-pin 150-mil SOIC                           |

| MPC962309D-1HR2  | 16-pin 150-mil SOIC - Tape and Reel           |

| MPC962309EF-1H   | 16-pin 150-mil SOIC (Pb-free)                 |

| MPC962309EF-1HR2 | 16-pin 150-mil SOIC (Pb-free) - Tape and Reel |

| MPC962309DT-1H   | 16-pin 4.4-mm TSSOP                           |

| MPC962309DT-1HR2 | 16-pin 4.4-mm TSSOP - Tape and Reel           |

| MPC962309EJ-1H   | 16-pin 4.4-mm TSSOP (Pb-free)                 |

| MPC962309EJ-1HR2 | 16-pin 4.4-mm TSSOP (Pb-free) - Tape and Reel |

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |        | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------------------|--------|--------------|------------------|-------------|

| TITLE:                                                           |        | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROV                                                  | W BODY | CASE NUMBER  | R: 751–07        | 07 APR 2005 |

|                                                                  |        | STANDARD: JE | EDEC MS-012AA    |             |

PAGE 1 OF 2

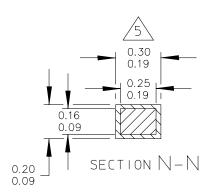

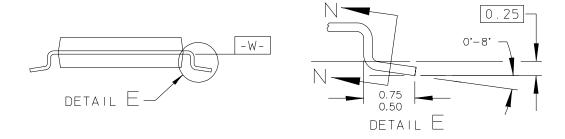

CASE 751-07 ISSUE U 8-LEAD SOIC PLASTIC PACKAGE

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

么 DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW                                      | / BODY    | CASE NUMBER  | R: 751–07        | 07 APR 2005 |

|                                                      |           | STANDARD: JE | DEC MS-012AA     |             |

PAGE 2 OF 2

#### **CASE 751-07 ISSUE U 8-LEAD SOIC PLASTIC PACKAGE**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               | 07 DITOU  | DOCUMENT NO  | ): 98ASB42566B   | REV: L      |

| 16LD SOIC N/B, 1.27 PITCH<br>CASE-OUTLINE            |           | CASE NUMBER  | R: 751B-05       | 11 APR 2005 |

|                                                      |           | STANDARD: JE | CCDEC MS-012AC   |             |

PAGE 1 OF 2

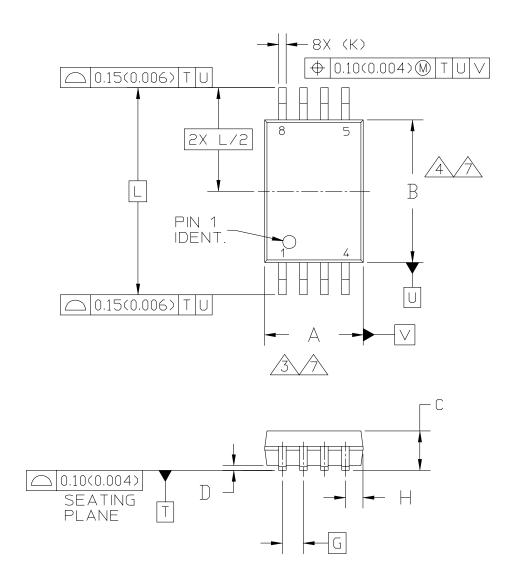

#### CASE 751B-05 ISSUE L 16-LEAD SOIC PLASTIC PACKAGE

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |   | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|-----------------------------------------------------------------|---|--------------|------------------|-------------|

| TITLE:                                                          |   | DOCUMENT NO  | ): 98ASB42566B   | REV: L      |

| 16LD SOIC N/B, 1.2°<br>CASE OUTLINE                             | • | CASE NUMBER  | R: 751B−05       | 11 APR 2005 |

| CASE OUTETNE                                                    | _ | STANDARD: JE | DEC MS-012AC     |             |

PAGE 2 OF 2

#### CASE 751B-05 ISSUE L 16-LEAD SOIC PLASTIC PACKAGE

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE             |        | PRINT VERSION NOT TO SCALE |  |  |

|------------------------------------------------------|--------------------------------|--------|----------------------------|--|--|

| TITLE:                                               | DOCUMENT NO                    | REV: B |                            |  |  |

| 16 LD TSSOP, PITCH 0.6.                              | CASE NUMBER: 948F-01 19 MAY 20 |        |                            |  |  |

| ,                                                    | STANDARD: JE                   | DEC    |                            |  |  |

PAGE 1 OF 3

#### CASE 948F-01 ISSUE B 16-LEAD TSSOP PLASTIC PACKAGE

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA                       | L OUTLINE | PRINT VERSION NO | IT TO SCALE |

|---------------------------------------------------------|---------------------------------|-----------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NO                     | RE√: B    |                  |             |

| 16 LD TSSOP, PITCH 0.                                   | CASE NUMBER: 948F-01 19 MAY 200 |           |                  |             |

| TO ED TOOLI, THEFT O.                                   | STANDARD: JE                    | DEC       |                  |             |

PAGE 2 OF 3

#### CASE 948F-01 ISSUE B 16-LEAD TSSOP PLASTIC PACKAGE

#### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M-1982.

DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

$^{\prime 4}ackslash$  dimension does not include interlead flash or protrusion. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

5\ DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

DIMENSIONS ARE TO BE DETERMINED AT DATUM PLANE -

|   | -W- |

|---|-----|

| - |     |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA                       | L OUTLINE | PRINT VERSION NO | IT TO SCALE |

|------------------------------------------------------|---------------------------------|-----------|------------------|-------------|

| TITLE:                                               | DOCUMENT NO                     | REV: B    |                  |             |

| 16 LD TSSOP, PITCH 0.6                               | CASE NUMBER: 948F-01 19 MAY 200 |           |                  |             |

|                                                      | STANDARD: JE                    | DEC       |                  |             |

PAGE 3 OF 3

#### **CASE 948F-01 ISSUE B 16-LEAD TSSOP PLASTIC PACKAGE**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE       |            | PRINT VERSION NOT TO SCALE |  |

|------------------------------------------------------|--------------------------|------------|----------------------------|--|

| TITLE:                                               | DOCUMENT NO: 98ASH70382A |            | REV: B                     |  |

| 8 LD TSSOP, PITCH 0                                  | CASE NUMBER              | 2: 948J-01 | 19 MAY 2005                |  |

| O LU 1330F, FITCH U                                  | STANDARD: JE             | DEC        |                            |  |

PAGE 1 OF 3

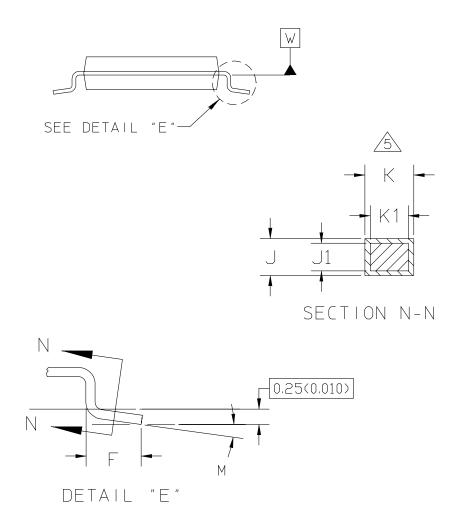

#### CASE 948J-01 ISSUE B 8-LEAD TSSOP PLASTIC PACKAGE

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MEC |           | L OUTLINE    | PRINT VERSION NOT TO SCALE |             |  |

|------------------------------------------------------------|-----------|--------------|----------------------------|-------------|--|

| TITLE:                                                     |           | DOCUMENT NO  | 1: 98ASH70382A             | RE√: B      |  |

| 8 LD TSSOP. PITCH 0.65MM                                   |           | CASE NUMBER  | 2: 948J-01                 | 19 MAY 2005 |  |

| 8 LD 1330F, FITCH 0                                        | .VIIVICO. | STANDARD: JE | DEC                        |             |  |

PAGE 2 OF 3

#### CASE 948J-01 ISSUE B 8-LEAD TSSOP PLASTIC PACKAGE

#### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER

- 2. DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (.006) PER SIDE.

- DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (.010) PER SIDE.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (.003) TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSIONS ARE TO BE DETERMINED AT DATUM PLANE -W-

|                          | IV                                                               | ICH   | MIL  | LIMETER                     |         | INCH          |             | MIL      | LIMETER |

|--------------------------|------------------------------------------------------------------|-------|------|-----------------------------|---------|---------------|-------------|----------|---------|

| DIM                      | MIN                                                              | MAX   | MIN  | MAX                         | DIM     | MIN           | MAX         | MIN      | MAX     |

| А                        | 0.114                                                            | 0.122 | 2.90 | 3.10                        |         |               |             |          |         |

| В                        | 0.169                                                            | 0.177 | 4.30 | 4.50                        |         |               |             |          |         |

| С                        | -                                                                | 0.047 | _    | 1.20                        |         |               |             |          |         |

| D                        | 0.002                                                            | 0.006 | 0.05 | 0.15                        |         |               |             |          |         |

| F                        | 0.020                                                            | 0.030 | 0.50 | 0.75                        |         |               |             |          |         |

| G                        | 0.026                                                            | BSC   | 0.   | 65 BSC                      |         |               |             |          |         |

| Н                        | 0.020                                                            | 0.024 | 0.50 | 0.60                        |         |               |             |          |         |

| J                        | 0.004                                                            | 0.008 | 0.09 | 0.20                        |         |               |             |          |         |

| J1                       | 0.004                                                            | 0.006 | 0.09 | 0.16                        |         |               |             |          |         |

| К                        | 0.007                                                            | 0.012 | 0.19 | 0.30                        |         |               |             |          |         |

| K1                       | 0.007                                                            | 0.010 | 0.19 | 0.25                        |         |               |             |          |         |

| L                        | 0.252                                                            | BSC   | 6.   | 40 BSC                      |         |               |             |          |         |

| M                        | 0°                                                               | 8°    | 0*   | 8°                          |         |               |             |          |         |

| © FI                     | © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |       |      | L OUT                       | LINE    | PRINT VER     | SION NE     | TO SCALE |         |

| TITLE:                   |                                                                  |       |      | DOCU                        | MENT NE | ]: 98ASH70382 | 2A          | REV: B   |         |

| 8 LD TSSOP, PITCH 0.65MM |                                                                  |       |      | CASE NUMBER: 948J-01 19 MAY |         |               | 19 MAY 2005 |          |         |

|                          |                                                                  |       | STAN | DARD: JE                    | DEC     |               |             |          |         |

PAGE 3 OF 3

CASE 948J-01 ISSUE B 8-LEAD TSSOP PLASTIC PACKAGE

### Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### **Asia Pacific and Japan**

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### **Europe**

IDT Europe, Limited 321 Kingston Road Leatherhead, Surrey KT22 7TU England +44 (0) 1372 363 339 Fax: +44 (0) 1372 378851

© 2007 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners.

Printed in USA