# **Ceramic transient voltage suppressors**

SMD multilayer transient voltage suppressors, low capacitance series

| _ |      | _   |    |    |

|---|------|-----|----|----|

| - | ries | e/T | ٧n | ο. |

|   |      |     |    |    |

Date: November 2010

© EPCOS AG 2010. Reproduction, publication and dissemination of this publication, enclosures hereto and the information contained therein without EPCOS' prior express consent is prohibited.

### Low capacitance series

### **SMD**

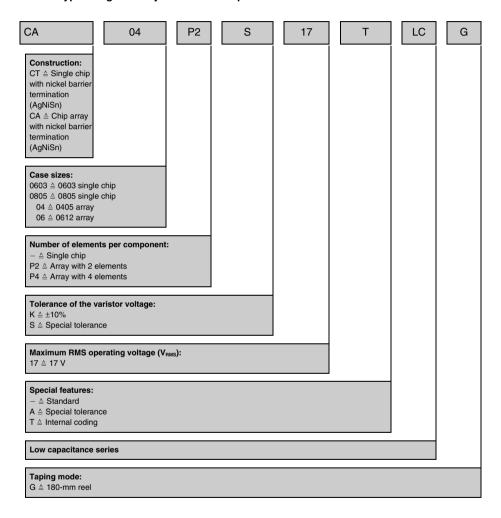

### EPCOS type designation system for low capacitance series

### Low capacitance series

### **SMD**

### **Features**

- ESD protection level acc. ISO 10605, IEC 61000-4-2 Level 4

- Bidirectional protection

- Low capacitance

- Low insertion loss

- Low leakage current

- No signal distortion

- RoHS-compatible

- Suitable for lead-free soldering

- PSpice simulation models available

- Customer-specific types on request

### **Applications**

ESD protection of data lines e.g. in notebooks and portable devices

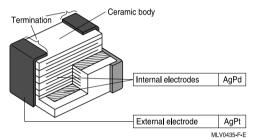

### Design

- Multilayer technology

- Lack of plastic or epoxy encapsulation for flammability rating better than UL 94 V-0

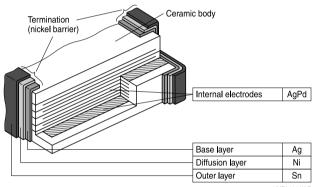

- Termination (see "Soldering directions"):

- CT and CA types with nickel barrier terminations (AgNiSn), recommended for lead-free soldering, and compatible with tin/lead solder.

### V/I characteristics and derating curves

V/I and derating curves are attached to the data sheet. The curves are sorted by  $V_{\text{RMS}}$  and then by case size, which is included in the type designation.

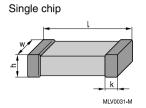

### Single chip

### Internal circuit

MLV0006-H

### Available case sizes:

| EIA  | Metric |

|------|--------|

| 0603 | 1608   |

| 0805 | 2012   |

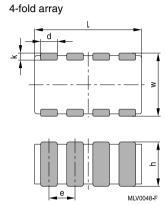

### Array

### Internal circuit

2-fold array

4-fold array

### Available case sizes:

| EIA  | Metric | Version      |  |  |

|------|--------|--------------|--|--|

| 0405 | 1014   | 2-fold array |  |  |

| 0612 | 1632   | 4-fold array |  |  |

### Low capacitance series

# **SMD**

### General technical data

| Maximum RMS operating voltage    |                           | $V_{RMS,max}$          | 17       | V  |

|----------------------------------|---------------------------|------------------------|----------|----|

| Maximum DC operating voltage     |                           | $V_{DC,max}$           | 22       | V  |

| Contact discharge ESD capability | to IEC 61000-4-2          | $V_{ESD,contact}$      | 8        | kV |

| Air discharge ESD capability     | to IEC 61000-4-2          | $V_{ESD,air}$          | 15       | kV |

| Maximum surge current            | (8/20 μs)                 | I <sub>surge,max</sub> | 10 30    | Α  |

| Maximum capacitance              | (1 MHz, 1 V)              | C <sub>max</sub>       | 50 100   | pF |

| Maximum clamping voltage         | (8/20 μs)                 | $V_{\text{clamp,max}}$ | 50       | V  |

| Operating temperature            | for arrays                | T <sub>op</sub>        | -40/+85  | °C |

|                                  | for case size ≥ 0603      | T <sub>op</sub>        | -55/+125 | °C |

| Storage temperature              | for arrays                | LCT/UCT                | -40/+125 | °C |

|                                  | for case size $\geq$ 0603 | LCT/UCT                | -55/+150 | °C |

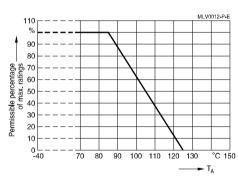

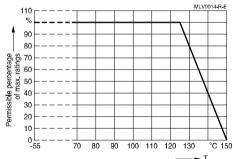

# Temperature derating

Climatic category: -40/+85 °C for arrays

Climatic category: -55/+125 °C for chip size  $\geq 0603$

### Low capacitance series

# **SMD**

# Electrical specifications and ordering codes Maximum ratings ( $T_{\text{op,max}}$ )

| Туре          | Ordering code   | $V_{RMS,max}$ | $V_{DC,max}$ | I <sub>surge,max</sub><br>(8/20 μs) | W <sub>max</sub><br>(2 ms) | $P_{diss,max}$ | $T_{op,max}$ |

|---------------|-----------------|---------------|--------------|-------------------------------------|----------------------------|----------------|--------------|

|               |                 | V             | ٧            | À                                   | mJ                         | mW             | °C           |

| 2-fold array  |                 |               |              |                                     |                            |                |              |

| CA04P2S17TLCG | B72762A2170S160 | 17            | 22           | 10                                  | 10                         | 3              | +85          |

| 4-fold array  |                 |               |              |                                     |                            |                |              |

| CA06P4S17TLCG | B72724A2170S162 | 17            | 22           | 30                                  | 75                         | 3              | +85          |

| Single chip   |                 |               |              |                                     |                            |                |              |

| CT0603K17LCG  | B72500T2170K060 | 17            | 22           | 10                                  | 100                        | 1              | +125         |

| CT0603S17ALCG | B72500T2170S160 | 17            | 22           | 30                                  | 75                         | 3              | +125         |

| CT0805K17LCG  | B72510T2170K062 | 17            | 22           | 30                                  | 100                        | 4              | +125         |

# Characteristics (T<sub>A</sub> = 25 °C)

| Туре          | V <sub>v,min</sub><br>(1 mA) | V <sub>V,max</sub><br>(1 mA) | $V_{clamp,max}$ | I <sub>clamp</sub> (8/20 μs) | C <sub>max</sub><br>(1 MHz, 1 V) |

|---------------|------------------------------|------------------------------|-----------------|------------------------------|----------------------------------|

|               | ٧                            | V                            | ٧               | Α                            | pF                               |

| 2-fold array  |                              |                              |                 |                              |                                  |

| CA04P2S17TLCG | 25                           | 40                           | 50              | 1                            | 75                               |

| 4-fold array  |                              |                              |                 |                              |                                  |

| CA06P4S17TLCG | 25                           | 40                           | 50              | 1                            | 75                               |

| Single chip   |                              |                              |                 |                              |                                  |

| CT0603K17LCG  | 24.3                         | 29.7                         | 50              | 1                            | 50                               |

| CT0603S17ALCG | 25                           | 40                           | 50              | 1                            | 75                               |

| CT0805K17LCG  | 24.8                         | 33                           | 50              | 1                            | 100                              |

# Low capacitance series

# **SMD**

# **Dimensional drawings**

### Dimensions in mm

| Case size<br>EIA / mm | 1          | w             | h        | d          | е          | k          |

|-----------------------|------------|---------------|----------|------------|------------|------------|

| 0603 / 1608           | 1.6 ±0.15  | 0.80 ±0.10    | 0.9 max. | -          | -          | 0.10 0.40  |

| 0805 / 2012           | 2.0 ±0.20  | 1.25 ±0.15    | 1.4 max. | -          | -          | 0.13 0.75  |

| 0405 / 1014           | 1.37 ±0.15 | 1.00 +0/-0.15 | 0.7 max. | 0.36 ±0.10 | 0.64 ±0.10 | 0.20 ±0.10 |

| 0612 / 1632           | 3.2 ±0.20  | 1.60 ±0.15    | 0.9 max. | 0.40 ±0.15 | 0.80 ±0.15 | 0.20 ±0.10 |

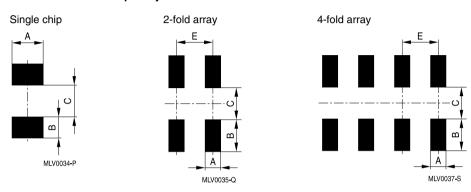

# Low capacitance series

# **SMD**

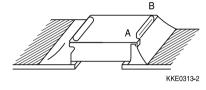

# Recommended solder pad layout

### Dimensions in mm

| Case size<br>EIA / mm |              | А    | В    | С    | Е    |

|-----------------------|--------------|------|------|------|------|

| 0603 / 1608           | Single chip  | 1.00 | 1.00 | 1.00 | -    |

| 0805 / 2012           | Single chip  | 1.40 | 1.20 | 1.00 | -    |

| 0405 / 1014           | 2-fold array | 0.40 | 0.55 | 0.28 | 0.64 |

| 0612 / 1632           | 4-fold array | 0.50 | 0.70 | 1.20 | 0.76 |

# **Delivery mode**

| EIA case size | Taping    | Reel size | Packing unit | Туре          | Ordering code   |

|---------------|-----------|-----------|--------------|---------------|-----------------|

|               |           | mm        | pcs.         |               |                 |

| 2-fold array  |           |           |              |               |                 |

| 0405          | Cardboard | 180       | 4000         | CA04P2S17TLCG | B72762A2170S160 |

| 4-fold array  |           |           |              |               |                 |

| 0612          | Blister   | 180       | 4000         | CA06P4S17TLCG | B72724A2170S162 |

| Single chip   |           |           |              |               |                 |

| 0603          | Cardboard | 180       | 4000         | CT0603K17LCG  | B72500T2170K060 |

| 0603          | Cardboard | 180       | 4000         | CT0603S17ALCG | B72500T2170S160 |

| 0805          | Blister   | 180       | 3000         | CT0805K17LCG  | B72510T2170K062 |

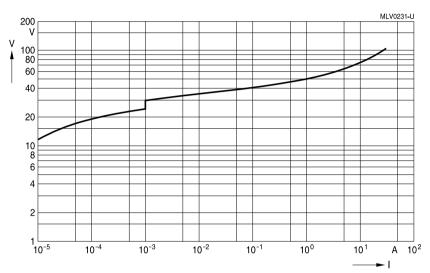

### Low capacitance series

# **SMD**

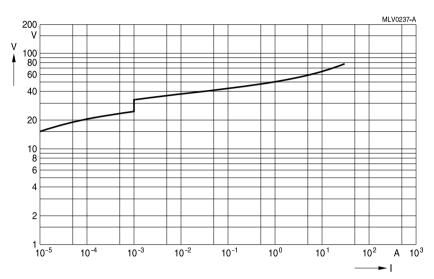

# V/I characteristics

### CT0603K17LCG

CT0603S17ALCG

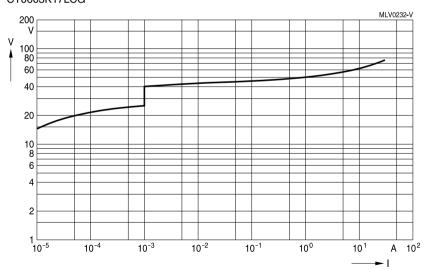

### Low capacitance series

# **SMD**

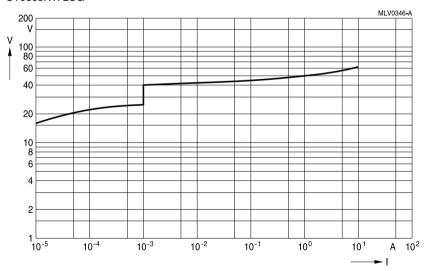

# V/I characteristics

### CT0805K17LCG

CA04P2S17TLCG

# Low capacitance series

# **SMD**

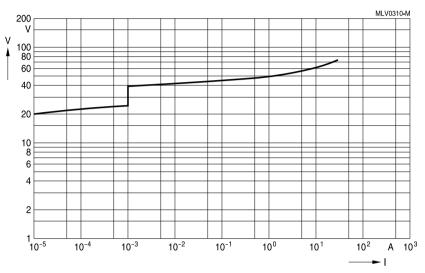

### V/I characteristics

CA06P4S17TLCG

### Low capacitance series

# **SMD**

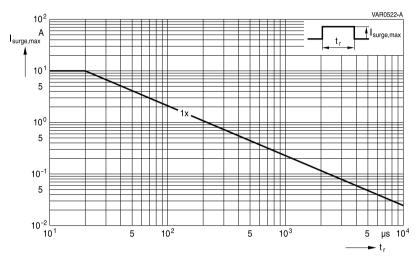

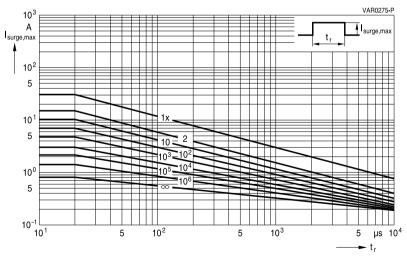

### **Derating curves**

Maximum surge current  $I_{surge,max} = f(t_r, pulse train)$

For explanation of the derating curves refer to "General technical information", chapter 2.7.2

### CT0603K17LCG

### CA04P2S17TLCG

CT0603S17ALCG CT0805K17LCG CA06P4S17TLCG

### Low capacitance series

# **SMD**

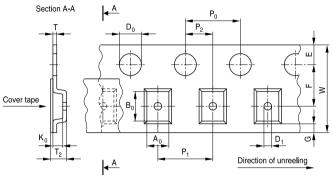

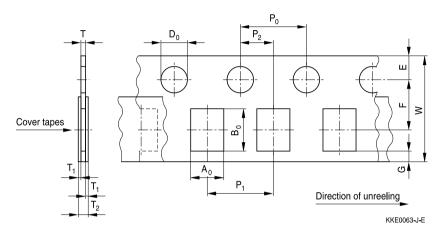

### Taping and packing

# 1 Taping and packing for SMD components

# 1.1 Blister tape (the taping to IEC 60286-3)

KKE0053-C-E

### **Dimensions in mm**

| -              |               | 8-mm tape           |               |               |               |               |                        | 16-mm tape |                 |                     |

|----------------|---------------|---------------------|---------------|---------------|---------------|---------------|------------------------|------------|-----------------|---------------------|

|                |               | Case size (inch/mm) |               |               |               |               | Case size<br>(inch/mm) |            | e size<br>ı/mm) | Tolerance           |

|                |               |                     | 0508/<br>1220 | 0612/<br>1632 | 1012/<br>2532 |               |                        |            |                 |                     |

|                | 0603/<br>1608 | 0506/<br>1216       | 0805/<br>2012 | 1206/<br>3216 | 1210/<br>3225 | 1812/<br>4532 | 2220/<br>5750          | 3225       | 4032            |                     |

| $A_0$          | 0.9 ±0.10     | 1.50                | 1.60          | 1.90          | 2.80          | 3.50          | 5.10                   | 7.00       | 8.60            | ±0.20               |

| B <sub>0</sub> | 1.75 ±0.10    | 1.80                | 2.40          | 3.50          | 3.50          | 4.80          | 6.00                   | 8.70       | 10.60           | ±0.20               |

| K <sub>0</sub> | 1.0           | 0.80                |               | 1.80          |               |               | 2.60                   |            | 00              | max.                |

| Т              |               |                     | 0.30          |               |               | 0.            | 30                     | 0.         | 30              | max.                |

| T <sub>2</sub> | 1.3           | 1.20                | 2.            | 50            |               | 3.            | 50                     | 5.         | 50              | max.                |

| D <sub>0</sub> |               |                     | 1.50          |               |               | 1.            | 50                     | 1.         | 50              | +0.10/-0            |

| $D_1$          |               |                     | 1.00          |               |               | 1.            | 50                     | 1.         | 50              | min.                |

| Po             |               |                     | 4.00          |               |               | 4.            | 00                     | 4.         | 00              | ±0.10 <sup>1)</sup> |

| $P_2$          |               |                     | 2.00          |               |               | 2.00          |                        | 2.         | 00              | ±0.05               |

| $P_1$          | 4.00          |                     |               |               | 8.00          |               | 12                     | .00        | ±0.10           |                     |

| W              | 8.00          |                     |               |               | 12            | .00           | 16                     | .00        | ±0.30           |                     |

| E              | 1.75          |                     |               |               | 1.            | 75            | 1.                     | 75         | ±0.10           |                     |

| F              |               |                     | 3.50          |               |               | 5.            | 50                     | 7.         | 50              | ±0.05               |

| G              |               |                     | 0.75          |               |               | 0.            | 75                     | 0.         | 75              | min.                |

<sup>1) ≤±0.2</sup> mm over 10 sprocket holes.

### Low capacitance series

# **SMD**

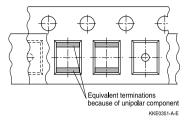

### Part orientation in tape pocket for blister tape

For discrete chip, case sizes 0603, 0805, 1206, 1210, 1812 and 2220

For array, case sizes 0612

For arrays 0506 and 1012

### For filter array, case size 0508

### Additional taping information

| Reel material             | Polystyrol (PS)                                                                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------|

| Tape material             | Polystyrol (PS) or Polycarbonat (PC) or PVC                                                                 |

| Tape break force          | min. 10 N                                                                                                   |

| Top cover tape strength   | min. 10 N                                                                                                   |

| Top cover tape peel force | 0.2 to 0.6 N for 8-mm tape and 0.2 to 0.8 N for 12-mm tape at a peel speed of 300 mm/min                    |

| Tape peel angle           | Angle between top cover tape and the direction of feed during peel off: 165° to 180°                        |

| Cavity play               | Each part rests in the cavity so that the angle between the part and cavity center line is no more than 20° |

### Low capacitance series

# **SMD**

# 1.2 Cardboard tape (taping to IEC 60286-3)

### Dimensions in mm

|                | 8-mm tape  |           |                |           |           |                     |                     |  |

|----------------|------------|-----------|----------------|-----------|-----------|---------------------|---------------------|--|

|                |            | Cas       | e size (inch/r | nm)       |           | Case size (inch/mm) | Tolerance           |  |

|                | 0201/0603  | 0402/1005 | 0405/1012      | 0603/1608 | 1003/2508 | 0508/1220           |                     |  |

| $A_0$          | 0.38 ±0.05 | 0.60      | 1.05           | 0.95      | 1.00      | 1.60                | ±0.20               |  |

| B <sub>0</sub> | 0.68 ±0.05 | 1.15      | 1.60           | 1.80      | 2.85      | 2.40                | ±0.20               |  |

| Т              | 0.35 ±0.02 | 0.60      | 0.75           | 0.95      | 1.00      | 0.95                | max.                |  |

| T <sub>2</sub> | 0.4 min.   | 0.70      | 0.90           | 1.10      | 1.10      | 1.12                | max.                |  |

| $D_0$          | 1.50 ±0.1  |           | 1.             | 50        |           | 1.50                | +0.10/-0            |  |

| P <sub>0</sub> |            |           | 4.             | 00        |           |                     | ±0.10 <sup>2)</sup> |  |

| $P_2$          |            |           | 2.             | 00        |           |                     | ±0.05               |  |

| P <sub>1</sub> | 2.00 ±0.05 | 2.00      | 4.00           | 4.00      | 4.00      | 4.00                | ±0.10               |  |

| W              | 8.00       |           |                |           |           |                     |                     |  |

| E              | 1.75       |           |                |           |           |                     |                     |  |

| F              |            | •         | 3.             | 50        | •         |                     | ±0.05               |  |

| G              | 1.35       |           |                | 0.75      | •         |                     | min.                |  |

<sup>2) ≤0.2</sup> mm over 10 sprocket holes.

### Low capacitance series

# **SMD**

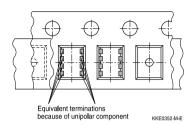

# Part orientation in tape pocket for cardboard tape

For discrete chip case sizes 0201, 0402, 0603 and 1003

# For array case size 0405

### For array case size 0508

## For filter array, case size 0405

# Additional taping information

| Reel material             | Polystyrol (PS)                                                                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------|

| Tape material             | Cardboard                                                                                                   |

| Tape break force          | min. 10 N                                                                                                   |

| Top cover tape strength   | min. 10 N                                                                                                   |

| Top cover tape peel force | 0.1 to 0.65 N at a peel speed of 300 mm/min                                                                 |

| Tape peel angle           | Angle between top cover tape and the direction of feed during peel off: 165° to 180°                        |

| Cavity play               | Each part rests in the cavity so that the angle between the part and cavity center line is no more than 20° |

### Low capacitance series

# **SMD**

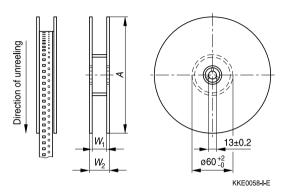

### 1.3 Reel packing

### Dimensions in mm

|                | 8-mm tape   |             | 12-mm tape   |              | 16-mm tape   |

|----------------|-------------|-------------|--------------|--------------|--------------|

|                | 180-mm reel | 330-mm reel | 180-mm reel  | 330-mm reel  | 330-mm reel  |

| A              | 180 -3/+0   | 330 -2.0    | 180 -3/+0    | 330 -2.0     | 330 -2.0     |

| W <sub>1</sub> | 8.4 +1.5/-0 | 8.4 +1.5/-0 | 12.4 +1.5/-0 | 12.4 +1.5/-0 | 16.4 +1.5/-0 |

| $W_2$          | 14.4 max.   | 14.4 max.   | 18.4 max.    | 18.4 max.    | 22.4 max.    |

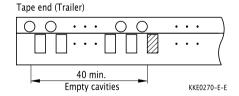

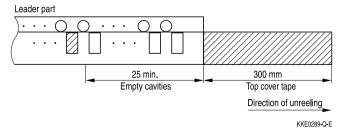

# Leader, trailer

# Low capacitance series

# **SMD**

# 1.4 Packing units for discrete chip and array chip

|           | th             |                |              | 180 mm        | 330 mm        |

|-----------|----------------|----------------|--------------|---------------|---------------|

| Case size | Chip thickness | Cardboard tape | Blister tape | Ø 180-mm reel | Ø 330-mm reel |

| inch/mm   | th             | W              | W            | pcs.          | pcs.          |

| 0201/0603 | 0.33 mm        | 8 mm           | _            | 15000         | _             |

| 0402/1005 | 0.6 mm         | 8 mm           | _            | 10000         | _             |

| 0405/1012 | 0.7 mm         | 8 mm           | _            | 5000          | _             |

| 0506/1216 | 0.5 mm         | _              | 8 mm         | 4000          | _             |

| 0508/1220 | 0.9 mm         | 8 mm           | 8 mm         | 4000          | _             |

| 0603/1608 | 0.9 mm         | 8 mm           | 8 mm         | 4000          | 16000         |

| 0612/1632 | 0.9 mm         | _              | 8 mm         | 3000          | _             |

| 0805/2012 | 0.7 mm         | _              | 8 mm         | 3000          | _             |

|           | 0.9 mm         | _              | 8 mm         | 3000          | 12000         |

|           | 1.3 mm         | _              | 8 mm         | 3000          | _             |

| 1003/2508 | 0.9 mm         | 8 mm           | _            | 4000          | _             |

| 1012/2532 | 1.0 mm         | _              | 8 mm         | 2000          | _             |

| 1206/3216 | 0.9 mm         | _              | 8 mm         | 3000          | _             |

|           | 1.3 mm         | _              | 8 mm         | 3000          | _             |

|           | 1.4 mm         | _              | 8 mm         | 2000          | _             |

|           | 1.6 mm         | _              | 8 mm         | 2000          | _             |

| 1210/3225 | 0.9 mm         | _              | 8 mm         | 3000          | _             |

|           | 1.3 mm         | _              | 8 mm         | 3000          | _             |

|           | 1.4 mm         | _              | 8 mm         | 2000          | _             |

|           | 1.6 mm         | _              | 8 mm         | 2000          | _             |

| 1812/4532 | 1.3 mm         | _              | 12 mm        | 1500          | _             |

|           | 1.4 mm         | _              | 12 mm        | 1000          | _             |

|           | 1.6 mm         | _              | 12 mm        | _             | 4000          |

|           | 2.3 mm         | _              | 12 mm        | _             | 3000          |

| 2220/5750 | 1.3 mm         | _              | 12 mm        | 1500          | _             |

|           | 1.4 mm         | _              | 12 mm        | 1000          | _             |

|           | 2.0 mm         | _              | 12 mm        | _             | 3000          |

|           | 2.3 mm         | -              | 12 mm        | _             | 3000          |

| 3225      | 3.2 mm         | _              | 16 mm        | _             | 1000          |

|           | 4.5 mm         | _              | 16 mm        | _             | 1000          |

| 4032      | 3.2 mm         | _              | 16 mm        | _             | 1000          |

|           | 4.5 mm         | _              | 16 mm        | _             | 1000          |

### Low capacitance series

# **SMD**

## 2 Delivery mode for leaded SHCV varistors

Standard delivery mode for SHCV types is bulk. Alternative taping modes (AMMO pack or taped on reel) are available upon request.

Packing units for:

| Type      | Pieces |

|-----------|--------|

| SR6       | 2000   |

| SR1 / SR2 | 1000   |

For types not listed in this data book please contact EPCOS.

### Low capacitance series

**SMD**

### Soldering directions

### 1 Terminations

### 1.1 Nickel barrier termination

The nickel barrier layer of the silver/nickel/tin termination prevents leaching of the silver base metallization layer. This allows great flexibility in the selection of soldering parameters. The tin prevents the nickel layer from oxidizing and thus ensures better wetting by the solder. The nickel barrier termination is suitable for all commonly-used soldering methods.

KKE0484-W-E

Multilayer CTVS: Structure of nickel barrier termination

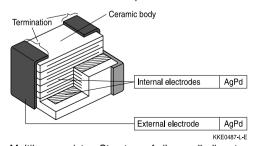

### 1.2 Silver-palladium termination

Silver-palladium terminations are used for the large case sizes 1812 and 2220 and for chips intended for conductive adhesion. This metallization improves the resistance of large chips to thermal shock.

In case of conductive adhesion, the silver-palladium metallization reduces susceptibility to corrosion. Silver-palladium termination can be used for smaller case sizes (only chip) for hybrid applications as well. The silver-palladium termination is not approved for lead-free soldering.

Multilayer varistor: Structure of silver-palladium termination

### Low capacitance series

### **SMD**

### 1.3 Silver-platinum termination

Silver-platinum terminations are mainly used for the large case sizes 1812 and 2220. The silver-platinum termination is approved for reflow soldering, SnPb soldering and lead-free soldering with a silver containing solder paste. In case of SnPb soldering, a solder paste Sn62Pb36Ag2 is recommended. For lead-free reflow soldering, a solder paste SAC, e.g. Sn95.5Ag3.8Cu0.7, is recommended.

Multilayer varistor: Structure of silver-platinum termination

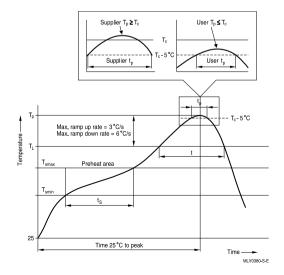

# 2 Recommended soldering temperature profiles

### 2.1 Reflow soldering temperature profile

Recommended temperature characteristic for reflow soldering following JEDEC J-STD-020D

### Low capacitance series

# **SMD**

| Profile feature                                                               |                                        | Sn-Pb eutectic assembly     | Pb-free assembly            |

|-------------------------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------------|

| Preheat and soak                                                              |                                        |                             |                             |

| - Temperature min                                                             | T <sub>smin</sub>                      | 100 °C                      | 150 °C                      |

| - Temperature max                                                             | $T_{\text{smax}}$                      | 150 °C                      | 200 °C                      |

| - Time                                                                        | $t_{\text{smin}}$ to $t_{\text{smax}}$ | 60 120 s                    | 60 180 s                    |

| Average ramp-up rate                                                          | $T_{\text{smax}}$ to $T_{\text{p}}$    | 3 °C/ s max.                | 3 °C/ s max.                |

| Liquidous temperature                                                         | T <sub>L</sub>                         | 183 °C                      | 217 °C                      |

| Time at liquidous                                                             | t <sub>L</sub>                         | 60 150 s                    | 60 150 s                    |

| Peak package body temperature                                                 | T <sub>p</sub> <sup>1)</sup>           | 220 °C 235 °C <sup>2)</sup> | 245 °C 260 °C <sup>2)</sup> |

| Time $(t_P)^{3)}$ within 5 °C of specified classification temperature $(T_c)$ |                                        | 20 s <sup>3)</sup>          | 30 s <sup>3)</sup>          |

| Average ramp-down rate                                                        | T <sub>p</sub> to T <sub>smax</sub>    | 6 °C/ s max.                | 6 °C/ s max.                |

| Time 25 °C to peak temperature                                                |                                        | maximum 6 min               | maximum 8 min               |

<sup>1)</sup> Tolerance for peak profile temperature (T<sub>P</sub>) is defined as a supplier minimum and a user maximum.

**Note:** All temperatures refer to topside of the package, measured on the package body surface. Number of reflow cycles: 3

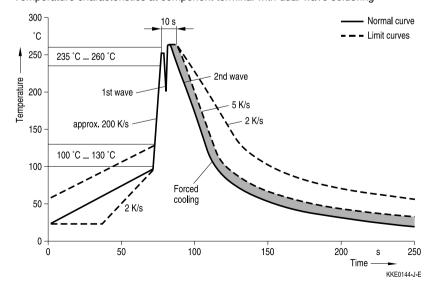

# 2.2 Wave soldering temperature profile

Temperature characteristics at component terminal with dual-wave soldering

Page 21 of 34

<sup>2)</sup> Depending on package thickness. For details please refer to JEDEC J-STD-020D.

<sup>3)</sup> Tolerance for time at peak profile temperature (t<sub>P</sub>) is defined as a supplier minimum and a user maximum.

### Low capacitance series

### **SMD**

### 2.3 Lead-free soldering processes

EPCOS multilayer CTVS with AgNiSn termination are designed for the requirements of lead-free soldering processes only.

Soldering temperature profiles to JEDEC J-STD-020D, IEC 60068-2-58 and ZVEI recommendations

### 3 Recommended soldering methods - type-specific releases by EPCOS

### 3.1 Overview

|                 |            | Reflow soldering |           | Wave soldering |           |

|-----------------|------------|------------------|-----------|----------------|-----------|

| Туре            | Case size  | SnPb             | Lead-free | SnPb           | Lead-free |

| CT / CD         | 0201/ 0402 | Approved         | Approved  | No             | No        |

| CT / CD         | 0603 2220  | Approved         | Approved  | Approved       | Approved  |

| CN              | 0603 2220  | Approved         | No        | Approved       | No        |

| CNK2            | 1812, 2220 | Approved         | Approved  | No             | No        |

| Arrays          | 0405 1012  | Approved         | Approved  | No             | No        |

| ESD/EMI filters | 0405, 0508 | Approved         | Approved  | No             | No        |

| CU              | 3225, 4032 | Approved         | Approved  | Approved       | Approved  |

| SHCV            | =          | No               | No        | Approved       | Approved  |

### 3.2 Nickel barrier and AgPt terminated multilayer CTVS

All EPCOS MLVs with nickel barrier and AgPt termination are suitable and fully qualiyfied for lead-free soldering. The nickel barrier layer is 100% matte tin-plated.

### 3.3 Silver-palladium terminated MLVs

AgPd-terminated MLVs are mainly designed for conductive adhesion technology on hybrid material. Additionally MLVs with AgPd termination are suitable for reflow and wave soldering with SnPb solder.

### Note:

Lead-free soldering is not approved for MLVs with AgPd termination.

### 3.4 Silver-platinum terminated MLVs

The silver-platinum termination is approved for reflow soldering, SnPb soldering and lead-free with a silver containing solder paste. In case of SnPb soldering, a solder paste Sn62Pb36Ag2 is recommended. For lead-free reflow soldering, a solder paste SAC, e.g. Sn95.5Ag3.8Cu0.7, is recommended.

### Low capacitance series

### **SMD**

### 3.5 Tinned copper alloy

All EPCOS CU types with tinned termination are approved for lead-free and SnPb soldering.

### 3.6 Tinned iron wire

All EPCOS SHCV types with tinned termination are approved for lead-free and SnPb soldering.

### 4 Solder joint profiles / solder quantity

### 4.1 Nickel barrier termination

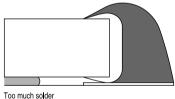

If the meniscus height is too low, that means the solder quantity is too low, the solder joint may break, i.e. the component becomes detached from the joint. This problem is sometimes interpreted as leaching of the external terminations.

If the solder meniscus is too high, i.e. the solder quantity is too large, the vise effect may occur. As the solder cools down, the solder contracts in the direction of the component. If there is too much solder on the component, it has no leeway to evade the stress and may break, as in a vise.

The figures below show good and poor solder joints for dual-wave and infrared soldering.

### 4.1.1 Solder joint profiles for nickel barrier termination - dual-wave soldering

Pad geometry too large, not soldered in preferred direction

KKE0288-H-E

Good and poor solder joints caused by amount of solder in dual-wave soldering.

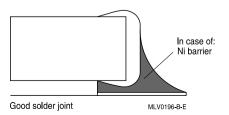

# 4.1.2 Solder joint profiles for nickel barrier termination / silver-palladium / silver-platinum termination - reflow soldering

Too much solder Pad geometry too large

KKE0071-A-E

# Multilayer varistors (MLVs) Low capacitance series In case of: AgPd/AgPt Ni-Barrier

Good solder joint

KKE0070-2-E

Good and poor solder joints caused by amount of solder in reflow soldering.

KKE0072-I-E

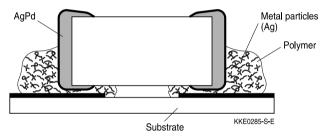

### 5 Conductive adhesion

Poor wetting

Attaching surface-mounted devices (SMDs) with electrically conductive adhesives is a commercially attractive method of component connection to supplement or even replace conventional soldering methods.

Electrically conductive adhesives consist of a non-conductive plastic (epoxy resin, polyimide or silicon) in which electrically conductive metal particles (gold, silver, palladium, nickel, etc) are embedded. Electrical conduction is effected by contact between the metal particles.

Adhesion is particularly suitable for meeting the demands of hybrid technology. The adhesives can be deposited ready for production requirements by screen printing, stamping or by dispensers. As shown in the following table, conductive adhesion involves two work operations fewer than soldering.

| Reflow soldering          | Wave soldering | Conductive adhesion              |

|---------------------------|----------------|----------------------------------|

| Screen-print solder paste | Apply glue dot | Screen-print conductive adhesive |

| Mount SMD                 | Mount SMD      | Mount SMD                        |

| Predry solder paste       | Cure glue      | Cure adhesive                    |

| Reflow soldering          | Wave soldering | Inspect                          |

| Wash                      | Wash           |                                  |

| Inspect                   | Inspect        |                                  |

### Low capacitance series

### **SMD**

A further advantage of adhesion is that the components are subjected to virtually no temperature shock at all. The curing temperatures of the adhesives are between 120 °C and 180 °C, typical curing times are between 30 minutes and one hour.

The bending strength of glued chips is, in comparison with that of soldered chips, higher by a factor of at least 2, as is to be expected due to the elasticity of the glued joints.

The lower conductivity of conductive adhesive may lead to higher contact resistance and thus result in electrical data different to those of soldered components. Users must pay special attention to this in RF applications.

### 6 Solderability tests

| Test                                                                                  | Standard          | Test conditions<br>Sn-Pb soldering                                                                      | Test conditions Pb-free soldering                                                                                  | Criteria/ test results                                                                |

|---------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Wettability                                                                           | IEC<br>60068-2-58 | Immersion in 60/40 SnPb solder using non-activated flux at 215 $\pm$ 3 °C for 3 $\pm$ 0.3 s             | Immersion in Sn96.5Ag3.0Cu0.5 solder using non- or low activated flux at $245 \pm 5$ °C for $3 \pm 0.3$ s          | Covering of 95% of<br>end termination,<br>checked by visual<br>inspection             |

| Leaching resistance                                                                   | IEC<br>60068-2-58 | Immersion in 60/40 SnPb solder using mildly activated flux without preheating at 260 ± 5 °C for 10 ±1 s | Immersion in Sn96.5Ag3.0Cu0.5 solder using non- or low activated flux without preheating at 255 ± 5 °C for 10 ±1 s | No leaching of contacts                                                               |

| Thermal shock<br>(solder shock)                                                       |                   | Dip soldering at 300 °C/5 s                                                                             | Dip soldering at 300 °C/5 s                                                                                        | No deterioration of electrical parameters. Capacitance change: ≤ ±15%                 |

| Tests of resistance to soldering heat for SMDs                                        | IEC<br>60068-2-58 | Immersion in<br>60/40 SnPb for 10 s<br>at 260 °C                                                        | Immersion in<br>Sn96.5Ag3.0Cu0.5<br>for 10 s at 260 °C                                                             | Change of varistor voltage: ≤ ±5%                                                     |

| Tests of resistance<br>to soldering heat<br>for radial leaded<br>components<br>(SHCV) | IEC<br>60068-2-20 | Immersion<br>of leads in<br>60/40 SnPb<br>for 10 s at 260 °C                                            | Immersion<br>of leads in<br>Sn96.5Ag3.0Cu0.5<br>for 10 s at 260 °C                                                 | Change of varistor voltage: $\leq \pm 5\%$ Change of capacitance X7R: $\leq -5/+10\%$ |

### Low capacitance series

**SMD**

### Note:

### Leaching of the termination

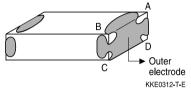

Effective area at the termination might be lost if the soldering temperature and/or immersion time are not kept within the recommended conditions. Leaching of the outer electrode should not exceed 25% of the chip end area (full length of the edge A-B-C-D) and 25% of the length A-B, shown below as mounted on substrate.

As a single chip

As mounted on substrate

### 7 Notes for proper soldering

### 7.1 Preheating and cooling

According to JEDEC J-STD-020D. Please refer to chapter 2.

### 7.2 Repair / rework

Manual soldering with a soldering iron must be avoided, hot-air methods are recommended for rework purposes.

### 7.3 Cleaning

All environmentally compatible agents are suitable for cleaning. Select the appropriate cleaning solution according to the type of flux used. The temperature difference between the components and cleaning liquid must not be greater than 100 °C. Ultrasonic cleaning should be carried out with the utmost caution. Too high ultrasonic power can impair the adhesive strength of the metallized surfaces.

### 7.4 Solder paste printing (reflow soldering)

An excessive application of solder paste results in too high a solder fillet, thus making the chip more susceptible to mechanical and thermal stress. Too little solder paste reduces the adhesive strength on the outer electrodes and thus weakens the bonding to the PCB. The solder should be applied smoothly to the end surface.

### Low capacitance series

### **SMD**

### 7.5 Adhesive application

Thin or insufficient adhesive causes chips to loosen or become disconnected during curing. Low viscosity of the adhesive causes chips to slip after mounting. It is advised to consult the manufacturer of the adhesive on proper usage and amounts of adhesive to use.

### 7.6 Selection of flux

Used flux should have less than or equal to 0.1 wt % of halogenated content, since flux residue after soldering could lead to corrosion of the termination and/or increased leakage current on the surface of the component. Strong acidic flux must not be used. The amount of flux applied should be carefully controlled, since an excess may generate flux gas, which in turn is detrimental to solderability.

### 7.7 Storage of CTVSs

Solderability is guaranteed for one year from date of delivery for multilayer varistors, CeraDiodes and ESD/EMI filters (half a year for chips with AgPd and AgPt terminations) and two years for SHCV and CU components, provided that components are stored in their original packages.

Storage temperature: -25 °C to +45 °C

Relative humidity: ≤75% annual average, ≤95% on 30 days a year

The solderability of the external electrodes may deteriorate if SMDs and leaded components are stored where they are exposed to high humidity, dust or harmful gas (hydrogen chloride, sulfurous acid gas or hydrogen sulfide).

Do not store SMDs and leaded components where they are exposed to heat or direct sunlight. Otherwise the packing material may be deformed or SMDs/ leaded components may stick together, causing problems during mounting.

After opening the factory seals, such as polyvinyl-sealed packages, it is recommended to use the SMDs or leaded components as soon as possible.

### 7.8 Placement of components on circuit board

Especially in the case of dual-wave soldering, it is of advantage to place the components on the board before soldering in that way that their two terminals do not enter the solder bath at different times.

Ideally, both terminals should be wetted simultaneously.

### 7.9 Soldering cautions

- An excessively long soldering time or high soldering temperature results in leaching of the outer electrodes, causing poor adhesion and a change of electrical properties of the varistor due to the loss of contact between electrodes and termination.

- Wave soldering must not be applied for MLVs designated for reflow soldering only.

- Keep the recommended down-cooling rate.

# Low capacitance series

# **SMD**

### 7.10 Standards

CECC 00802

IEC 60068-2-58

IEC 60068-2-20

JEDEC J-STD-020D

# Low capacitance series

# **SMD**

# Symbols and terms

| Symbol                           | Term                                                       |

|----------------------------------|------------------------------------------------------------|

| C <sub>line,typ</sub>            | Typical capacitance per line                               |

| $C_{\text{max}}$                 | Maximum capacitance                                        |

| $C_{min}$                        | Minimum capacitance                                        |

| $C_{nom}$                        | Nominal capacitance                                        |

| $\Delta \textbf{C}_{\text{nom}}$ | Tolerance of nominal capacitance                           |

| $C_{typ}$                        | Typical capacitance                                        |

| $f_{\text{cut-off,min}}$         | Minimum cut-off frequency                                  |

| 1                                | Current                                                    |

| I <sub>clamp</sub>               | Clamping current                                           |

| l <sub>leak</sub>                | Leakage current                                            |

| I <sub>leak,typ</sub>            | Typical leakage current                                    |

| $I_{PP}$                         | Peak pulse current                                         |

| I <sub>surge,max</sub>           | Maximum surge current (also termed peak current)           |

| LCT                              | Lower category temperature                                 |

| $L_{typ}$                        | Typical inductance                                         |

| $P_{diss,max}$                   | Maximum power dissipation                                  |

| $P_{PP}$                         | Peak pulse power                                           |

| $R_{\text{ins}}$                 | Insulation resistance                                      |

| $R_{min}$                        | Minimum resistance                                         |

| $R_s$                            | Resistance per line                                        |

| $T_A$                            | Ambient temperature                                        |

| $T_op$                           | Operating temperature                                      |

| $T_{stg}$                        | Storage temperature                                        |

| t <sub>r</sub>                   | Duration of equivalent rectangular wave                    |

| $t_{resp}$                       | Response time                                              |

| UCT                              | Upper category temperature                                 |

| V                                | Voltage                                                    |

| $V_{BR,min}$                     | Minimum breakdown voltage                                  |

| $V_{\text{clamp,max}}$           | Maximum clamping voltage                                   |

| $V_{\text{DC,max}}$              | Maximum DC operating voltage (also termed working voltage) |

| $V_{ESD,air}$                    | Air discharge ESD capability                               |

| $V_{ESD,contact}$                | Contact discharge ESD capability                           |

| $V_{\text{jump}}$                | Maximum jump start voltage                                 |

# Low capacitance series

# **SMD**

| $V_{RMS,max}$         | Maximum AC operating voltage, root-mean-square value     |

|-----------------------|----------------------------------------------------------|

| $V_{v}$               | Varistor voltage (also termed breakdown voltage)         |

| $V_{v,min}$           | Minimum varistor voltage                                 |

| $V_{v,max}$           | Maximum varistor voltage                                 |

| $\Delta V_{\text{V}}$ | Tolerance of varistor voltage                            |

| $W_{LD}$              | Maximum load dump                                        |

| $W_{\text{max}}$      | Maximum energy absorption (also termed transient energy) |

| $lpha_{typ}$          | Typical insertion loss                                   |

| е                     | Lead spacing                                             |

| <b>≪*</b> ≫           | Maximum possible application conditions                  |

All dimensions are given in mm.

The commas used in numerical values denote decimal points.

### Low capacitance series

### **SMD**

### Cautions and warnings

### General

Some parts of this publication contain statements about the suitability of our ceramic transient voltage suppressor (CTVS) components (multilayer varistors (MLVs), CeraDiodes, ESD/EMI filters, SMD disk varistors (CU types), leaded transient voltage/ RFI suppressors (SHCV types)) for certain areas of application, including recommendations about incorporation/design-in of these products into customer applications. The statements are based on our knowledge of typical requirements often made of our CTVS devices in the particular areas. We nevertheless expressly point out that such statements cannot be regarded as binding statements about the suitability of our CTVS components for a particular customer application. As a rule, EPCOS is either unfamiliar with individual customer applications or less familiar with them than the customers themselves. For these reasons, it is always incumbent on the customer to check and decide whether the CTVS devices with the properties described in the product specification are suitable for use in a particular customer application.

- Do not use EPCOS CTVS components for purposes not identified in our specifications, application notes and data books.

- Ensure the suitability of a CTVS in particular by testing it for reliability during design-in. Always evaluate a CTVS component under worst-case conditions.

- Pay special attention to the reliability of CTVS devices intended for use in safety-critical applications (e.g. medical equipment, automotive, spacecraft, nuclear power plant).

### **Design notes**

- Always connect a CTVS in parallel with the electronic circuit to be protected.

- Consider maximum rated power dissipation if a CTVS has insufficient time to cool down between a number of pulses occurring within a specified isolated time period. Ensure that electrical characteristics do not degrade.

- Consider derating at higher operating temperatures. Choose the highest voltage class compatible with derating at higher temperatures.

- Surge currents beyond specified values will puncture a CTVS. In extreme cases a CTVS will burst

- If steep surge current edges are to be expected, make sure your design is as low-inductance as possible.

- In some cases the malfunctioning of passive electronic components or failure before the end of their service life cannot be completely ruled out in the current state of the art, even if they are operated as specified. In applications requiring a very high level of operational safety and especially when the malfunction or failure of a passive electronic component could endanger human life or health (e.g. in accident prevention, life-saving systems, or automotive battery line applications such as clamp 30), ensure by suitable design of the application or other measures (e.g. installation of protective circuitry or redundancy) that no injury or damage is sustained by third parties in the event of such a malfunction or failure. Only use CTVS components from the automotive series in safety-relevant applications.

### Low capacitance series

### **SMD**

Specified values only apply to CTVS components that have not been subject to prior electrical, mechanical or thermal damage. The use of CTVS devices in line-to-ground applications is therefore not advisable, and it is only allowed together with safety countermeasures like thermal fuses.

### Storage

- Only store CTVS in their original packaging. Do not open the package before storage.

- Storage conditions in original packaging: temperature −25 to +45°C, relative humidity ≤75% annual average, maximum 95%, dew precipitation is inadmissible.

- Do not store CTVS devices where they are exposed to heat or direct sunlight. Otherwise the packaging material may be deformed or CTVS may stick together, causing problems during mounting.

- Avoid contamination of the CTVS surface during storage, handling and processing.

- Avoid storing CTVS devices in harmful environments where they are exposed to corrosive gases for example (SO<sub>x</sub>, CI).

- Use CTVS as soon as possible after opening factory seals such as polyvinyl-sealed packages.

- Solder CTVS components after shipment from EPCOS within the time specified:

- CTVS with Ni barrier termination, 12 months

- CTVS with AgPd and AgPt termination, 6 months

- SHCV and CU series, 24 months

### Handling

- Do not drop CTVS components and allow them to be chipped.

- Do not touch CTVS with your bare hands gloves are recommended.

- Avoid contamination of the CTVS surface during handling.

# Mounting

- When CTVS devices are encapsulated with sealing material or overmolded with plastic material, electrical characteristics might be degraded and the life time reduced.

- Make sure an electrode is not scratched before, during or after the mounting process.

- Make sure contacts and housings used for assembly with CTVS components are clean before mounting.

- The surface temperature of an operating CTVS can be higher. Ensure that adjacent components are placed at a sufficient distance from a CTVS to allow proper cooling.

- Avoid contamination of the CTVS surface during processing.

- Multilayer varistors (MLVs) with AgPd termination are not approved for lead-free soldering.

### Soldering

- Complete removal of flux is recommended to avoid surface contamination that can result in an instable and/or high leakage current.

- Use resin-type or non-activated flux.

- Bear in mind that insufficient preheating may cause ceramic cracks.

- Rapid cooling by dipping in solvent is not recommended, otherwise a component may crack.

### Low capacitance series

### **SMD**

### Conductive adhesive gluing

Only multilayer varistors (MLVs) with an AgPd termination are approved for conductive adhesive gluing.

### Operation

- Use CTVS only within the specified operating temperature range.

- Use CTVS only within specified voltage and current ranges.

- Environmental conditions must not harm a CTVS. Only use them in normal atmospheric conditions. Reducing the atmosphere (e.g. hydrogen or nitrogen atmosphere) is prohibited.

- Prevent a CTVS from contacting liquids and solvents. Make sure that no water enters a CTVS (e.g. through plug terminals).

- Avoid dewing and condensation.

- EPCOS CTVS components are mainly designed for encased applications. Under all circumstances avoid exposure to:

- direct sunlight

- rain or condensation

- steam, saline spray

- corrosive gases

- atmosphere with reduced oxygen content

- EPCOS CTVS devices are not suitable for switching applications or voltage stabilization where static power dissipation is required.

- Multilayer varistors (MLVs) are designed for ESD protection and transient suppression. CeraDiodes are designed for ESD protection only, ESD/EMI filters are designed for ESD and EMI protection only.

This listing does not claim to be complete, but merely reflects the experience of EPCOS AG.

### Important notes

The following applies to all products named in this publication:

- 1. Some parts of this publication contain statements about the suitability of our products for certain areas of application. These statements are based on our knowledge of typical requirements that are often placed on our products in the areas of application concerned. We nevertheless expressly point out that such statements cannot be regarded as binding statements about the suitability of our products for a particular customer application. As a rule, EPCOS is either unfamiliar with individual customer applications or less familiar with them than the customers themselves. For these reasons, it is always ultimately incumbent on the customer to check and decide whether an EPCOS product with the properties described in the product specification is suitable for use in a particular customer application.

- 2. We also point out that in individual cases, a malfunction of electronic components or failure before the end of their usual service life cannot be completely ruled out in the current state of the art, even if they are operated as specified. In customer applications requiring a very high level of operational safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health (e.g. in accident prevention or lifesaving systems), it must therefore be ensured by means of suitable design of the customer application or other action taken by the customer (e.g. installation of protective circuitry or redundancy) that no injury or damage is sustained by third parties in the event of malfunction or failure of an electronic component.

- 3. The warnings, cautions and product-specific notes must be observed.

- 4. In order to satisfy certain technical requirements, some of the products described in this publication may contain substances subject to restrictions in certain jurisdictions (e.g. because they are classed as hazardous). Useful information on this will be found in our Material Data Sheets on the Internet (www.epcos.com/material). Should you have any more detailed questions, please contact our sales offices.

- 5. We constantly strive to improve our products. Consequently, the products described in this publication may change from time to time. The same is true of the corresponding product specifications. Please check therefore to what extent product descriptions and specifications contained in this publication are still applicable before or when you place an order. We also reserve the right to discontinue production and delivery of products. Consequently, we cannot guarantee that all products named in this publication will always be available. The aforementioned does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.

- Unless otherwise agreed in individual contracts, all orders are subject to the current version of the "General Terms of Delivery for Products and Services in the Electrical Industry" published by the German Electrical and Electronics Industry Association (ZVEI).

- 7. The trade names EPCOS, BAOKE, Alu-X, CeraDiode, CSMP, CSSP, CTVS, DeltaCap, DigiSiMic, DSSP, FormFit, MiniBlue, MiniCell, MKK, MKD, MLSC, MotorCap, PCC, PhaseCap, PhaseCube, PhaseMod, PhiCap, SIFERRIT, SIFI, SIKOREL, SilverCap, SIMDAD, SiMic, SIMID, SineFormer, SIOV, SIP5D, SIP5K, ThermoFuse, WindCap are trademarks registered or pending in Europe and in other countries. Further information will be found on the Internet at www.epcos.com/trademarks.