Real-time Clock Module (I<sup>2</sup>C Bus)

#### **Features**

- Using external 32.768kHz quartz crystal

- Supports I<sup>2</sup>C-Bus's high speed mode (400 kHz)

- Includes time (Hour/Minute/Second) and calendar (Year/Month/Date/Day) counter functions (BCD code)

- Programmable square wave output signal

- 56-byte, battery-backed, nonvolatile (NV) RAM for data storage

- Automatic power-fail detect and switch circuitry of battery backup

- Consumes less than 500nA in battery backup mode with oscillator running

# **Description**

The PT7C4307 serial real-time clock is a low-power clock/calendar with a programmable square-wave output and 56 bytes of nonvolatile RAM.

Address and data are transferred serially via a 2-wire, bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator.

The PT7C4307 has a built-in power sense circuit that detects power failures and automatically switches to the battery supply.

Table 1 shows the basic functions of PT7C4307. More details are shown in section: overview of functions.

**Table 1.** Basic functions of PT7C4307

| Item |            | Fur              | nction                  | PT7C4307                   |

|------|------------|------------------|-------------------------|----------------------------|

|      |            | Sour             | ce: Crystal: 32.768kHz  | √                          |

| 1    | Oscillator | Osc              | cillator enable/disable | V                          |

|      |            | C                | Oscillator fail detect  | -                          |

|      |            | Time display     | 12-hour                 | V                          |

| 2    | Time       | Time display     | 24-hour                 | V                          |

|      |            |                  | Century bit             | -                          |

| 3    |            | Alarm            | interrupt               | -                          |

| 4    | F          | Programmable squ | are wave output (Hz)    | 1, 4.096k, 8.192k, 32.768k |

| 5    | RAM        |                  |                         | 56×8                       |

| 6    |            | Batter           | y backup                | √                          |

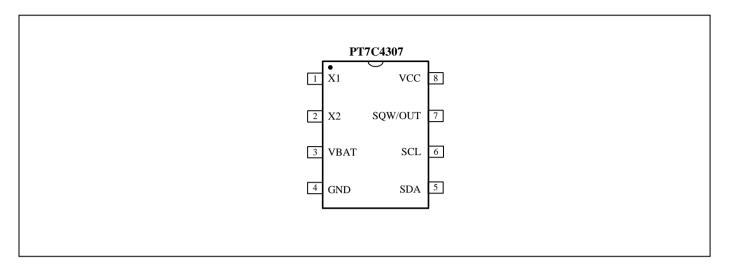

# Pin Assignment

# **Pin Description**

| Pin# | Pin     | Туре | Description                                                                                                                                                               |

|------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | X1      | I    | Oscillator Circuit Input. Together with X2, 32.768kHz crystal is connected between them.                                                                                  |

| 2    | X2      | О    | Oscillator Circuit Output. Together with X1, 32.768kHz crystal is connected between them. When 32.768kHz external input, X2 must be float.                                |

| 6    | SCL     | I    | <b>Serial Clock Input.</b> SCL is used to synchronize data movement on the I <sup>2</sup> C serial interface.                                                             |

| 5    | SDA     | I/O  | <b>Serial Data Input/Output.</b> SDA is the input/output pin for the 2-wire serial interface. The SDA pin is open-drain output and requires an external pull-up resistor. |

| 7    | SQW/OUT | О    | <b>Square Wave/Output Driver.</b> Open drain. Four frequencies selectable: 32.768k, 8.192k, 4.096k, 1Hz when SQWE bit is set to 1.                                        |

| 8    | VCC     | P    | <b>Power.</b> Primary power for PT7C4307.                                                                                                                                 |

| 3    | VBAT    | Р    | +3V Battery Power.                                                                                                                                                        |

| 4    | GND     | Р    | Ground.                                                                                                                                                                   |

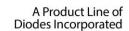

# **Function Block**

**Maximum Ratings**

| 0                                               |                         |

|-------------------------------------------------|-------------------------|

| Storage Temperature                             | -65°Cto +150°C          |

| Ambient Temperature with Power Applied          | -40°Cto +85°C           |

| Supply Voltage to Ground Potential (Vcc to GND) | 0.3V to +6.5V           |

| DC Input (All Other Inputs except Vcc & GND)    | 0.3V to $(V_{cc}+0.3V)$ |

| DC Output Voltage (SDA, /INTA, /INTB pins)      | 0.3V to +6.5V           |

| DC Output Current (FOUT)                        | 0.3V to $(V_{cc}+0.3V)$ |

| Power Dissipation                               | 320mW                   |

|                                                 | (depend on package)     |

|                                                 |                         |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended Operating Conditions**

| Part No. | Symbol    | Description           | Min. | Тур. | Max.                 | Unit |

|----------|-----------|-----------------------|------|------|----------------------|------|

|          | $V_{CC}$  | Power voltage         | 4.5  | 5    | 5.5                  |      |

|          | $V_{BAT}$ | Battery voltage       | 2    | -    | 3.5                  | v    |

| PT7C4307 | $V_{IH}$  | Input high level      | 2.2  | -    | V <sub>CC</sub> +0.3 | V    |

|          | $V_{IL}$  | Input low level       | -0.3 | -    | 0.8                  |      |

|          | $T_A$     | Operating temperature | -40  | -    | 85                   | С    |

# **DC** Electrical Characteristics

Unless otherwise specified,  $V_{DD} = 4.5 \sim 5.5 \text{ V}$ ,  $T_A = -40 \text{ } \text{C}$  to +85 C

| Sym.              | Item                     | Pin                | Condition                   | Min.      | Тур.      | Max.      | Unit     |

|-------------------|--------------------------|--------------------|-----------------------------|-----------|-----------|-----------|----------|

| $V_{CC}$          | Supply voltage           | $V_{CC}$           |                             | 4.5       | 5.0       | 5.5       | V        |

| $V_{BAT}$         | Supply voltage           | $V_{BATT}$         |                             | 2.0       | -         | 3.5       | v        |

| $V_{\mathrm{PF}}$ | Power fail voltage       |                    | Note 4                      | 1.216×    | 1.25×     | 1.284×    | V        |

| ▼ PF              | Tower rain voltage       |                    | Note 4                      | $V_{BAT}$ | $V_{BAT}$ | $V_{BAT}$ |          |

| $I_{CC}$          | Current consumption      | $V_{CC}$           | OSC on, Note 3              | -         | -         | 1.5       | mA       |

| 1CC               | Current consumption      | ▼ CC               | OSC off, Note 1             | -         | -         | 200       | μΑ       |

| $I_{BAT}$         | Current consumption      | $V_{\mathrm{BAT}}$ | OSC on, SQW/OUT off, Note 2 | -         | 300       | 500       | nA       |

| 1BAT              | Current consumption      | V BAT              | OSC on, SQW/OUT on (32kHz)  | -         | 480       | 800       | шА       |

| $V_{\rm IL}$      | Low-level input voltage  | SCL                |                             | -         | -         | 0.8       | V        |

| V <sub>IH</sub>   | High-level input voltage | SCL                |                             | 2.0       | -         | -         | <b>'</b> |

| V <sub>OL</sub>   | Low-level output voltage | SDA                | $I_{OL} = 5 \text{mA}$      | -         | -         | 0.4       | V        |

| $I_{\mathrm{IL}}$ | Input leakage current    | SCL                |                             | -         | -         | 1         | μΑ       |

| $I_{OZ}$          | Output current when OFF  | SDA                |                             | -         | -         | 1         | μΑ       |

#### Note:

- $$\begin{split} V_{CC} &= 5.0 V \text{ and SDA, SCL} = 5.0 V. \\ V_{CC} &= 0 V, \ V_{BAT} = 3 V. \end{split}$$

- SCL clocking at max frequency = 400 kHz. SDA pin open, /EOSC bit = 0 (oscillator enabled)

- $V_{PF}$  measured at  $V_{BAT} = 3.0V$ .

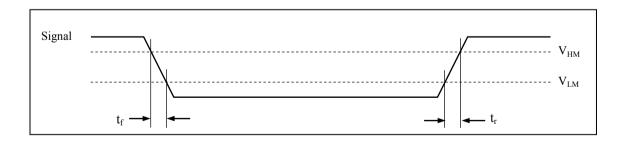

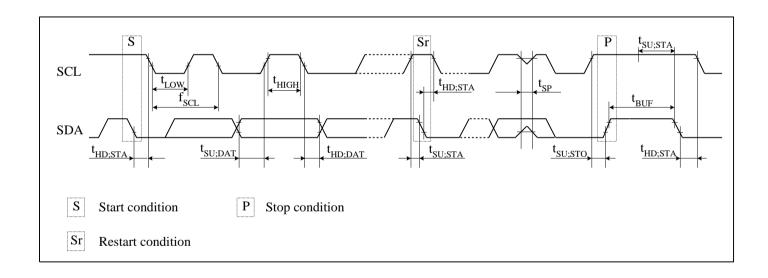

# **AC Electrical Characteristics**

| Sym.         | Description                               | Value                           | Unit |

|--------------|-------------------------------------------|---------------------------------|------|

| $V_{HM}$     | Rising and falling threshold voltage high | $0.8~\mathrm{V_{CC}}$           | V    |

| $V_{\rm HL}$ | Rising and falling threshold voltage low  | $0.2  \mathrm{V}_{\mathrm{CC}}$ | V    |

# A Product Line of Diodes Incorporated

PT7C4307

## Over the operating range

| Symbol                | Item                                             | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------|------|------|------|------|

| $f_{SCL}$             | SCL clock frequency                              | -    | -    | 400  | kHz  |

| $t_{SU;STA}$          | START condition set-up time                      | 0.6  | -    | =    | μs   |

| $t_{\mathrm{HD;STA}}$ | START condition hold time                        | 0.6  | -    | -    | μs   |

| $t_{SU;DAT}$          | Data set-up time (RTC read/write)                | 200  | -    | -    | ns   |

| $t_{\rm HD;DAT1}$     | Data hold time (RTC write)                       | 35   | -    | -    | ns   |

| t <sub>HD;DAT2</sub>  | Data hold time (RTC read)                        | 0    | -    | -    | μs   |

| $t_{\rm SU;STO}$      | STOP condition setup time                        | 0.6  | -    | -    | μs   |

| $t_{\mathrm{BUF}}$    | Bus idle time between a START and STOP condition | 1.3  | -    | -    | μs   |

| $t_{LOW}$             | When SCL = "L"                                   | 1.3  | -    | -    | μs   |

| t <sub>HIGH</sub>     | When SCL = "H"                                   | 0.6  | -    | -    | μs   |

| t <sub>r</sub>        | Rise time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| $t_{\rm f}$           | Fall time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>SP</sub> *     | Allowable spike time on bus                      | -    | -    | 50   | ns   |

| $C_B$                 | Capacitance load for each bus line               | -    | -    | 400  | pF   |

<sup>\*</sup> Note: only reference for design

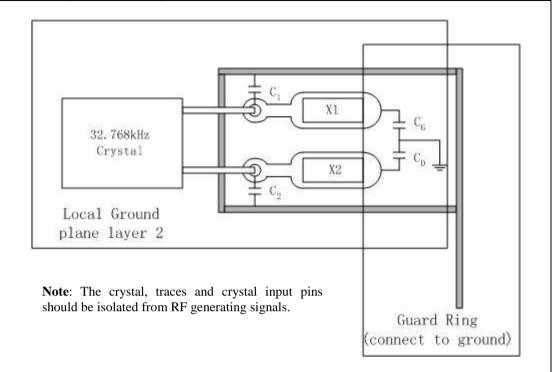

**Recommended Layout for Crystal**

**Built-in Capacitors Specifications and Recommended External Capacitors**

| Parameter            |           | Symbol  | Тур. | Unit |

|----------------------|-----------|---------|------|------|

| Duild in conscitors  | X1 to GND | $C_{G}$ | 20   | pF   |

| Build-in capacitors  | X2 to GND | $C_D$   | 20   | pF   |

| Recommended External | X1 to GND | $C_1$   | 4    | pF   |

| capacitors           | X2 to GND | $C_2$   | 4    | pF   |

**Note**: The frequency of crystal can be optimized by external capacitor  $C_1$  and  $C_2$ , for frequency=32.768Hz,  $C_1$  and  $C_2$  should meet the equation as below:

$Cpar + [(C_1+C_G)*(C_2+C_D)]/[(C_1+C_G)+(C_2+C_D)] = C_L$

Cpar is all parasitical capacitor between X1 and X2.

$C_L$  is crystal's load capacitance.

# **Crystal Specifications**

| Parameter         | Symbol  | Min. | Тур.   | Max. | Unit |

|-------------------|---------|------|--------|------|------|

| Nominal Frequency | $f_{O}$ | =    | 32.768 | ı    | kHz  |

| Series Resistance | ESR     | -    | -      | 70   | kΩ   |

| Load Capacitance  | $C_{L}$ | -    | 12.5   | -    | pF   |

# **Function Description**

#### **Clock function**

CPU can read or write data including the year (last two digits), month, date, day, hour, minute, and second. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2099.

#### Programmable square wave output

A square wave output enable bit controls square wave output at pin 7. 4 frequencies are selectable: 1, 4.096k, 8.192k, 32.768k Hz.

#### Interface with CPU

Data is read and written via the I<sup>2</sup>C bus interface using two signal lines: SCL (clock) and SDA (data).

Since the output of the I/O pin SDA is open drain, a pull-up resistor should be used on the circuit board if the CPU output I/O is also open drain.

The SCL's maximum clock frequency is 400 kHz, which supports the I<sup>2</sup>C bus's high-speed mode.

#### Oscillator enable/disable

Oscillator can be enabled or disabled by /EOSC bit. But time count chain does not shut down when the bit is logic 1.

#### RAM

56×8 nonvolatile RAM are available for customer use.

#### **Registers**

Allocation of registers

| Addr.   | tion of registers        | Register definition |         |              |        |       |       |       |       |

|---------|--------------------------|---------------------|---------|--------------|--------|-------|-------|-------|-------|

| (hex)*1 | Function                 | Bit 7               | Bit 6   | Bit 5        | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 00      | Seconds (00-59)          | /EOSC*2             | S40     | S20          | S10    | S8    | S4    | S2    | S1    |

| 01      | Minutes (00-59)          | 0                   | M40     | M20          | M10    | M8    | M4    | M2    | M1    |

| 02      | Hours (00-23 / 01-12)    | 0                   | 12, /24 | H20 or P, /A | H10    | Н8    | H4    | H2    | H1    |

| 03      | Days of the week (01-07) | 0                   | 0       | 0            | 0      | 0     | W4    | W2    | W1    |

| 04      | Dates (01-31)            | 0                   | 0       | D20          | D10    | D8    | D4    | D2    | D1    |

| 05      | Months (01-12)           | 0                   | 0       | 0            | MO10   | MO8   | MO4   | MO2   | MO1   |

| 06      | Years (00-99)            | Y80                 | Y40     | Y20          | Y10    | Y8    | Y4    | Y2    | Y1    |

| 07      | Control*3                | OUT*4               | 0       | 0            | SQWE*5 | 0     | 0     | RS1*6 | RS0*6 |

| 08~3F   | RAM*7                    | -                   | -       | -            | -      | -     | -     | -     | -     |

#### Caution points:

- \*1. PT7C4307 uses 6 bits for address. That is if write data to 41H, the data will be written to 01H address register.

- \*2. Oscillator Enable bit. When this bit is set to 1, oscillator is stopped but time count chain is still active.

- \*3. Control register was used to select SQW/OUT pin output square wave with one of 4 kinds of frequency or DC level.

- \*4. Control SQW/OUT pin output DC level when square wave is disabled.

- \*5. Square wave outputs enable at SQW/OUT pin.

- \*6. Square wave output frequency select.

- \*7. PT7C4307 has 56×8 static RAM for customer use. It is volatile RAM.

- \*8. All bits marked with "0" are read-only bits. Their value when read is always "0". All bits marked with "-" are customer using space.

## Control and status register

| Addr. (hex) | Description       | D7       | D6     | D5     | D4        | D3     | D2     | D1  | D0  |

|-------------|-------------------|----------|--------|--------|-----------|--------|--------|-----|-----|

| 07          | Control (default) | OUT<br>0 | 0<br>0 | 0<br>0 | SQWE<br>0 | 0<br>0 | 0<br>0 | RS1 | RS0 |

#### • OUT

It controls the output level of the SQW/OUT pin when the square wave output is disabled.

| OUT          | Data | Description                             |

|--------------|------|-----------------------------------------|

| Read / Write | 0    | When SQWE = 0, SQW/OUT pin output low.  |

| Read / Wille | 1    | When SQWE = 0, SQW/OUT pin output high. |

#### • SQWE (Square Wave Enable)

This bit, when set to a logic 1, will enable the oscillator output. The frequency of the square wave output depends upon the value of the RSO and RS1 bits. With the square wave output set to 1Hz, the clock registers update on the falling edge of the square wave.

#### • RS (Rate Select)

These bits control the frequency of the square wave output when the square wave output has been enabled.

| RS1, RS0     | Data | SQW output freq. (Hz) |

|--------------|------|-----------------------|

|              | 00   | 1                     |

| Pand / Write | 01   | 4.096k                |

| Read / Write | 10   | 8.192k                |

|              | 11   | 32.768k Default       |

#### **Time Counter**

Time digit display (in BCD code):

- Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00.

- Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00.

- Hour digits: See description on the /12, 24 bit. Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00.

| Addr. (hex) | Description | D7     | D6        | D5          | D4        | D3        | D2        | D1        | D0        |

|-------------|-------------|--------|-----------|-------------|-----------|-----------|-----------|-----------|-----------|

| 00          | Seconds     | /EOSC* | S40       | S20         | S10       | S8        | S4        | S2        | S1        |

|             | (default)   | 0      | Undefined | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined |

| 01          | Minutes     | 0      | M40       | M20         | M10       | M8        | M4        | M2        | M1        |

| 01          | (default)   | 0      | Undefined | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined |

| 02          | Hours       | 0      | 12, /24   | H20 or P,/A | H10       | Н8        | H4        | H2        | H1        |

| 02          | (default)   | 0      | Undefined | Undefined   | Undefined | Undefined | Undefined | Undefined | Undefined |

<sup>\*</sup> Note: /EOSC bit must be written into 0 to start the time count.

#### • 12, /24 bit

This bit is used to select between 12-hour clock system and 24-hour clock system.

| 12, /24      | Data | Description    |

|--------------|------|----------------|

| Pood / Write | 0    | 24-hour system |

| Read / Write | 1    | 12-hour system |

This bit is used to select between 12-hour clock operation and 24-hour clock operation.

| 12, /24 | Description           | Hours register |               |               |               |  |  |  |  |

|---------|-----------------------|----------------|---------------|---------------|---------------|--|--|--|--|

|         |                       | 24-hour clock  | 12-hour clock | 24-hour clock | 12-hour clock |  |  |  |  |

|         |                       | 00             | 52 ( AM 12 )  | 12            | 72 ( PM 12)   |  |  |  |  |

| 0       | 24 hazzationa diambar | 01             | 41 ( AM 01 )  | 13            | 61 ( PM 01 )  |  |  |  |  |

| U       | 24-hour time display  | 02             | 42 ( AM 02 )  | 14            | 62 ( PM 02 )  |  |  |  |  |

|         |                       | 03             | 43 ( AM 03 )  | 15            | 63 ( PM 03 )  |  |  |  |  |

|         |                       | 04             | 44 ( AM 04 )  | 16            | 64 ( PM 04 )  |  |  |  |  |

|         |                       | 05             | 45 ( AM 05 )  | 17            | 65 ( PM 05 )  |  |  |  |  |

|         |                       | 06             | 46 ( AM 06 )  | 18            | 66 ( PM 06 )  |  |  |  |  |

|         |                       | 07             | 47 ( AM 07 )  | 19            | 67 ( PM 07 )  |  |  |  |  |

| 1       | 12 hove time display  | 08             | 48 ( AM 08 )  | 20            | 68 ( PM 08 )  |  |  |  |  |

| 1       | 12-hour time display  | 09             | 49 ( AM 09 )  | 21            | 69 ( PM 09 )  |  |  |  |  |

|         |                       | 10             | 50 ( AM 10 )  | 22            | 70 ( PM 10 )  |  |  |  |  |

|         |                       | 11             | 51 ( AM 11 )  | 23            | 71 ( PM 11 )  |  |  |  |  |

<sup>\*</sup> Be sure to select between 12-hour and 24-hour clock operation before writing the time data.

### Days of the week Counter

The day counter is a divide-by-7 counter that counts from 01 to 07 and up 07 before starting again from 01. Values that correspond to the day of week are user defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation.

| Addr. (hex) | Description      | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------|------------------|----|----|----|----|----|----|----|----|

|             | - 0.4            |    |    |    |    |    |    |    |    |

| 03          | Days of the week | 0  | 0  | 0  | 0  | 0  | W4 | W2 | W1 |

#### **Calendar Counter**

The data format is BCD format.

• Day digits: Range from 1 to 31 (for January, March, May, July, August, October and December).

Range from 1 to 30 (for April, June, September and November).

Range from 1 to 29 (for February in leap years).

Range from 1 to 28 (for February in ordinary years).

Carried to month digits when cycled to 1.

- Month digits: Range from 1 to 12 and carried to year digits when cycled to 1.

- Year digits: Range from 00 to 99 and 00, 04, 08, ..., 92 and 96 are counted as leap years.

| Addr. | Description | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|-------------|----|----|----|----|----|----|----|----|

| (hex) | Description | D/ | D6 | DS | D4 | טט | D2 | Di | D0 |

| 04 | Dates     | 0         | 0         | D20       | D10       | D8        | D4        | D2        | D1        |

|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 04 | (default) | 0         | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 05 | Months    | 0         | 0         | 0         | M10       | M8        | M4        | M2        | M1        |

| 03 | (default) | 0         | 0         | 0         | Undefined | Undefined | Undefined | Undefined | Undefined |

| 06 | Years     | Y80       | Y40       | Y20       | Y10       | Y8        | Y4        | Y2        | Y1        |

|    | (default) | Undefined |

Note: Any registered imaginary time should be replaced by correct time, otherwise it will cause the clock counter malfunction.

# I<sup>2</sup>C Bus Interface

## Overview of I<sup>2</sup>C-BUS

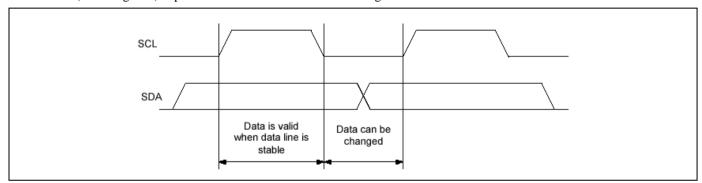

The I<sup>2</sup>C bus supports bi-directional communications via two signal lines: the SDA (data) line and SCL (clock) line. A combination of these two signals is used to transmit and receive communication start/stop signals, data signals, acknowledge signals, and so on. Both the SCL and SDA signals are held at high level whenever communications are not being performed. The starting and stopping of communications is controlled at the rising edge or falling edge of SDA while SCL is at high level. During data transfers, data changes that occur on the SDA line are performed while the SCL line is at low level, and on the receiving side the data is captured while the SCL line is at high level. In either case, the data is transferred via the SCL line at a rate of one bit per clock pulse. The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device and the receiving device responds to communications only when its slave address matches the slave address in the received data.

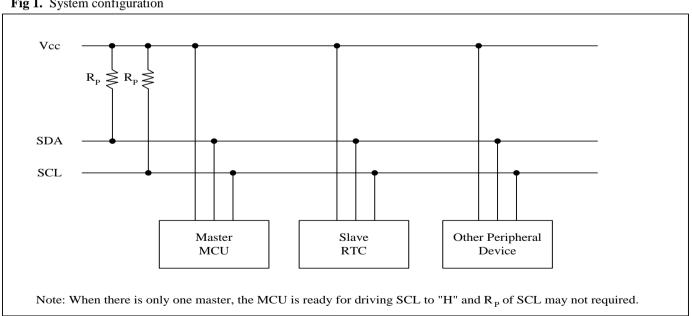

#### **System Configuration**

All ports connected to the I2C bus must be either open drain or open collector ports in order to enable AND connections to multiple devices.

SCL and SDA are both connected to the VDD line via a pull-up resistance. Consequently, SCL and SDA are both held at high level when the bus is released (when communication is not being performed).

Fig 1. System configuration

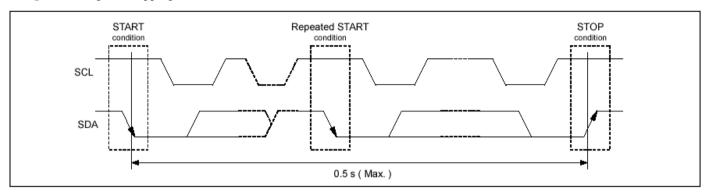

# Starting and Stopping I<sup>2</sup>C Bus Communications

Fig 2. Starting and stopping on I<sup>2</sup>C bus

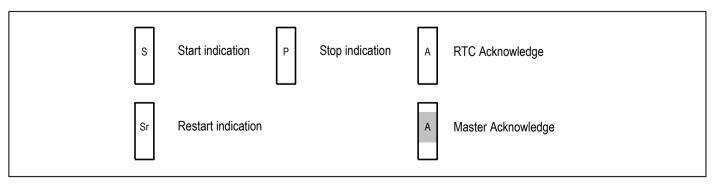

#### 1) START condition, repeated START condition, and STOP condition

- a) START condition

- SDA level changes from high to low while SCL is at high level

- b) STOP condition

- SDA level changes from low to high while SCL is at high level

- c) Repeated START condition (RESTART condition)

In some cases, the START condition occurs between a previous START condition and the next STOP condition, in which case the second START condition is distinguished as a RESTART condition. Since the required status is the same as for the START condition, the SDA level changes from high to low while SCL is at high level.

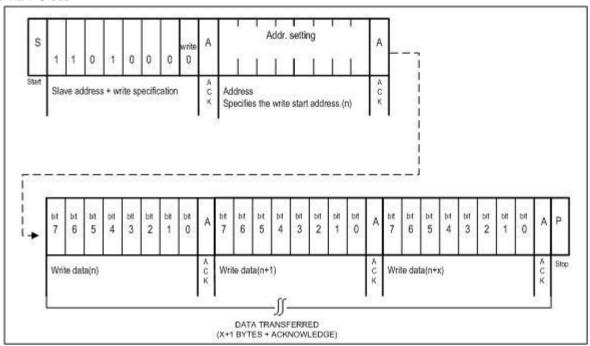

#### 2) Data Transfers and Acknowledge Responses during I<sup>2</sup>C-BUS Communication

#### a) Data transfers

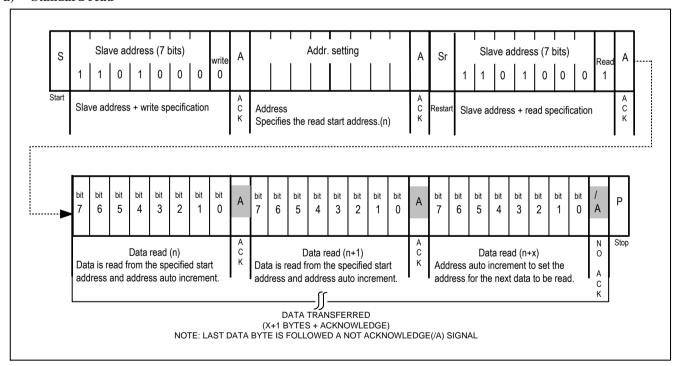

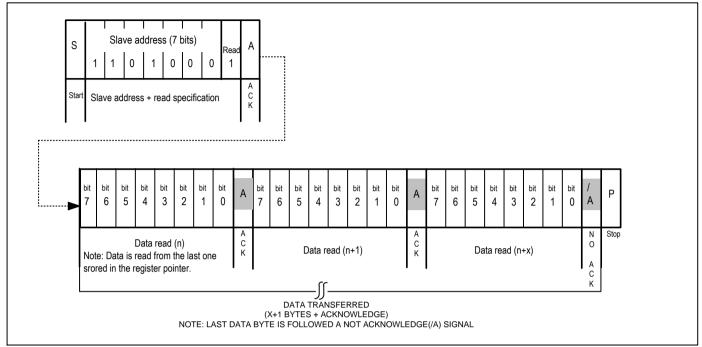

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the amount (bytes) of data that are transferred between the START condition and STOP condition.

The address auto increment function operates during both write and read operations.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low level. The receiver (receiving side) captures data while the SCL line is at high level.

<sup>\*</sup>Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a START, RESTART, or STOP condition.

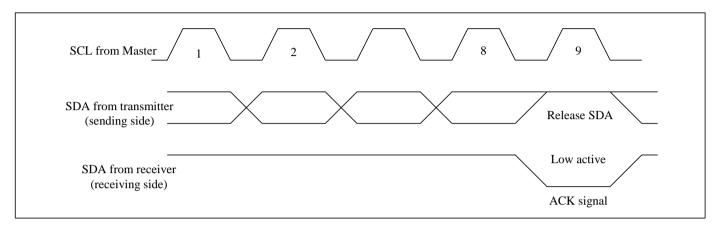

#### b) Data acknowledge response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an 8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal communication has not been established. (This does not include instances where the master device intentionally does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter continues to release the SDA and awaits a STOP condition from the Master.

#### **Slave Address**

The  $I^2C$  bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+  $R\overline{/W}$  specification)]. The receiving device responds to this communication only when the specified slave address it has received matches its own slave address. Slave addresses have a fixed length of 7 bits. See table for the details.

An  $R/\overline{W}$  bit is added to each 7-bit slave address during 8-bit transfers.

| Operation | Transfer data |       |       | Sl    | ave addre | ess   |       |             | R/W bit    |

|-----------|---------------|-------|-------|-------|-----------|-------|-------|-------------|------------|

| Operation | Transfer data | bit 7 | bit 6 | bit 5 | bit 4     | bit 3 | bit 2 | bit 1       | bit 0      |

| Read      | D1 h          | 1     | 1     | 0     | 1         | 0     | 0     | 0           | 1 (= Read) |

| Write     | D0 h          | 1     | 1 0   | 1     | U         | U     | U     | 0 (= Write) |            |

#### I<sup>2</sup>C Bus's Basic Transfer Format

## 1) Write via I<sup>2</sup>C bus

## 2) Read via I<sup>2</sup>C bus

#### a) Standard read

#### b) Simplified read

#### Note:

- 1. The above steps are an example of transfers of one or two bytes only. There is no limit to the number of bytes transferred during actual communications.

- 2. 49H, 4AH are used as test mode address. Customer should not use the addresses.

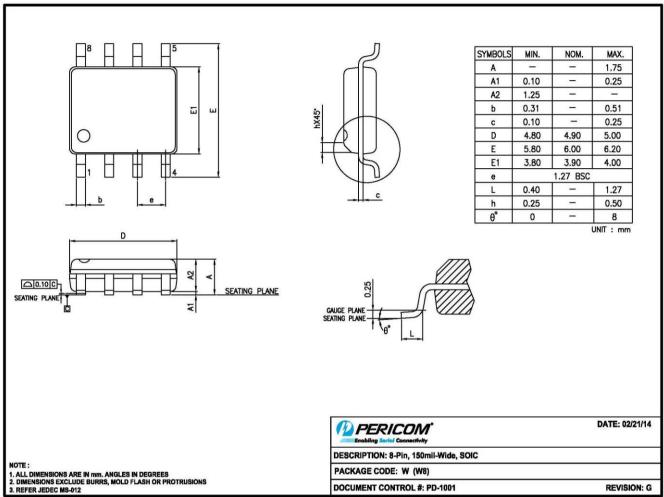

# **Mechanical Information**

W (8-pin SOIC)

15-0103

11/3/2016

PT0206-6

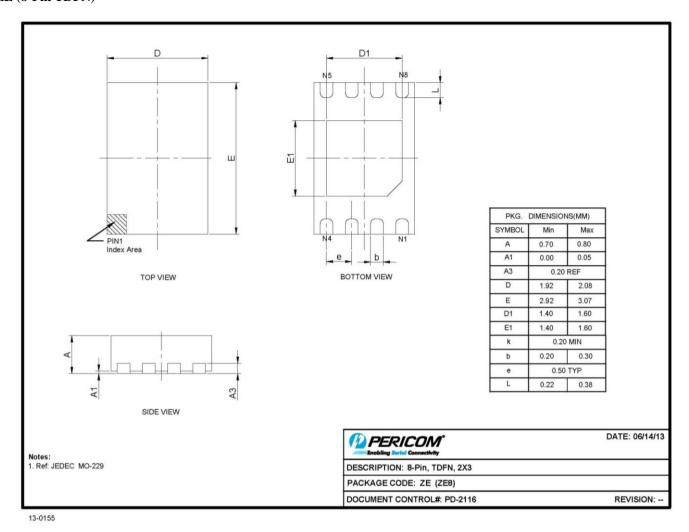

#### ZE (8-Pin TDFN)

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Part Number  | Package Code | Package                              |

|--------------|--------------|--------------------------------------|

| PT7C4307WE   | W            | 8-Pin, 150mil Wide (SOIC)            |

| PT7C4307WEX  | W            | 8-Pin, 150mil Wide (SOIC), Tape/Reel |

| PT7C4307ZEE  | ZE           | 8-Pin, 2x3 (TDFN)                    |

| PT7C4307ZEEX | ZE           | 8-Pin, 2x3 (TDFN), Tape/Reel         |

#### Note:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding X Suffix= Tape/Reel