# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# EZ-BLE™ Creator Module

#### **General Description**

The CYBLE-212020-01 is a fully certified and qualified module supporting Bluetooth<sup>®</sup> Low Energy (BLE) 4.2 wireless communication. The CYBLE-212020-01 is a turnkey solution and includes onboard crystal oscillators, trace antenna, passive components, and the Cypress PSoC 4 BLE. Refer to the PSoC 4 BLE datasheet for additional details on the capabilities of the PSoC 4 BLE device used on this module.

The CYBLE-212020-01 supports a number of peripheral functions (ADC, timers, counters, PWM) and serial communication protocols ( $I^2$ C, UART, SPI) through its programmable architecture. The CYBLE-212020-01 includes a royalty-free BLE stack compatible with Bluetooth 4.2 and provides up to 23 GPIOs in a  $14.52 \times 19.20 \times 2.00$  mm package.

The CYBLE-212020-01 is drop-in compatible with the CYBLE-01211-00 (128KB BT 4.1) and CYBLE-212019-00 (256KB BT 4.1) EZ-BLE Creator  $^{\rm @}$  Modules.

The CYBLE-212020-01 is a complete solution targeted at applications requiring cost-optimized BLE wireless connectivity.

#### **Module Description**

- Module size: 14.52 mm ×19.20 mm × 2.00 mm (with shield)

- Castelated solder pad connections for ease-of-use

- 256-KB flash memory, 32-KB SRAM memory

- Up to 23 GPIOs configurable as open drain high/low, pull-up/pull-down, HI-Z analog, HI-Z digital, or strong output

- Bluetooth 4.2 single-mode module

- □ QDID: 82977

- □ Declaration ID: D030800

- Certified to FCC, ISED, MIC, KC, and CE regulations

- Industrial temperature range: -40 °C to +85 °C

- 32-bit processor (0.9 DMIPS/MHz) with single-cycle 32-bit multiply, operating at up to 48 MHz

- Watchdog timer with dedicated internal low-speed oscillator (ILO)

- Two-pin SWD for programming

#### **Power Consumption**

- TX output power: -18 dbm to +3 dbm

- Received signal strength indicator (RSSI) with 1-dB resolution

- TX current consumption of 15.6 mA (radio only, 0 dbm)

- RX current consumption of 16.4 mA (radio only)

- Low power mode support

- □ Deep Sleep: 1.3 µA with watch crystal oscillator (WCO) on

- ☐ Hibernate: 150 nA with SRAM retention

- ☐ Stop: 60 nA with GPIO (P2.2) or XRES wakeup

#### **Functional Capabilities**

- Up to 22 capacitive sensors for buttons or sliders with best-in-class signal-to-noise ration (SNR) and liquid tolerance

- 12-bit, 1-Msps SAR ADC with internal reference, sample-and-hold (S/H), and channel sequencer

- Two serial communication blocks (SCBs) supporting I<sup>2</sup>C (master/slave), SPI (master/slave), or UART

- Four dedicated 16-bit timer, counter, or PWM (TCPWM) blocks

- LCD drive supported on all GPIOs (common or segment)

- Programmable low-voltage detect (LVD) from 1.8 V to 4.5 V

- I<sup>2</sup>S master interface

- BLE protocol stack supporting generic access profile (GAP)

Central, Peripheral, Observer, or Broadcaster roles

- Switches between Central and Peripheral roles on-the-go

- Standard BLE profiles and services for interoperability

- Custom profile and service for specific use cases

## **Benefits**

The CYBLE-212020-01 module is provided as a turnkey solution, including all necessary hardware required to use BLE communication standards.

- Proven hardware design that is ready for use

- Cost-optimized for applications without space constraint

- Reprogrammable architecture

- Fully certified module eliminates the time needed for design, development and certification processes

- Bluetooth SIG qualified with QDID and Declaration ID

- Flexible communication protocol support

- PSoC Creator™ provides an easy-to-use integrated design environment (IDE) to configure, develop, program, and test a BLE application

Cypress Semiconductor Corporation

Document Number: 002-12597 Rev. \*F

#### More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right module for your design, and to help you to quickly and effectively integrate the module into your design.

- Overview:

- □ EZ-BLE Module Portfolio, Module Roadmap PSoC 4 BLE Silicon Datasheet

- Application notes: Cypress offers a number of BLE application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with EZ-BLE modules are:

- □ AN96841 Getting Started with EZ-BLE Module

- □ AN91267 Getting Started with PSoC® 4 BLE

□ AN97060 PSoC® 4 BLE and PRoC™ BLE Over-The-Air (OTA) Device Firmware Upgrade (DFU) Guide

- □ AN91162 Creating a BLE Custom Profile

- □ AN91184 PSoC 4 BLE Designing BLE Applications

- □ AN92584 Designing for Low Power and Estimating Battery Life for BLE Applications

- □ AN85951 PSoC<sup>®</sup> 4 and PSoC Analog Coprocessor Cap-Sense<sup>®</sup> Design Guide

- □ AN95089 PSoC® 4/PRoC™ BLE Crystal Oscillator Selection and Tuning Techniques

- AN91445 Antenna Design and RF Layout Guidelines

- Technical Reference Manual (TRM):

- □ PRoC® BLE Technical Reference Manual

- Knowledge Base Article

- □ KBA212838 Pin Mapping Differences Between the EZ-BLE™ Creator Evaluation Board (CYBLE-212020-EVAL) and the BLE Pioneer Kit (CY8CKIT-042-BLE)

- □ KBA97095 EZ-BLE™ Module Placement

- □ KBA210638 RF Regulatory Certifications for EZ-BLE™ Creator Module CYBLE-212020-01

- KBA213976 FAQ for BLE and Regulatory Certifications with **EZ-BLE** modules

- □ KBA210802 Queries on BLE Qualification and Declaration Processes

- □ KBA2108122 3D Model Files for EZ-BLE/EZ-BT Modules

- Development Kits:

- CYBLE-212020-EVAL, CYBLE-212020-01 Evaluation Board

- □ CY8CKIT-042-BLE, Bluetooth® Low Energy (BLE) Pioneer

- □ CY8CKIT-002, PSoC® MiniProg3 Program and Debug Kit

- Test and Debug Tools:

- CYSmart, Bluetooth<sup>®</sup> LE Test and Debug Tool (Windows)

- □ CYSmart Mobile, Bluetooth® LE Test and Debug Tool (Android/iOS Mobile App)

# Two Easy-To-Use Design Environments to Get You Started Quickly

## PSoC<sup>®</sup> Creator™ Integrated Design Environment (IDE)

PSoC Creator is an Integrated Design Environment (IDE) that enables concurrent hardware and firmware editing, compiling and debugging of PSoC 3, PSoC 4, PSoC 5LP, PSoC 4 BLE, and EZ-BLE module systems with no code size limitations. PSoC peripherals are designed using schematic capture and simple graphical user interface (GUI) with over 120 pre-verified, production-ready PSoC Components™.

PSoC Components are analog and digital "virtual chips," represented by an icon that users can drag-and-drop into a design and configure to suit a broad array of application requirements.

#### Bluetooth Low Energy Component

The Bluetooth Low Energy Component inside PSoC Creator provides a comprehensive GUI-based configuration window that lets you quickly design BLE applications. The Component incorporates a Bluetooth Core Specification v4.1 compliant BLE protocol stack and provides API functions to enable user applications to interface with the underlying Bluetooth Low Energy Sub-System (BLESS) hardware via the stack.

#### EZ-Serial™ BLE Firmware Platform

The EZ-Serial Firmware Platform provides a simple way to access the most common hardware and communication features needed in BLE applications. EZ-Serial implements an intuitive API protocol over the UART interface and exposes various status and control signals through the module's GPIOs, making it easy to add BLE functionality quickly to existing designs.

Use a simple serial terminal and evaluation kit to begin development without requiring an IDE. Refer to the EZ-Serial web page for User Manuals and instructions for getting started as well as detailed reference materials.

EZ-BLE modules are pre-flashed with the EZ-Serial Firmware Platform. If you do not have EZ-Serial pre-loaded on your module, you can download each EZ-BLE module's firmware images on the EZ-Serial web page.

#### Technical Support

- Frequently Asked Questions (FAQs): Learn more about our BLE ecosystem.

- Forum: See if your question is already answered by fellow developers on the PSoC 4 BLE.

- Visit our support page and create a technical support case or contact a local sales representatives. If you are in the United States, you can talk to our technical support team by calling our toll-free number: +1-800-541-4736. Select option 2 at the prompt.

## **Contents**

| Overview                                        | 4  |

|-------------------------------------------------|----|

| Module Description                              | 4  |

| Pad Connection Interface                        |    |

| Recommended Host PCB Layout                     | 7  |

| Digital and Analog Capabilities and Connections | 9  |

| Power Supply Connections and Recommended Ext    |    |

| Components                                      | 10 |

| Connection Options                              | 10 |

| External Component Recommendation               | 10 |

| Critical Components List                        | 13 |

| Antenna Design                                  | 13 |

| Electrical Specifications                       | 14 |

| GPIO                                            | 16 |

| XRES                                            |    |

| Digital Peripherals                             |    |

| Serial Communication                            |    |

| Memory                                          |    |

| System Resources                                |    |

| Environmental Specifications                    |    |

| Environmental Compliance                        |    |

| RF Certification                                |    |

| Safety Certification                            |    |

| Environmental Conditions                        |    |

| FSD and FMI Protection                          | 29 |

| Regulatory Information                   | 30 |

|------------------------------------------|----|

| FCC                                      | 30 |

| ISED                                     | 31 |

| European R&TTE Declaration of Conformity | 31 |

| MIC Japan                                | 32 |

| KC Korea                                 | 32 |

| Packaging                                |    |

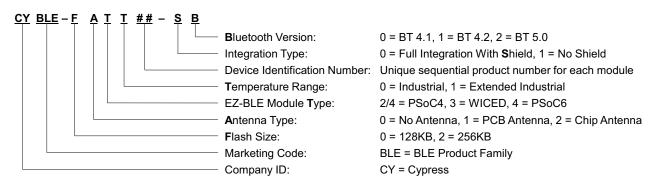

| Ordering Information                     | 35 |

| Part Numbering Convention                | 35 |

| Acronyms                                 | 36 |

| Document Conventions                     | 36 |

| Units of Measure                         | 36 |

| Document History Page                    | 37 |

| Sales, Solutions, and Legal Information  | 38 |

| Worldwide Sales and Design Support       | 38 |

| Products                                 | 38 |

| PSoC® Solutions                          | 38 |

| Cypress Developer Community              | 38 |

| Technical Support                        | 38 |

## Overview

#### **Module Description**

The CYBLE-212020-01 module is a complete module designed to be soldered to the applications main board.

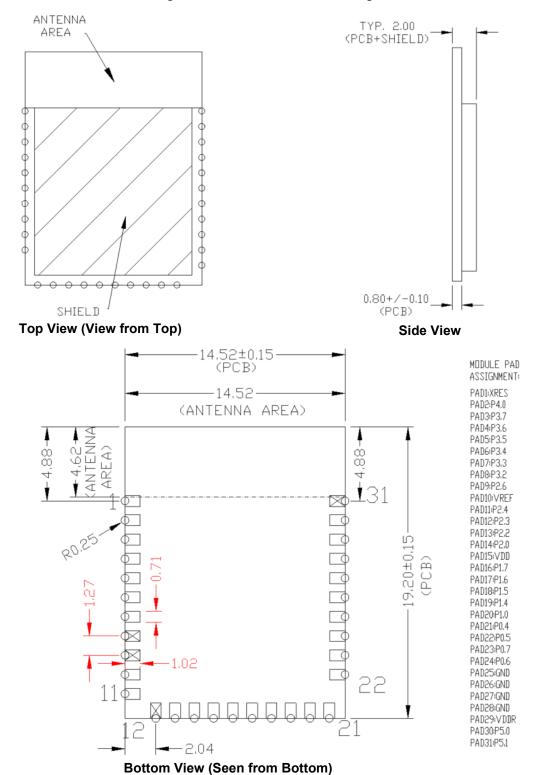

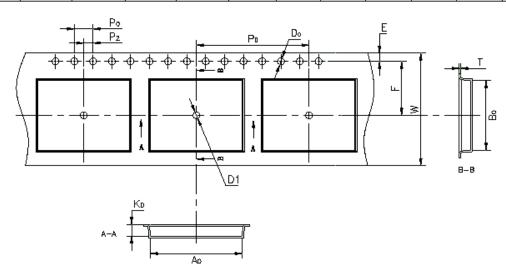

Module Dimensions and Drawing

Cypress reserves the right to select components (including the appropriate BLE device) from various vendors to achieve the BLE module functionality. Such selections will still guarantee that all height restrictions of the component area are maintained. Designs should be held within the physical dimensions shown in the mechanical drawings in Figure 1. All dimensions are in millimeters (mm).

**Table 1. Module Design Dimensions**

| Dimension Item                                                 | Specification |                          |

|----------------------------------------------------------------|---------------|--------------------------|

| Module dimensions                                              | Length (X)    | 14.52 ± 0.15 mm          |

| Module difficults                                              | Width (Y)     | 19.20 ± 0.15 mm          |

| Antenna location dimensions                                    | Length (X)    | 11.00 ± 0.15 mm          |

| Afficilia location differsions                                 | Width (Y)     | 5.00 ± 0.15 mm           |

| PCB thickness                                                  | Height (H)    | 0.80 ± 0.10 mm           |

| Shield height                                                  | Height (H)    | 1.20 ± 0.10 mm           |

| Maximum component height                                       | Height (H)    | 1.20-mm typical (shield) |

| Total module thickness (bottom of module to highest component) | Height (H)    | 2.00-mm typical          |

See Figure 1 on page 5 for the mechanical reference drawing for CYBLE-212020-01.

Figure 1. Module Mechanical Drawing

#### Note

<sup>1.</sup> No metal should be located beneath or above the antenna area. Only bare PCB material should be located beneath the antenna area. For more information on recommended host PCB layout, see Figure 3, Figure 4, Figure 5, and Figure 6 and Table 3.

#### **Pad Connection Interface**

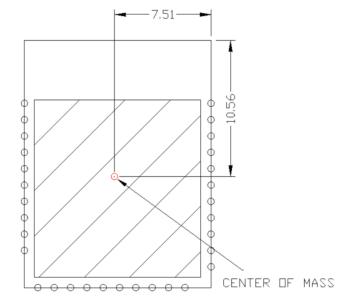

As shown in the bottom view of Figure 1 on page 5, the CYBLE-212020-01 connects to the host board via solder pads on the back side of the module. Table 2 and Figure 2 detail the solder pad length, width, and pitch dimensions of the CYBLE-212020-01 module.

Table 2. Solder Pad Connection Description

| Name | Connections | Connection Type | Pad Length Dimension | Pad Width Dimension | Pad Pitch |

|------|-------------|-----------------|----------------------|---------------------|-----------|

| SP   | 31          | Solder Pads     | 1.02 mm              | 0.71 mm             | 1.27 mm   |

1102 22

Figure 2. Solder Pad Dimensions (Seen from Bottom)

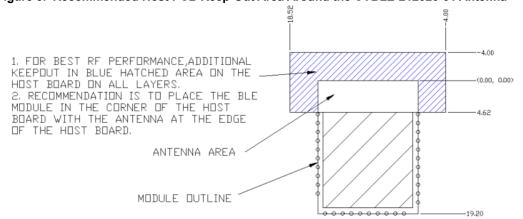

To maximize RF performance, the host layout should follow these recommendations:

- The ideal placement of the Cypress BLE module is in a corner of the host board with the trace antenna located at the far corner.

This placement minimizes the additional recommended keep-out area stated in item 2. Refer to AN96841 for module placement best practices.

- 2. To maximize RF performance, the area immediately around the Cypress BLE module trace antenna should contain an additional keep-out area, where no grounding or signal trace are contained. The keep-out area applies to all layers of the host board. The recommended dimensions of the host PCB keep-out area are shown in Figure 3 (dimensions are in mm).

Figure 3. Recommended Host PCB Keep-Out Area Around the CYBLE-212020-01 Antenna

Host PCB Keep-Out Area Around Trace Antenna

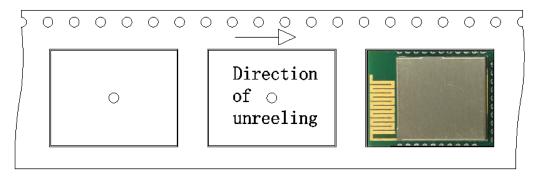

## **Recommended Host PCB Layout**

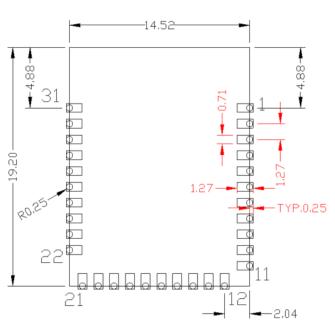

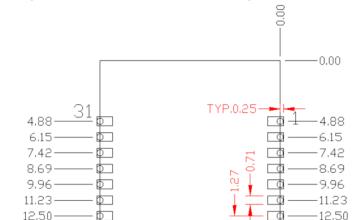

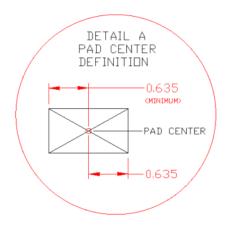

Figure 4, Figure 5, Figure 6, and Table 3 provide details that can be used for the recommended host PCB layout pattern for the CYBLE-212020-01. Dimensions are in millimeters unless otherwise noted. Pad length of 1.27 mm (0.635 mm from center of the pad on either side) shown in Figure 6 is the minimum recommended host pad length. The host PCB layout pattern can be completed using either Figure 4, Figure 5, or Figure 6. It is not necessary to use all figures to complete the host PCB layout pattern.

13.77-

15.04 -

16.31

14,52 13,47 12,20 10,93 9,66 7,12 7,12 5,85 4,58

Figure 4. Host Layout Pattern for CYBLE-212020-01

Top View (Seen on Host PCB)

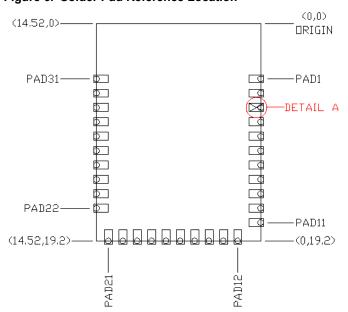

Figure 5. Module Pad Location from Origin

Top View (Seen on Host PCB)

-13.77

15.04

16.31

17,58 19.20

12

Table 3 provides the center location for each solder pad on the CYBLE-212020-01. All dimensions are referenced to the center of the solder pad. Refer to Figure 6 for the location of each module solder pad.

**Table 3. Module Solder Pad Location**

| Solder Pad<br>(Center of Pad) | Location (X,Y) from<br>Orign (mm) | Dimension from<br>Orign (mils) |

|-------------------------------|-----------------------------------|--------------------------------|

| 1                             | (0.39, 4.88)                      | (15.35, 192.13)                |

| 2                             | (0.39, 6.15)                      | (15.35, 242.13)                |

| 3                             | (0.39, 7.42)                      | (15.35, 292.13)                |

| 4                             | (0.39, 8.69)                      | (15.35, 342.13)                |

| 5                             | (0.39, 9.96)                      | (15.35, 392.13)                |

| 6                             | (0.39, 11.23)                     | (15.35, 442.13)                |

| 7                             | (0.39, 12.50)                     | (15.35, 492.13)                |

| 8                             | (0.39, 13.77)                     | (15.35, 542.13)                |

| 9                             | (0.39, 15.04)                     | (15.35, 592.13)                |

| 10                            | (0.39, 16.31)                     | (15.35, 642.13)                |

| 11                            | (0.39, 17.58)                     | (15.35, 692.13)                |

| 12                            | (2.04, 18.82)                     | (80.31, 740.94)                |

| 13                            | (3.31, 18.82)                     | (130.31, 740.94)               |

| 14                            | (4.58, 18.82)                     | (180.31, 740.94)               |

| 15                            | (5.85, 18.82)                     | (230.31, 740.94)               |

| 16                            | (7.12, 18.82)                     | (280.31, 740.94)               |

| 17                            | (8.39, 18.82)                     | (330.31, 740.94)               |

| 18                            | (9.66, 18.82)                     | (380.31, 740.94)               |

| 19                            | (10.93, 18.82)                    | (430.31, 740.94)               |

| 20                            | (12.20, 18.82)                    | (480.31, 740.94)               |

| 21                            | (13.47, 18.82)                    | (530.31, 740.94)               |

| 22                            | (14.14, 16.31)                    | (556.69, 642.12)               |

| 23                            | (14.14, 15.04)                    | (556.69, 592.12)               |

| 24                            | (14.14, 13.77)                    | (556.69, 542.12)               |

| 25                            | (14.14, 12.50)                    | (556.69, 492.12)               |

| 26                            | (14.14, 11.23)                    | (556.69, 442.12)               |

| 27                            | (14.14, 9.96)                     | (556.69, 392.12)               |

| 28                            | (14.14, 8.69)                     | (556.69, 342.12)               |

| 29                            | (14.14, 7.42)                     | (556.69, 292.12)               |

| 30                            | (14.14, 6.15)                     | (556.69, 242.12)               |

| 31                            | (14.14, 4.88)                     | (556.69, 192.12)               |

|                               |                                   |                                |

Figure 6. Solder Pad Reference Location

Top View (Seen on Host PCB)

## **Digital and Analog Capabilities and Connections**

Table 4 details the solder pad connection definitions and available functions for each connection pad. Table 4 lists the solder pads on CYBLE-212020-01, the BLE device port-pin, and denotes whether the function shown is available for each solder pad. Each connection is configurable for a single option shown with a .

Table 4. Solder Pad Connection Definitions<sup>[2]</sup>

| Solder Pad<br>Number | Device<br>Port Pin  | UART         | SPI          | I <sup>2</sup> C | TCPWM <sup>[3,4]</sup> | CapSense                     | WCO<br>Out | ECO<br>Out | LCD      | SWD              | GPIO     |

|----------------------|---------------------|--------------|--------------|------------------|------------------------|------------------------------|------------|------------|----------|------------------|----------|

| 1                    | XRES                |              |              | External Re      | eset Hardware Cor      | •                            | İ          |            |          |                  |          |

| 2                    | P4.0 <sup>[5]</sup> | _ , _ /      | ✓(SCB1_MOSI) |                  | ✓(TCPWM0_P)            | <b>√</b> (C <sub>MOD</sub> ) |            |            | <b>\</b> |                  | <b>/</b> |

| 3                    | P3.7                | ✓(SCB1_CTS)  |              |                  | ✓(TCPWM)               | √(Sensor)                    | <b>✓</b>   |            | <b>/</b> |                  | <b>/</b> |

| 4                    | P3.6                | ✓(SCB1_RTS)  |              |                  | ✓(TCPWM)               | ✓(Sensor)                    |            |            | /        |                  | /        |

| 5                    | P3.5                | ✓(SCB1_TX)   |              | ✓(SCB1_SCL)      | ✓(TCPWM)               | ✓(Sensor)                    |            |            | /        |                  | /        |

| 6                    | P3.4                | ✓(SCB1_RX)   |              | ✓(SCB1_SDA)      | ✓(TCPWM)               | √ (Sensor)                   |            |            | /        |                  | <b>/</b> |

| 7                    | P3.3                | ✓(SCB0_CTS)  |              |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | <b>✓</b> |                  | <b>✓</b> |

| 8                    | P3.2                | √(SCB0_RTS)  |              |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | /        |                  | <b>✓</b> |

| 9                    | P2.6                |              |              |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | /        |                  | <b>/</b> |

| 10                   | VREF                |              |              | Refere           | nce Voltage Input (    | (Optional)                   | ı          |            |          |                  |          |

| 11                   | P2.4                |              |              |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | <b>/</b> |                  | <b>✓</b> |

| 12                   | P2.3                |              |              |                  | ✓(TCPWM)               | √(Sensor)                    | <b>✓</b>   |            | <b>✓</b> |                  | <b>✓</b> |

| 13                   | P2.2                |              | ✓(SCB0_SS3)  |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | /        |                  | /        |

| 14                   | P2.0                |              | ✓(SCB0_SS1)  |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | 1        |                  | 1        |

| 15                   | $V_{DD}$            |              |              | Digital Pow      | er Supply Input (1     | .8 V to 5.5 V)               | ı          |            |          |                  |          |

| 16                   | P1.7                | ✓(SCB0_CTS)  | √(SCB0_SCLK) |                  | ✓(TCPWM)               | √ (Sensor)                   |            |            | /        |                  | <b>/</b> |

| 17                   | P1.6                | ✓ (SCBO_RTS) | ✓(SCB0_SS0)  |                  | ✓(TCPWM)               | √ (Sensor)                   |            |            | /        |                  | <b>/</b> |

| 18                   | P1.5                | ✓(SCB0_TX)   | ✓(SCB0_MISO) | ✓(SCB0_SCL)      | ✓(TCPWM)               | √ (Sensor)                   |            |            | /        |                  | /        |

| 19                   | P1.4                | ✓(SCB0_RX)   | ✓(SCB0_MOSI) | ✓(SCB0_SDA)      | ✓(TCPWM)               | √ (Sensor)                   |            |            | /        |                  | <b>/</b> |

| 20                   | P1.0                |              |              |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | <b>/</b> |                  | <b>✓</b> |

| 21                   | P0.4                | ✓(SCB0_RX)   | ✓(SCB0_MOSI) | ✓(SCB0_SDA)      | ✓(TCPWM)               | √(Sensor)                    |            | <b>✓</b>   | <b>✓</b> |                  | <b>✓</b> |

| 22                   | P0.5                | ✓(SCB0_TX)   | ✓(SCB0_MISO) | ✓(SCB0_SCL)      | ✓(TCPWM)               | √(Sensor)                    |            |            | <b>✓</b> |                  | <b>✓</b> |

| 23                   | P0.7                | ✓(SCB0_CTS)  | ✓(SCB0_SCLK  |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | /        | ✓(SWDCLK)        | <b>✓</b> |

| 24                   | P0.6                | √(SCB0_RTS)  | ✓(SCB0_SS0)  |                  | ✓(TCPWM)               | √(Sensor)                    |            |            | 1        | <b>√</b> (SWDIO) | 1        |

| 25                   | GND <sup>[6]</sup>  |              |              | 1                | Ground Connection      | on                           | ı          |            |          |                  |          |

| 26                   | GND <sup>[6]</sup>  |              |              |                  | Ground Connection      | on                           |            |            |          |                  |          |

| 27                   | GND <sup>[6]</sup>  |              |              |                  | Ground Connection      |                              |            |            |          |                  |          |

| 28                   | GND <sup>[6]</sup>  |              |              |                  | Ground Connection      |                              |            |            |          |                  |          |

| 29                   | $V_{DDR}$           |              |              |                  | ower Supply (1.9       |                              |            |            |          |                  |          |

| 30                   | P5.0                | ✓(SCB1_RX)   |              |                  | ✓(TCPWM3_P)            |                              |            |            | <b>/</b> |                  | <b>/</b> |

| 31                   | P5.1                | ✓(SCB1_TX)   | ✓ (SCB1_SCLK | ✓ (SCB1_SCL)     | ✓(TCPWM3_N)            | √ (Sensor)                   |            | /          | <b>/</b> |                  | <b>✓</b> |

- 2. If the I<sup>2</sup>S feature is used in the design, the I<sup>2</sup>S pins shall be dynamically routed to the appropriate available GPIO by PSoC Creator.

- 3. TCPWM: Timer, Counter, and Pulse Width Modulator. If supported, the pad can be configured to any of these peripheral functions

- TCPWM connections on ports 0, 1, 2, and 3 can be routed through the Digital Signal Interconnect (DSI) to any of the TCPWM blocks and can be either positive or negative polarity. TCPWM connections on ports 4 and 5 are direct and can only be used with the specified TCPWM block and polarity specified above.

- When using the capacitive sensing functionality, Pad 2 (P4.0) must be connected to a C<sub>MOD</sub> capacitor (located off of Cypress BLE Module). The value of this capacitor is 2.2 nF and should be placed as close to the module as possible.

The main board needs to connect all GND connections (Pad 25/26/27/28) on the module to the common ground of the system.

## **Power Supply Connections and Recommended External Components**

#### **Power Connections**

The CYBLE-212020-01 contains two power supply connections, VDD and VDDR. The VDD connection supplies power for both digital and analog device operation. The VDDR connection supplies power for the device radio.

VDD accepts a supply range of 1.71 V to 5.5 V. VDDR accepts a supply range of 1.9 V to 5.5 V. These specifications are listed in Table 9. The maximum power supply ripple for both power connections on the module is 100 mV, as shown in Table 7.

The power supply ramp rate of VDD must be equal to or greater than that of VDDR.

#### **Connection Options**

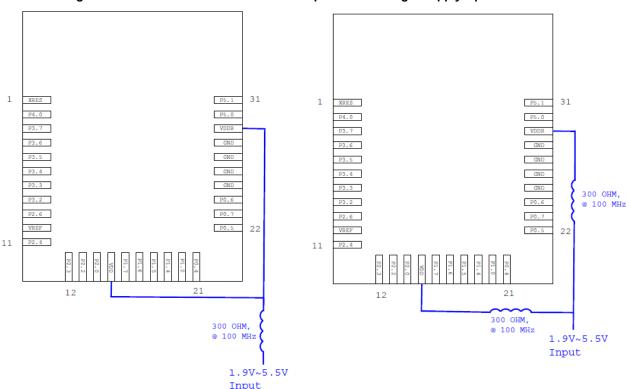

Two connection options are available for any application:

- 1. Single supply: Connect VDD and VDDR to the same supply.

- 2. Independent supply: Power VDD and VDDR separately.

#### **External Component Recommendation**

In either connection scenario, it is recommended to place an external ferrite bead between the supply and the module connection. The ferrite bead should be positioned as close as possible to the module pin connection.

Figure 7 details the recommended host schematic options for a single supply scenario. The use of one or two ferrite beads will depend on the specific application and configuration of the CYBLE-212020-01.

Figure 8 details the recommended host schematic for an independent supply scenario.

The recommended ferrite bead value is 330  $\Omega$ , 100 MHz. (Murata BLM21PG331SN1D).

Figure 7. Recommended Host Schematic Options for a Single Supply Option

Single Ferrite Bead Option(Seen from Bottom)

Two Ferrite Bead Option (Seen from Bottom)

Figure 8. Recommended Host Schematic for an Independent Supply Option

Independent Power Supply Option(Seen from Bottom)

VREF

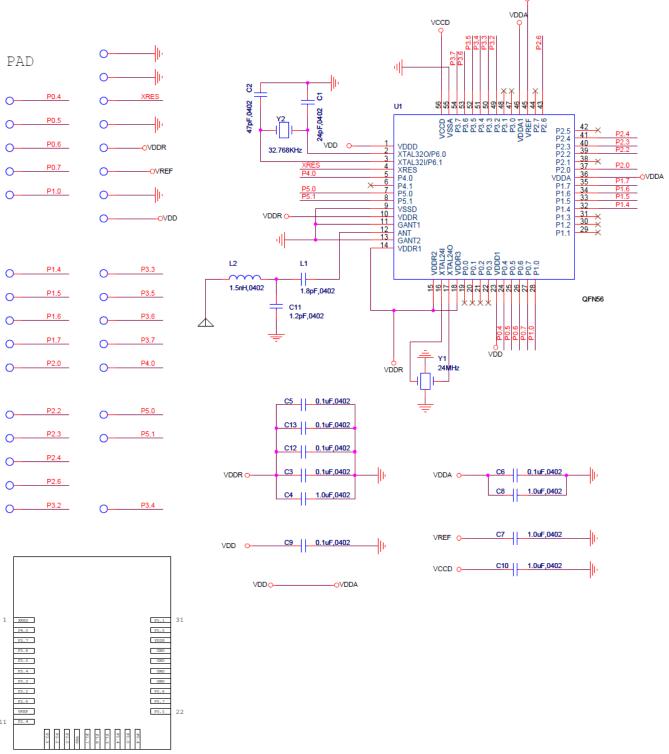

The CYBLE-212020-01 schematic is shown in Figure 9.

Figure 9. CYBLE-212020-01 Schematic Diagram

## **Critical Components List**

Table 5 details the critical components used in the CYBLE-212020-01 module.

## Table 5. Critical Component List

| Component | Reference Designator | Description           |

|-----------|----------------------|-----------------------|

| Silicon   | U1                   | 56-pin QFN PSoC 4 BLE |

| Crystal   | Y1                   | 24.000 MHz, 12PF      |

| Crystal   | Y2                   | 32.768 kHz, 12.5PF    |

## **Antenna Design**

Table 6 details trace antenna used in the CYBLE-212020-01 module. For more information, see Table 8.

## **Table 6. Trace Antenna Specifications**

| Item            | Description      |

|-----------------|------------------|

| Frequency Range | 2400–2500 MHz    |

| Peak Gain       | 0.5 dBi typical  |

| Average Gain    | -0.5-dBi typical |

| Return Loss     | 10-dB minimum    |

## **Electrical Specifications**

Table 7 details the absolute maximum electrical characteristics for the Cypress BLE module.

Table 7. CYBLE-212020-01 Absolute Maximum Ratings

| Parameter                   | Description                                                                             | Min  | Тур | Max      | Units | Details/Conditions                                        |

|-----------------------------|-----------------------------------------------------------------------------------------|------|-----|----------|-------|-----------------------------------------------------------|

| V <sub>DDD_ABS</sub>        | Analog, digital, or radio supply relative to $V_{SS}$ ( $V_{SSD} = V_{SSA}$ )           | -0.5 | ı   | 6        | >     | Absolute maximum                                          |

| V <sub>CCD_ABS</sub>        | Direct digital core voltage input relative to V <sub>SSD</sub>                          | -0.5 | _   | 1.95     | V     | Absolute maximum                                          |

| V <sub>DD_RIPPLE</sub>      | Maximum power supply ripple for $V_{DD}$ and $V_{DDR}$ input voltage                    | -    | ı   | 100      | mV    | 3.0-V supply<br>Ripple frequency of 100 kHz<br>to 750 kHz |

| V <sub>GPIO_ABS</sub>       | GPIO voltage                                                                            | -0.5 | _   | VDD +0.5 | V     | Absolute maximum                                          |

| I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                                | -25  | -   | 25       | mA    | Absolute maximum                                          |

| I <sub>GPIO_injection</sub> | GPIO injection current: Maximum for $V_{IH} > V_{DD}$ and minimum for $V_{IL} < V_{SS}$ | -0.5 | -   | 0.5      | mA    | Absolute maximum current injected per pin                 |

| LU                          | Pin current for latch-up                                                                | -200 |     | 200      | mA    | -                                                         |

Table 8 details the RF characteristics for the Cypress BLE module.

Table 8. CYBLE-212020-01 RF Performance Characteristics

| Parameter        | Description                   | Min  | Тур   | Max  | Units | Details/Conditions                 |

|------------------|-------------------------------|------|-------|------|-------|------------------------------------|

| RF <sub>O</sub>  | RF output power on ANT        | -18  | 0     | 3    | dBm   | Configurable via register settings |

| RX <sub>S</sub>  | RF receive sensitivity on ANT | _    | -87   | -    | dBm   | Guaranteed by design simulation    |

| F <sub>R</sub>   | Module frequency range        | 2400 | _     | 2480 | MHz   | _                                  |

| G <sub>P</sub>   | Peak gain                     | _    | 0.5   | _    | dBi   | _                                  |

| G <sub>Avg</sub> | Average gain                  | _    | -0.5  | _    | dBi   | -                                  |

| RL               | Return loss                   | _    | -10.5 | -    | dB    | _                                  |

Table 9 through Table 48 list the module level electrical characteristics for the CYBLE-212020-01. All specifications are valid for  $-40 \text{ °C} \le \text{TA} \le 85 \text{ °C}$  and  $\text{TJ} \le 100 \text{ °C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

Table 9. CYBLE-212020-01 DC Specifications

| Parameter         | Description                            | Min  | Тур | Max  | Units | Details/Conditions                    |

|-------------------|----------------------------------------|------|-----|------|-------|---------------------------------------|

| V <sub>DD1</sub>  | Power supply input voltage             | 1.8  | _   | 5.5  | V     | With regulator enabled                |

| V <sub>DD2</sub>  | Power supply input voltage unregulated | 1.71 | 1.8 | 1.89 | V     | Internally unregulated supply         |

| V <sub>DDR1</sub> | Radio supply voltage (radio on)        | 1.9  | _   | 5.5  | V     | -                                     |

| V <sub>DDR2</sub> | Radio supply voltage (radio off)       | 1.71 | _   | 5.5  | V     | -                                     |

| Active Mode,      | V <sub>DD</sub> = 1.71 V to 5.5 V      |      |     |      |       |                                       |

| I <sub>DD3</sub>  | Execute from flash; CPU at 3 MHz       | -    | 1.7 | _    | mA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

| I <sub>DD4</sub>  | Execute from flash; CPU at 3 MHz       | _    | _   | _    | mA    | T = -40 °C to 85 °C                   |

| I <sub>DD5</sub>  | Execute from flash; CPU at 6 MHz       | -    | 2.5 | -    | mA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

| I <sub>DD6</sub>  | Execute from flash; CPU at 6 MHz       | _    | _   | _    | mA    | T = -40 °C to 85 °C                   |

| I <sub>DD7</sub>  | Execute from flash; CPU at 12 MHz      | _    | 4   | _    | mA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

Table 9. CYBLE-212020-01 DC Specifications (continued)

| Parameter           | Description                                             | Min      | Тур  | Max | Units | Details/Conditions                                        |

|---------------------|---------------------------------------------------------|----------|------|-----|-------|-----------------------------------------------------------|

| DD8                 | Execute from flash; CPU at 12 MHz                       | -        | _    | _   | mA    | T = -40 °C to 85 °C                                       |

| DD9                 | Execute from flash; CPU at 24 MHz                       | -        | 7.1  | _   | mA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                     |

| DD10                | Execute from flash; CPU at 24 MHz                       | _        | _    | _   | mA    | T = -40 °C to 85 °C                                       |

| I <sub>DD11</sub>   | Execute from flash; CPU at 48 MHz                       | -        | 13.4 | _   | mA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                     |

| $I_{\mathrm{DD12}}$ | Execute from flash; CPU at 48 MHz                       | _        | _    | _   | mA    | T = -40 °C to 85 °C                                       |

| Sleep Mode,         | V <sub>DD</sub> = 1.8 V to 5.5 V                        |          | 1    | l . | -1    | L                                                         |

| DD13                | IMO on                                                  | _        | _    | _   | mA    | $T = 25$ °C, $V_{DD} = 3.3$ V, SYSCLK = 3 MHz             |

| Sleep Mode,         | V <sub>DD</sub> and V <sub>DDR</sub> = 1.9 V to 5.5 V   | <b>"</b> | •    | I.  | ı     | 1                                                         |

| DD14                | ECO on                                                  | _        | _    | _   | mA    | $T = 25$ °C, $V_{DD} = 3.3$ V, SYSCLK = 3 MHz             |

| Deep-Sleep I        | Mode, V <sub>DD</sub> = 1.8 V to 3.6 V                  | <u>'</u> | •    | •   |       |                                                           |

| I <sub>DD15</sub>   | WDT with WCO on                                         | _        | 1.5  | _   | μA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                     |

| I <sub>DD16</sub>   | WDT with WCO on                                         | _        | _    | _   | μA    | T = -40 °C to 85 °C                                       |

| I <sub>DD17</sub>   | WDT with WCO on                                         | _        | _    | _   | μA    | T = 25 °C,<br>V <sub>DD</sub> = 5 V                       |

| I <sub>DD18</sub>   | WDT with WCO on                                         | -        | _    | _   | μA    | T = -40 °C to 85 °C                                       |

| Deep-Sleep I        | Mode, V <sub>DD</sub> = 1.71 V to 1.89 V (Regulator Byr | passed)  |      |     |       |                                                           |

| I <sub>DD19</sub>   | WDT with WCO on                                         | _        | _    | _   | μA    | T = 25 °C                                                 |

| I <sub>DD20</sub>   | WDT with WCO on                                         | _        | _    | _   | μA    | T = -40 °C to 85 °C                                       |

| Hibernate Mo        | ode, V <sub>DD</sub> = 1.8 V to 3.6 V                   |          |      |     |       | ,                                                         |

| DD27                | GPIO and reset active                                   | _        | 150  | _   | nA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                     |

| I <sub>DD28</sub>   | GPIO and reset active                                   | _        | _    | _   | nA    | T = -40 °C to 85 °C                                       |

| Hibernate Mo        | ode, V <sub>DD</sub> = 3.6 V to 5.5 V                   |          |      |     |       |                                                           |

| I <sub>DD29</sub>   | GPIO and reset active                                   | _        | _    | _   | nA    | T = 25 °C,<br>V <sub>DD</sub> = 5 V                       |

| I <sub>DD30</sub>   | GPIO and reset active                                   | _        | _    | _   | nA    | T = -40 °C to 85 °C                                       |

| Stop Mode, \        | / <sub>DD</sub> = 1.8 V to 3.6 V                        |          |      |     |       |                                                           |

| I <sub>DD33</sub>   | Stop-mode current (V <sub>DD</sub> )                    | _        | 20   | _   | nA    | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                     |

| I <sub>DD34</sub>   | Stop-mode current (V <sub>DDR</sub> )                   | _        | 40   |     | nA    | T = 25 °C,<br>V <sub>DDR</sub> = 3.3 V                    |

| I <sub>DD35</sub>   | Stop-mode current (V <sub>DD</sub> )                    | _        | _    | _   | nA    | T = -40 °C to 85 °C                                       |

| DD36                | Stop-mode current (V <sub>DDR</sub> )                   | _        | _    | _   | nA    | T = -40 °C to 85 °C,<br>V <sub>DDR</sub> = 1.9 V to 3.6 V |

| Stop Mode, \        | / <sub>DD</sub> = 3.6 V to 5.5 V                        |          |      |     |       |                                                           |

| I <sub>DD37</sub>   | Stop-mode current (V <sub>DD</sub> )                    | _        | _    | _   | nA    | T = 25 °C,<br>V <sub>DD</sub> = 5 V                       |

| I <sub>DD38</sub>   | Stop-mode current (V <sub>DDR</sub> )                   | _        | _    | _   | nA    | T = 25 °C,<br>V <sub>DDR</sub> = 5 V                      |

| I <sub>DD39</sub>   | Stop-mode current (V <sub>DD</sub> )                    | _        | _    | _   | nA    | T = -40 °C to 85 °C                                       |

| I <sub>DD40</sub>   | Stop-mode current (V <sub>DDR</sub> )                   | _        | _    | _   | nA    | T = -40 °C to 85 °C                                       |

Table 10. AC Specifications

| Parameter              | Description                 | Min | Тур | Max | Units | Details/Conditions                                   |

|------------------------|-----------------------------|-----|-----|-----|-------|------------------------------------------------------|

| F <sub>CPU</sub>       | CPU frequency               | DC  | _   | 48  | MHz   | $1.71 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ |

| T <sub>SLEEP</sub>     | Wakeup from Sleep mode      | _   | 0   | _   | μs    | Guaranteed by characterization                       |

| T <sub>DEEPSLEEP</sub> | Wakeup from Deep-Sleep mode | _   | -   | 25  | μs    | 24-MHz IMO. Guaranteed by characterization           |

| T <sub>HIBERNATE</sub> | Wakeup from Hibernate mode  | _   | _   | 2   | ms    | Guaranteed by characterization                       |

| T <sub>STOP</sub>      | Wakeup from Stop mode       | _   | _   | 2   | ms    | XRES wakeup                                          |

## **GPIO**

Table 11. GPIO DC Specifications

| Parameter                      | Description                                                          | Min                   | Тур | Max                  | Units | Details/Conditions                              |

|--------------------------------|----------------------------------------------------------------------|-----------------------|-----|----------------------|-------|-------------------------------------------------|

|                                | Input voltage HIGH threshold                                         | 0.7 × V <sub>DD</sub> | -   | _                    | V     | CMOS input                                      |

| V <sub>IH</sub> <sup>[7]</sup> | LVTTL input, V <sub>DD</sub> < 2.7 V                                 | 0.7 × V <sub>DD</sub> | _   | -                    | V     | -                                               |

|                                | LVTTL input, V <sub>DD</sub> >= 2.7 V                                | 2.0                   | _   | _                    | V     | -                                               |

|                                | Input voltage LOW threshold                                          | _                     | _   | $0.3 \times V_{DD}$  | V     | CMOS input                                      |

| $V_{IL}$                       | LVTTL input, V <sub>DD</sub> < 2.7 V                                 | _                     | _   | 0.3× V <sub>DD</sub> | V     | -                                               |

|                                | LVTTL input, V <sub>DD</sub> >= 2.7 V                                | _                     | _   | 0.8                  | V     | -                                               |

| V                              | Output voltage HIGH level                                            | V <sub>DD</sub> -0.6  | _   | _                    | V     | $I_{OH}$ = 4 mA at 3.3-V $V_{DD}$               |

| V <sub>OH</sub>                | Output voltage HIGH level                                            | V <sub>DD</sub> -0.5  | _   | _                    | V     | I <sub>OH</sub> = 1 mA at 1.8-V V <sub>DD</sub> |

|                                | Output voltage LOW level                                             | _                     | _   | 0.6                  | V     | $I_{OL}$ = 8 mA at 3.3-V $V_{DD}$               |

| V <sub>OL</sub>                | Output voltage LOW level                                             | _                     | _   | 0.6                  | V     | $I_{OL}$ = 4 mA at 1.8-V $V_{DD}$               |

|                                | Output voltage LOW level                                             | _                     | _   | 0.4                  | V     | $I_{OL}$ = 3 mA at 3.3-V $V_{DD}$               |

| R <sub>PULLUP</sub>            | Pull-up resistor                                                     | 3.5                   | 5.6 | 8.5                  | kΩ    | -                                               |

| R <sub>PULLDOWN</sub>          | Pull-down resistor                                                   | 3.5                   | 5.6 | 8.5                  | kΩ    | -                                               |

| I <sub>IL</sub>                | Input leakage current (absolute value)                               | _                     | _   | 2                    | nA    | 25 °C, V <sub>DD</sub> = 3.3 V                  |

| I <sub>IL_CTBM</sub>           | Input leakage on CTBm input pins                                     | _                     | _   | 4                    | nA    | -                                               |

| C <sub>IN</sub>                | Input capacitance                                                    | _                     | _   | 7                    | pF    | -                                               |

| V <sub>HYSTTL</sub>            | Input hysteresis LVTTL                                               | 25                    | 40  | _                    | mV    | V <sub>DD</sub> > 2.7 V                         |

| V <sub>HYSCMOS</sub>           | Input hysteresis CMOS                                                | $0.05 \times V_{DD}$  | -   | _                    | 1     | _                                               |

| I <sub>DIODE</sub>             | Current through protection diode to V <sub>DD</sub> /V <sub>SS</sub> | _                     | _   | 100                  | μA    | -                                               |

| I <sub>TOT_GPIO</sub>          | Maximum total source or sink chip current                            | _                     | _   | 200                  | mA    | -                                               |

Note 7.  $V_{IH}$  must not exceed  $V_{DD}$  + 0.2 V.

Table 12. GPIO AC Specifications

| Parameter            | Description                                                               | Min | Тур | Max  | Units | Details/Conditions                                  |

|----------------------|---------------------------------------------------------------------------|-----|-----|------|-------|-----------------------------------------------------|

| T <sub>RISEF</sub>   | Rise time in Fast-Strong mode                                             | 2   | _   | 12   | ns    | 3.3-V V <sub>DDD</sub> , C <sub>LOAD</sub> = 25 pF  |

| T <sub>FALLF</sub>   | Fall time in Fast-Strong mode                                             | 2   | _   | 12   | ns    | $3.3\text{-V V}_{DDD}$ , $C_{LOAD} = 25 \text{ pF}$ |

| T <sub>RISES</sub>   | Rise time in Slow-Strong mode                                             | 10  | _   | 60   | ns    | $3.3\text{-V V}_{DDD}$ , $C_{LOAD} = 25 \text{ pF}$ |

| T <sub>FALLS</sub>   | Fall time in Slow-Strong mode                                             | 10  | _   | 60   | ns    | $3.3\text{-V V}_{DDD}$ , $C_{LOAD} = 25 \text{ pF}$ |

| F <sub>GPIOUT1</sub> | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DD} \le 5.5 V$ Fast-Strong mode            | _   | -   | 33   | MHz   | 90/10%, 25 pF load, 60/40 duty<br>cycle             |

| F <sub>GPIOUT2</sub> | GPIO $F_{OUT}$ ; 1.7 $V \le V_{DD} \le 3.3 \text{ V}$<br>Fast-Strong mode | _   | -   | 16.7 | MHz   | 90/10%, 25 pF load, 60/40 duty cycle                |

| F <sub>GPIOUT3</sub> | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DD} \le 5.5 V$<br>Slow-Strong mode         | _   | -   | 7    | MHz   | 90/10%, 25 pF load, 60/40 duty<br>cycle             |

| F <sub>GPIOUT4</sub> | GPIO $F_{OUT}$ ; 1.7 $V \le V_{DD} \le 3.3 V$<br>Slow-Strong mode         | _   | _   | 3.5  | MHz   | 90/10%, 25 pF load, 60/40 duty<br>cycle             |

| F <sub>GPIOIN</sub>  | GPIO input operating frequency 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V | _   | _   | 48   | MHz   | 90/10% V <sub>IO</sub>                              |

## Table 13. OVT GPIO DC Specifications (P5\_0 and P5\_1 Only)

| Parameter       | Description                                                          | Min | Тур | Max | Units | Details/Conditions                                   |

|-----------------|----------------------------------------------------------------------|-----|-----|-----|-------|------------------------------------------------------|

| I <sub>IL</sub> | Input leakage (absolute value).<br>V <sub>IH</sub> > V <sub>DD</sub> | -   | -   | 10  | μA    | 25°C, V <sub>DD</sub> = 0 V, V <sub>IH</sub> = 3.0 V |

| $V_{OL}$        | Output voltage LOW level                                             | 1   | _   | 0.4 | V     | $I_{OL}$ = 20 mA, $V_{DD}$ > 2.9 V                   |

## Table 14. OVT GPIO AC Specifications (P5\_0 and P5\_1 Only)

| Parameter              | Description                                                     | Min | Тур | Max | Units | Details/Conditions                              |

|------------------------|-----------------------------------------------------------------|-----|-----|-----|-------|-------------------------------------------------|

| T <sub>RISE_OVFS</sub> | Output rise time in Fast-Strong mode                            | 1.5 | -   | 12  | ns    | 25-pF load, 10%–90%, V <sub>DD</sub> =3.3 V     |

| T <sub>FALL_OVFS</sub> | Output fall time in Fast-Strong mode                            | 1.5 | -   | 12  | ns    | 25-pF load, 10%–90%, V <sub>DD</sub> =3.3 V     |

| T <sub>RISESS</sub>    | Output rise time in Slow-Strong mode                            | 10  | 1   | 60  | ns    | 25 pF load, 10%-90%,<br>V <sub>DD</sub> = 3.3 V |

| T <sub>FALLSS</sub>    | Output fall time in Slow-Strong mode                            | 10  | 1   | 60  | ns    | 25 pF load, 10%-90%,<br>V <sub>DD</sub> = 3.3 V |

| F <sub>GPIOUT1</sub>   | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DD} \le 5.5 V$ Fast-Strong mode  | _   | 1   | 24  | MHz   | 90/10%, 25 pF load, 60/40 duty cycle            |

| F <sub>GPIOUT2</sub>   | GPIO $F_{OUT}$ ; 1.71 $V \le V_{DD} \le 3.3 V$ Fast-Strong mode | -   | 1   | 16  | MHz   | 90/10%, 25 pF load, 60/40 duty cycle            |

## **XRES**

## Table 15. XRES DC Specifications

| Parameter            | Description                                                          | Min                  | Тур | Max                  | Units | Details/Conditions |

|----------------------|----------------------------------------------------------------------|----------------------|-----|----------------------|-------|--------------------|

| V <sub>IH</sub>      | Input voltage HIGH threshold                                         | $0.7 \times V_{DDD}$ | _   | _                    | V     | CMOS input         |

| $V_{IL}$             | Input voltage LOW threshold                                          | _                    | _   | $0.3 \times V_{DDD}$ | V     | CMOS input         |

| R <sub>PULLUP</sub>  | Pull-up resistor                                                     | 3.5                  | 5.6 | 8.5                  | kΩ    | -                  |

| C <sub>IN</sub>      | Input capacitance                                                    | _                    | 3   | _                    | pF    | -                  |

| V <sub>HYSXRES</sub> | Input voltage hysteresis                                             | _                    | 100 | _                    | mV    | _                  |

| I <sub>DIODE</sub>   | Current through protection diode to V <sub>DD</sub> /V <sub>SS</sub> | _                    | _   | 100                  | μΑ    | -                  |

#### Table 16. XRES AC Specifications

| Parameter               | Description       | Min | Тур | Max | Units | Details/Conditions |

|-------------------------|-------------------|-----|-----|-----|-------|--------------------|

| T <sub>RESETWIDTH</sub> | Reset pulse width | 1   | _   | -   | μs    | -                  |

## Temperature Sensor

#### **Table 17. Temperature Sensor Specifications**

| Parameter            | Description                 | Min | Тур | Max | Units | Details/Conditions |

|----------------------|-----------------------------|-----|-----|-----|-------|--------------------|

| T <sub>SENSACC</sub> | Temperature-sensor accuracy | -5  | ±1  | 5   | °C    | –40 to +85 °C      |

#### SAR ADC

## Table 18. SAR ADC DC Specifications

| Parameter | Description                        | Min             | Тур | Max       | Units | Details/Conditions                             |

|-----------|------------------------------------|-----------------|-----|-----------|-------|------------------------------------------------|

| A_RES     | Resolution                         | -               | -   | 12        | bits  |                                                |

| A_CHNIS_S | Number of channels - single-ended  | -               | _   | 8         |       | 8 full-speed <sup>[8]</sup>                    |

| A-CHNKS_D | Number of channels - differential  | _               | _   | 4         |       | Diff inputs use neighboring I/O <sup>[8]</sup> |

| A-MONO    | Monotonicity                       | -               | -   | -         |       | Yes                                            |

| A_GAINERR | Gain error                         | -               | _   | ±0.1      | %     | With external reference                        |

| A_OFFSET  | Input offset voltage               | -               | _   | 2         | mV    | Measured with 1-V V <sub>REF</sub>             |

| A_ISAR    | Current consumption                | _               | _   | 1         | mA    |                                                |

| A_VINS    | Input voltage range - single-ended | V <sub>SS</sub> | _   | $V_{DDA}$ | V     |                                                |

| A_VIND    | Input voltage range - differential | V <sub>SS</sub> | _   | $V_{DDA}$ | V     |                                                |

| A_INRES   | Input resistance                   | _               | _   | 2.2       | kΩ    |                                                |

| A_INCAP   | Input capacitance                  | -               | _   | 10        | pF    |                                                |

| VREFSAR   | Trimmed internal reference to SAR  | -1              | _   | 1         | %     | Percentage of Vbg (1.024 V)                    |

#### Note

<sup>8.</sup> A maximum of eight single-ended ADC Channels can be accomplished only if the AMUX Buses are not being used for other functionality (e.g. CapSense). If the AMUX Buses are being used for other functions, then the maximum number of single-ended ADC channels is six. Similarly, if the AMUX Buses are being used for other functionality, then the maximum number of differential ADC channels is three.

Table 19. SAR ADC AC Specifications

| Parameter  | Description                                                            | Min        | Тур | Max      | Units | Details/Conditions                        |

|------------|------------------------------------------------------------------------|------------|-----|----------|-------|-------------------------------------------|

| A_PSRR     | Power-supply rejection ratio                                           | 70         | _   | _        | dB    | Measured at 1-V reference                 |

| A_CMRR     | Common-mode rejection ratio                                            | 66         | _   | _        | dB    |                                           |

| A_SAMP     | Sample rate                                                            | _          | _   | 1        | Msps  |                                           |

| Fsarintref | SAR operating speed without external ref. bypass                       | _          | -   | 100      | ksps  | 12-bit resolution                         |

| A_SNR      | Signal-to-noise ratio (SNR)                                            | 65         | _   | _        | dB    | F <sub>IN</sub> = 10 kHz                  |

| A_BW       | Input bandwidth without aliasing                                       | _          | _   | A_SAMP/2 | kHz   |                                           |

| A_INL      | Integral nonlinearity. V <sub>DD</sub> = 1.71 V to 5.5 V, 1 Msps       | -1.7       | -   | 2        | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

| A_INL      | Integral nonlinearity. V <sub>DDD</sub> = 1.71 V to 3.6 V, 1 Msps      | -1.5       | -   | 1.7      | LSB   | $V_{REF}$ = 1.71 V to $V_{DD}$            |

| A_INL      | Integral nonlinearity. V <sub>DD</sub> = 1.71 V to 5.5 V, 500 ksps     | -1.5       | -   | 1.7      | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

| A_dnl      | Differential nonlinearity. V <sub>DD</sub> = 1.71 V to 5.5 V, 1 Msps   | <b>–</b> 1 | -   | 2.2      | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

| A_DNL      | Differential nonlinearity. V <sub>DD</sub> = 1.71 V to 3.6 V, 1 Msps   | <b>–1</b>  | -   | 2        | LSB   | $V_{REF}$ = 1.71 V to $V_{DD}$            |

| A_DNL      | Differential nonlinearity. V <sub>DD</sub> = 1.71 V to 5.5 V, 500 ksps | <b>–</b> 1 | -   | 2.2      | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

| A_THD      | Total harmonic distortion                                              | _          | -   | -65      | dB    | F <sub>IN</sub> = 10 kHz                  |

## CSD

# **CSD Block Specifications**

| Parameter              | Description                                    | Min  | Тур | Max | Units | Details/Conditions                                                                             |

|------------------------|------------------------------------------------|------|-----|-----|-------|------------------------------------------------------------------------------------------------|

| V <sub>CSD</sub>       | Voltage range of operation                     | 1.71 | -   | 5.5 | V     |                                                                                                |

| IDAC1                  | DNL for 8-bit resolution                       | -1   | -   | 1   | LSB   |                                                                                                |

| IDAC1                  | INL for 8-bit resolution                       | -3   | _   | 3   | LSB   |                                                                                                |

| IDAC2                  | DNL for 7-bit resolution                       | -1   | _   | 1   | LSB   |                                                                                                |

| IDAC2                  | INL for 7-bit resolution                       | -3   | _   | 3   | LSB   |                                                                                                |

| SNR                    | Ratio of counts of finger to noise             | 5    | -   | _   | Ratio | Capacitance range of 9 pF to 35 pF, 0.1-pF sensitivity. Radio is not operating during the scan |

| I <sub>DAC1_CRT1</sub> | Output current of IDAC1 (8 bits) in High range | _    | 612 | _   | μA    |                                                                                                |

| I <sub>DAC1_CRT2</sub> | Output current of IDAC1 (8 bits) in Low range  | _    | 306 | _   | μA    |                                                                                                |

| I <sub>DAC2_CRT1</sub> | Output current of IDAC2 (7 bits) in High range | _    | 305 | _   | μA    |                                                                                                |

| I <sub>DAC2_CRT2</sub> | Output current of IDAC2 (7 bits) in Low range  | _    | 153 | _   | μA    |                                                                                                |

## **Digital Peripherals**

Timer

## Table 20. Timer DC Specifications

| Parameter         | Description                         | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>TIM1</sub> | Block current consumption at 3 MHz  | _   | _   | 42  | μA    | 16-bit timer       |

| I <sub>TIM2</sub> | Block current consumption at 12 MHz | -   | _   | 130 | μA    | 16-bit timer       |

| I <sub>TIM3</sub> | Block current consumption at 48 MHz | _   | _   | 535 | μA    | 16-bit timer       |

## **Table 21. Timer AC Specifications**

| Parameter               | Description                    | Min                  | Тур | Max | Units | Details/Conditions |

|-------------------------|--------------------------------|----------------------|-----|-----|-------|--------------------|

| T <sub>TIMFREQ</sub>    | Operating frequency            | F <sub>CLK</sub>     | _   | 48  | MHz   |                    |

| T <sub>CAPWINT</sub>    | Capture pulse width (internal) | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>CAPWEXT</sub>    | Capture pulse width (external) | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>TIMRES</sub>     | Timer resolution               | T <sub>CLK</sub>     | _   | _   | ns    |                    |

| T <sub>TENWIDINT</sub>  | Enable pulse width (internal)  | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>TENWIDEXT</sub>  | Enable pulse width (external)  | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>TIMRESWINT</sub> | Reset pulse width (internal)   | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>TIMRESEXT</sub>  | Reset pulse width (external)   | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

#### Counter

## Table 22. Counter DC Specifications

| Parameter         | Description                         | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>CTR1</sub> | Block current consumption at 3 MHz  | =   | _   | 42  | μA    | 16-bit counter     |

| I <sub>CTR2</sub> | Block current consumption at 12 MHz | _   | _   | 130 | μA    | 16-bit counter     |

| I <sub>CTR3</sub> | Block current consumption at 48 MHz | _   | _   | 535 | μA    | 16-bit counter     |

## Table 23. Counter AC Specifications

| Parameter               | Description                    | Min                  | Тур | Max | Units | Details/Conditions |

|-------------------------|--------------------------------|----------------------|-----|-----|-------|--------------------|

| T <sub>CTRFREQ</sub>    | Operating frequency            | F <sub>CLK</sub>     | _   | 48  | MHz   |                    |

| T <sub>CTRPWINT</sub>   | Capture pulse width (internal) | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>CTRPWEXT</sub>   | Capture pulse width (external) | 2 × T <sub>CLK</sub> | _   | -   | ns    |                    |

| T <sub>CTRES</sub>      | Counter Resolution             | T <sub>CLK</sub>     | _   | -   | ns    |                    |

| T <sub>CENWIDINT</sub>  | Enable pulse width (internal)  | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>CENWIDEXT</sub>  | Enable pulse width (external)  | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>CTRRESWINT</sub> | Reset pulse width (internal)   | 2 × T <sub>CLK</sub> | _   | -   | ns    |                    |

| T <sub>CTRRESWEXT</sub> | Reset pulse width (external)   | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

## Pulse Width Modulation (PWM)

## Table 24. PWM DC Specifications

| Parameter         | Description                         | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>PWM1</sub> | Block current consumption at 3 MHz  | _   | -   | 42  | μA    | 16-bit PWM         |

| I <sub>PWM2</sub> | Block current consumption at 12 MHz | _   | _   | 130 | μΑ    | 16-bit PWM         |

| I <sub>PWM3</sub> | Block current consumption at 48 MHz | -   | _   | 535 | μA    | 16-bit PWM         |

## Table 25. PWM AC Specifications

| Parameter               | Description                   | Min                  | Тур | Max | Units | Details/Conditions |

|-------------------------|-------------------------------|----------------------|-----|-----|-------|--------------------|

| T <sub>PWMFREQ</sub>    | Operating frequency           | F <sub>CLK</sub>     | _   | 48  | MHz   |                    |

| T <sub>PWMPWINT</sub>   | Pulse width (internal)        | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMEXT</sub>     | Pulse width (external)        | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMKILLINT</sub> | Kill pulse width (internal)   | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMKILLEXT</sub> | Kill pulse width (external)   | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMEINT</sub>    | Enable pulse width (internal) | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMENEXT</sub>   | Enable pulse width (external) | 2 × T <sub>CLK</sub> | -   | -   | ns    |                    |

| T <sub>PWMRESWINT</sub> | Reset pulse width (internal)  | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

| T <sub>PWMRESWEXT</sub> | Reset pulse width (external)  | 2 × T <sub>CLK</sub> | _   | _   | ns    |                    |

#### LCD Direct Drive

## Table 26. LCD Direct Drive DC Specifications

| Parameter             | Description                                            | Min | Тур  | Max  | Units | Details/Conditions                    |

|-----------------------|--------------------------------------------------------|-----|------|------|-------|---------------------------------------|

| I <sub>LCDLOW</sub>   | Operating current in low-power mode                    | -   | 17.5 | _    | μA    | 16 × 4 small segment display at 50 Hz |

| C <sub>LCDCAP</sub>   | LCD capacitance per segment/common driver              | -   | 500  | 5000 | pF    |                                       |

| LCD <sub>OFFSET</sub> | Long-term segment offset                               | _   | 20   | _    | mV    |                                       |

| I <sub>LCDOP1</sub>   | LCD system operating current V <sub>BIAS</sub> = 5 V   | _   | 2    | _    | mA    | 32 × 4 segments. 50 Hz<br>at 25 °C    |

| I <sub>LCDOP2</sub>   | LCD system operating current V <sub>BIAS</sub> = 3.3 V | _   | 2    | _    | mA    | 32 × 4 segments<br>50 Hz at 25 °C     |

## Table 27. LCD Direct Drive AC Specifications

| Parameter        | Description    | Min | Тур | Max | Units | Details/Conditions |

|------------------|----------------|-----|-----|-----|-------|--------------------|

| F <sub>LCD</sub> | LCD frame rate | 10  | 50  | 150 | Hz    |                    |

#### **Serial Communication**

## Table 28. Fixed I<sup>2</sup>C DC Specifications

| Parameter         | Description                                 | Min | Тур | Max | Units | Details/Conditions |

|-------------------|---------------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>I2C1</sub> | Block current consumption at 100 kHz        | _   | -   | 50  | μΑ    | _                  |

| I <sub>I2C2</sub> | Block current consumption at 400 kHz        | _   | -   | 155 | μΑ    | _                  |

| I <sub>I2C3</sub> | Block current consumption at 1 Mbps         | _   | _   | 390 | μΑ    | -                  |

| I <sub>I2C4</sub> | I <sup>2</sup> C enabled in Deep-Sleep mode | _   | _   | 1.4 | μΑ    | _                  |

## Table 29. Fixed I<sup>2</sup>C AC Specifications

| Parameter         | Description | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------|-----|-----|-----|-------|--------------------|

| F <sub>I2C1</sub> | Bit rate    | 1   | _   | 400 | kHz   |                    |

## Table 30. Fixed UART DC Specifications

| Parameter          | Description                            | Min | Тур | Max | Units | Details/Conditions |

|--------------------|----------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>UART1</sub> | Block current consumption at 100 kbps  | _   | -   | 55  | μΑ    | _                  |

| I <sub>UART2</sub> | Block current consumption at 1000 kbps | 1   | 1   | 312 | μΑ    | _                  |

## Table 31. Fixed UART AC Specifications

| Parameter         | Description | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------|-----|-----|-----|-------|--------------------|

| F <sub>UART</sub> | Bit rate    | _   | 1   | 1   | Mbps  | -                  |

## Table 32. Fixed SPI DC Specifications

| Parameter         | Description                         | Min | Тур | Max | Units | Details/Conditions |

|-------------------|-------------------------------------|-----|-----|-----|-------|--------------------|

| I <sub>SPI1</sub> | Block current consumption at 1 Mbps | -   | 1   | 360 | μΑ    | _                  |

| I <sub>SPI2</sub> | Block current consumption at 4 Mbps | _   | -   | 560 | μΑ    | _                  |

| I <sub>SPI3</sub> | Block current consumption at 8 Mbps | _   | _   | 600 | μA    | -                  |

## Table 33. Fixed SPI AC Specifications

| Parameter        | Description                                        | Min | Тур | Max | Units | Details/Conditions |

|------------------|----------------------------------------------------|-----|-----|-----|-------|--------------------|

| F <sub>SPI</sub> | SPI operating frequency (master; 6x over sampling) | _   | 1   | 8   | MHz   | -                  |

Document Number: 002-12597 Rev. \*F Page 22 of 38

#### Table 34. Fixed SPI Master Mode AC Specifications

| Parameter        | Description                                                               | Min | Тур | Max | Units | Details/Conditions               |

|------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|----------------------------------|

| $T_{DMO}$        | MOSI valid after SCLK driving edge                                        | _   | _   | 18  | ns    | _                                |

|                  | MISO valid before SCLK capturing edge Full clock, late MISO sampling used | 20  | -   | -   | ns    | Full clock, late MISO sampling   |

| T <sub>HMO</sub> | Previous MOSI data hold time                                              | 0   | _   | _   | ns    | Referred to Slave capturing edge |

## Table 35. Fixed SPI Slave Mode AC Specifications

| Parameter            | Description                                                                        | Min | Тур | Max                       | Units | Details/Conditions |

|----------------------|------------------------------------------------------------------------------------|-----|-----|---------------------------|-------|--------------------|

| T <sub>DMI</sub>     | MOSI valid before SCLK capturing edge                                              | 40  | _   | _                         | ns    |                    |

| T <sub>DSO</sub>     | MISO valid after SCLK driving edge                                                 | -   | -   | 42+3×<br>T <sub>CPU</sub> | ns    |                    |

| T <sub>DSO_ext</sub> | MISO Valid after SCLK driving edge in external clock mode. V <sub>DD</sub> < 3.0 V | _   | -   | 50                        | ns    |                    |

| T <sub>HSO</sub>     | Previous MISO data hold time                                                       | 0   | _   | _                         | ns    |                    |

| T <sub>SSELSCK</sub> | SSEL valid to first SCK valid edge                                                 | 100 | _   | _                         | ns    |                    |

## Memory

#### Table 36. Flash DC Specifications

| Parameter         | Description                        | Min  | Тур | Max | Units | Details/Conditions       |

|-------------------|------------------------------------|------|-----|-----|-------|--------------------------|

| V <sub>PE</sub>   | Erase and program voltage          | 1.71 | _   | 5.5 | V     | _                        |

| T <sub>WS48</sub> | Number of Wait states at 32–48 MHz | 2    | _   | _   |       | CPU execution from flash |

| T <sub>WS32</sub> | Number of Wait states at 16–32 MHz | 1    | _   | _   |       | CPU execution from flash |

| T <sub>WS16</sub> | Number of Wait states for 0–16 MHz | 0    | _   | _   |       | CPU execution from flash |

## Table 37. Flash AC Specifications

| Parameter                              | Description                                        | Min   | Тур | Max | Units   | Details/Conditions      |

|----------------------------------------|----------------------------------------------------|-------|-----|-----|---------|-------------------------|

|                                        | Row (block) write time (erase and program)         | 1     | -   | 20  | ms      | Row (block) = 256 bytes |

| NOWLINASL                              | Row erase time                                     | _     | _   | 13  | ms      | -                       |

| T <sub>ROWPROGRAM</sub> <sup>[9]</sup> | Row program time after erase                       | _     | _   | 7   | ms      | -                       |

|                                        | Bulk erase time (256 KB)                           | -     | _   | 35  | ms      | _                       |

| T <sub>DEVPROG</sub> <sup>[9]</sup>    | Total device program time                          | _     | _   | 25  | seconds | -                       |

| F <sub>END</sub>                       | Flash endurance                                    | 100 K | _   | _   | cycles  | -                       |